利用人工智能技术来加快芯片设计流程,是最近两、三年来在EDA工具业界相当热门的话题。特别是在布局绕线(P&R)与模拟(Simulation)阶段,人工智能技术已展现出相当大的应用潜力。

在此基础之上,美国国防部旗下的DARPA希望更进一步,利用人工智能实现全自动化的芯片设计(Push Button IC Design)。然而,这无疑是个相当远大的目标。通常DARPA发起的先进研究计划,都是十年磨一剑的专案,过程中失败的机率也不低,但倘若能做出成果,对产业的颠覆性却是不容小觑的。

从自驾车到全自动IC设计DARPA挑战科技极限

楷登电子(Cadence)资深副总裁暨客制化IC/PCB设计总经理Tom Beckley指出,DARPA所推动的研究,通常都是挑战当代科技极限的专案,其所举办的Grand Challenge竞赛就是其中之一。

Cadence资深副总裁Tom Beckley指出,全自动设计是DARPA对半导体产业提出的下一个Grand Challenge。

2004年的DARPA Grand Challenge就以自动驾驶技术为主题,举办了第一届自驾车挑战赛,要求参赛队伍用自动驾驶技术,完成从加州到内华达州,全程约150英里的赛事。结果第一届参赛者没有任何一支队伍跑完全程,即便是跑得最远的参赛队伍,也只跑了7英里。2005年这项赛事卷土重来,赛事路线稍有变动,但大多数队伍的表现都远比前一届更好,其中更有五支队伍跑完全程132英里。

为了参与这项竞赛所发展出来的技术,成为目前自驾车发展的基础,未来更可能彻底改变人类社会的交通运输。但从第一届Grand Challenge到现在已经过了十多年,自驾车距离全面上路,还是有一段不小的距离。这就是DARPA计划的特色--高度前瞻、高风险,但倘若能成功,将会对产业甚至整个社会造成颠覆性的变革。

拉回到半导体领域,DARPA这次对半导体产业提出的挑战,全名为电子复兴运动(Electronics Resurgence Initiative, ERI)。该计划广邀学术界、商用产业与军事产业中获选的成员共同参与,目的是将复杂又昂贵的SoC设计门槛压低。

在EDA工具的辅助下,很多芯片设计流程已经进入自动化时代,但由于制程技术不断进步,使得单一芯片得以整合更多功能,因此SoC设计变得越来越复杂,在SoC上执行的软件也是如此。因此,两相抵销之下,SoC设计的成本还是一飞冲天,而且开发团队的规模只增不减。这使得先进SoC的开发变成少数大型跨国公司的专利,而且只有少数市场规模够大的应用,才能吸引业者开发这种先进SoC。

这个趋势对小型芯片公司与美国国防部这种利基型客户是不利的。以国防应用来说,许多系统设备也需要使用先进SoC,但由于国防航太产业的需求规模不够大,因此开发费用很难摊提。

在ERI计划之下,又分成电子资产智慧设计(Intelligent Design of Electronic Assets, IDEA)跟Posh开放原始码硬件计划(Posh Open Source Hardware, POSH)两个子计划,各有其研究团队(表1)。

线路布局全面自动化

ERI的终极目标是创造出一个以软件为基础,完全自动化的实体线路布局产生器跟开放原始码硅智财(IP)生态系,能在24小时内完成一次设计循环,进而让客制化商用SoC跟符合国防部规格要求的军用SoC均能大量、快速产出。

为了达成这个目标,IDEA团队必须创造出一个无人介入(No Human In the Loop)的线路布局产生器,让垫子设计经验有限的团队也能在24小时内完成电子硬件的实体设计。IDEA团队的软件必须能自动生成可制造的电路设计档案,把以年为单位的设计周期缩短到一天之内。藉由导入机器学习,IDEA希望其为数位电路、混合讯号电路、系统级封装(SiP)与印刷电路板开发的线路布局产生器,能有更高的效能。

创造开放原始码硬件IP生态系统

至于在POSH方面,其主要任务则是产生大量经过验证的IP基本元素,借此减少混合讯号SoC研发所需投入的资源。透过从软件领域发展出来的开放原始码概念,POSH将创造出开放原始码的SoC设计生态系统,让高度复杂的SoC开发更具成本效益。虽然IP重复利用已经为IC设计带来相当显著的经济效益,但IP授权的商业模式限制了IP的重复利用。

要创造出可持续发展的开放原始码硬件生态系统,POSH团队必须发展出一系列验证技术,确保采用开放原始码设计的混合讯号SoC,其品质符合预期。同时POSH团队也必须发展出各种关键的开放原始码IP元件。

Beckley表示,由于Cadence是IDEA的一员,因此该公司未来的发展方向建立基于机器学习(ML)的平台,在该公司的Virtuoso、OrbitIO、Allegro等工具中导入机器学习演算法,实现布局、绕线与萃取的最佳化设计。

因应少子化趋势机器必须做更多

这是个非常宏大的计划,但同时也加深了人工智能跟人类抢饭碗的疑虑。因为全自动化的IC设计流程,势必会让众多IC设计工程师的工作不保。但Beckley并不认为情况会这么严重,因为要实现高品质的IC设计,人还是很关键的因素。先别说完全自动化的芯片设计流程在短时间内还很难实现,即便有朝一日DARPA ERI计划实现了,IC设计工程师还是会有忙不完的工作,因为SoC设计的复杂度只会一直上升。

Cadence全球副总裁暨亚太区总裁石丰瑜则进一步解释,在少子化的情况下,各行各业未来缺工的情况只会越来越严重,即便是高科技产业也不例外。中国大陆清华大学微电子所所长魏少军曾估计,光是中国的半导体产业,包含半导体制造跟IC设计,就有至少40万工程师人力缺口。

另一方面,婴儿潮时代结束,很多老一辈的半导体人都即将退休,未来缺工的情况只会越来越严重,更会有经验传承中断的危机。对客制化ASIC跟类比芯片来说,设计经验是非常重要的。如果现在不设法把老前辈的经验转移到以机器学习为基础的开发环境上,对IC设计来说,是相当不利的。此外,两岸的年轻人其实都不喜欢进入半导体产业工作。因此,让机器做更多事情,提高工程师的工作效率,是未来必然要走的路。

IC设计模拟/分析进入人工智能时代

除了线路布局工具开始导入机器学习之外,在布局完成后的模拟跟分析作业,也开始看到机器学习的应用实例,特别是采用先进制程、规模动辄数十亿个闸极的大型SoC,在设计模拟跟分析的过程中,采用机器学习的效益更加明显。

Ansys半导体事业部技术长张鸿嘉指出,对半导体产业来说,机器学习并非这两三年才突然窜起的议题。在GPU的效能越来越强,能够在合理的执行时间内跑完演算任务之后,就开始有业者试着在设计芯片的过程中采用机器学习方法。

Ansys半导体事业部技术长张鸿嘉认为,由于IC的设计复杂度越来越高,开发团队在某些特定环节将越来越依赖机器学习技术。

而随着制程变得更先进,单一芯片动辄内含数十亿到数百亿个电晶体后,因为整个架构变得太过复杂,业界很难再用传统方法来应对未来的工程挑战。不管是在线路布局或设计模拟,采用机器学习都是大势所趋。

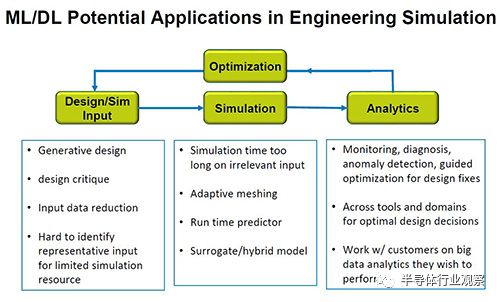

图3机器学习在工程领域的潜力应用。由这个图可以看出,在芯片开发过程中,机器学习可以发挥的环节相当多,从产生设计档案到执行设计模拟,乃至大数据分析等,都有机器学习可以发挥的地方。不过,机器学习终究是一项工具,使用者必须先厘清什么问题最适合用ML或深度学习(DL)来解决,后面才能逐步展开,进行训练资料搜集、发展模型等工作。其中,搜集训练资料是最耗时的工作,因为目前EDA工具仍使用监督式学习。

图3 机器学习在工程领域的潜力应用

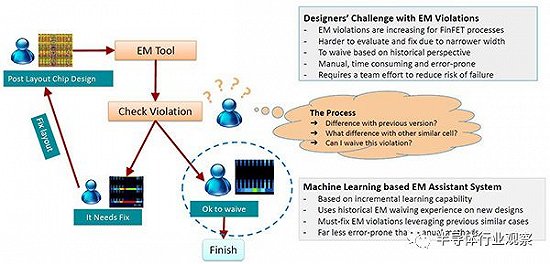

目前在芯片设计过程中,开发者最常遇到的问题,是由先进制程所带来的电子迁移(Electron Migration, EM)、时序(Timing)与功率(Power)问题。这些问题就很适合用机器学习的方法来解。Ansys已经跟NVIDIA合作发展出一套辅助工具,让已经完成线路布局的芯片设计,在模拟环境中进行分析,看芯片会不会遇到EM相关问题,以判断线路布局是否需要修改(图4) 。

图4 以机器学习为基础的EM辅助系统

传统上,当芯片开发团队完成线路布局后,是用工程团队所设定的条件去进行模拟,但因为模拟需要耗费相当长的时间,因此开发团队设定的模拟情境很难涵盖周延。但在ML的辅助之下,机器学习可以帮工程师注意到以前没关注的盲点,从而在芯片还在设计阶段就把可能出现的问题排除。

AI不是万能设计最佳化还得靠人脑

虽然用机器学习或人工智能来设计芯片将是未来趋势,而且有越来越多芯片设计开发的环节开始使用相关工具,但诚如张嘉鸿所言,机器学习只是众多工具中的一种,不是所有问题的万灵丹。因此,人在芯片设计的整个过程中,还是会扮演非常重要的角色,只是专注的工作跟现在不一样。

明导国际(Mentor Graphic)执行长Walden Rhines(图5)就表示,人工智能是许多学运算科学的人都研究过的题目,在他还是个年轻工程师的时候,就有参与过类似的开发专案。看到现在人工智能的蓬勃发展,一方面有终于熬到出头天的感慨,但另一方面还是得指出,神经网路(Neuro Network, NN)、机器学习这些人工智能技术,在应用上还是有其限制,不应该把AI神化。

明导国际执行长Walden Rhines认为,机器学习在EDA领域的应用还在发展中,而且有些IC设计步骤所遭遇的问题未必适合用机器学习来解决。

以IC设计为例,用机器学习来做芯片绕线布局,其实是非常「粗放」的。虽然用这种方法可以加快芯片设计的速度,但很难做到面积、功耗或性能的最佳化。这意味着以现有的技术条件,要完全靠机器学习设计出在商业市场上有竞争力的芯片,是有困难的。

对美国国防部这类单位或军事应用客户来说,ERI计划有其价值,因为该计划可让IC设计经验有限的团队快速开发出可用的芯片,而且军用市场其实对芯片的价格、功耗不是那么敏感。但如果是要应用在可携式装置、消费性电子这类应用的芯片,是不太可能接受的。

机器学习除了很难做到设计最佳化之外,在合成(Synthesis)这个步骤也不容易派上用场,或至少效益很有限。事实上,相对于机器学习,在合成阶段,IC设计团队有其他更好的选择,例如以C/C++或System C语言取代一部分VHDL或Verilog,就能明显提升开发效率。

告别PDF规格书AI协力打造元件资料库

除了IC设计用的EDA工具开始导入人工智能之外,还有另一个跟EDA有关,却较少被关注的领域,也就是元件资料库的建置。新创公司富比库(FootPrintKu)就看好这个需求,推出利用人工智能实现自动化元件资料库建置的云端解决方案。

富比库执行长黄以建表示,一般提到EDA,业内人士往往联想到IC设计,但其实除了IC设计之外,系统设计也需要用到EDA。但很吊诡的是,这两类EDA系统之间的资料串接,到现在都还是得靠人工把规格书PDF上的资料转成自己需要的资料库格式,没有自动化的衔接方案。

富比库执行长黄以建指出,电子零组件的规格资料至今都还依靠PDF来传递,透过人工智能将其转换成真正的数位资料,对电子产业可带来很大的帮助。

这个现象的成因,其实跟每家电子产品开发商自行定义的资料库格式不同有关。因为每家公司的命名规则、资料库栏目都不一样,IC或其他电子元件供应商除了给PDF规格书之外,让客户自己动手建资料库之外,似乎也没有其他更好的办法。但这绝对不是个好办法,因为人工建立资料库容易发生失误,而且命名规则不容易统一。

这是一定要做的工作,因为没有元件资料库,就等于没有元件的数位资料,没办法进入EDA做设计开发。但这种工作的附加价值不高,职涯发展空间也有限,若找专人来做,流动性是个大问题。因此,很多公司是让实习生或菜鸟工程师轮班处理这种苦差事。而这正是命名规则不统一,导致资料库难以检索的主要原因。

富比库就是从这个现象中看到机会,发展出一套以云端为基础的人工智能工具,使用者只要将PDF规格书上传到富比库的平台,提供系统必要的资料库格式资讯跟转换需求,富比库就会依照使用者需求将资料转换成所想要的资料库格式。

这个运作模式其实也带有共享经济的味道,因为系统只要做过一次,当其他使用者也需要同一款元件的规格资料时,系统可以很快就提供所需要的资料。当然,在某些情况下,如果某家厂商使用了客制化元件,并且不想让其他厂商查询到相关资料时,也可以选择不要共享该元件的资讯库。

黄以建希望,藉由推出这个云端服务,电子零组件供应商跟客户之间可以不用再依靠PDF档案来传递规格资料,因为这么做对简化产品开发工作并无太大帮助。下一步,富比库希望能将其资料库格式跟档案格式发展成业界标准,让电子零组件的规格资料得以实现数位化。

IC设计公司/工程师的挑战与机会

虽然EDA工具业者普遍认为人工智能有其极限跟适用的范围,不认为该技术能完全取代人类工程师在IC设计流程中的地位,但对IC设计业者跟个别从业人员来说,越来越自动化、智慧化的工具,还是会对产业生态跟个人的职涯造成影响。

首先,随着越来越多IC设计步骤可以用自动化技术来执行,IC设计业者在价值链中所要扮演的角色势必要跟着调整。以往IC设计公司还有IC设计的技术可以卖,但未来IC设计的技术价值,会有一部分转移到EDA工具跟IP供应商手中。

有台系IC设计业者A公司的内部员工就透露,由于A公司的营收大致持平,营运规模近几年也没有明显增加,因此公司花在IP授权跟EDA工具授权的费用没有明显成长,但就其观察,公司内的芯片设计团队对EDA工具仰赖日深,导致该公司的芯片面积很明显就是比另一家台厂B公司的同类产品来得大。

有趣的是,台厂B公司的内部员工指出,其公司向来奉行「终结者」策略--从不求产品快速上市,但只要一推出产品,其成本结构一定要是业内最佳。而对该公司的IC设计团队来说,这就意味工程师得在许多芯片设计的细节上琢磨,不能太仰赖EDA工具做出来的结果。当然,面对越来越复杂的SoC设计,完全不用EDA工具已经是不可能的任务。

某种程度上,这两家台湾IC设计公司的状况,正好呼应了Rhines所说的,设计出芯片不难,但设计最佳化的关键还是在人身上。如果开发团队的最佳化功力够扎实,公司策略又不求产品上市速度领先业界,给研发团队足够的时间,以市场终结者的定位自居,也是一种生意经营的策略。

但反过来说,如果公司策略是要追求技术跟产品上市时程领先,除了靠EDA工具跟机器学习来抢时效之外,必然要有其他牢牢掌握在自己手中的核心价值。这个价值是什么呢?钰创董事长卢超群的观点或值得参考。

卢超群认为,未来的IC设计公司对自己专攻的领域,必须要有更高的掌握度。除了要累积领域知识(Domain Know-how)之外,也要对客户的应用、甚至客户的客户应用,有比现在更深的理解。唯有如此,开出来的产品才能准确命中客户需求,甚至跟客户更深度结合,变成虚拟IDM价值链中的一分子。

而对个别IC设计工程师来说,如果要一直走设计研发这条路,为因应越来越强大的人工智能,除了在本职学能上不断强化基本功之外,最好也要开始学习如何驾驭人工智能,让人工智能帮自己处理杂务,省下来的心力跟时间则用来思考SoC系统架构这类更宏观的问题,朝系统架构师的方向发展,才能帮自己创造出不被机器取代的价值。

人工智能重新形塑半导体产业未来

许多半导体业内人士一听到人工智能、深度学习等词汇,就会立刻联想到各种技术应用跟随之而来的商机。但就本质而言,人工智能其实是一种做事的方法论--对历史资料进行统计分析,据此预估未来并做出决策。

也因为人工智能是做事的方法论,因此,随着软件工具内建的人工智能越来越强大,日常作业越来越依赖人工智能,企业组织内部的文化若没有跟着调整,可能会导致大大小小的文化冲突发生。

半导体产业向来走在科技的最前沿,因此恐怕也是第一个遭遇这种文化冲击的产业。有些半导体制造企业已经与人工智能共舞多年,摸索出一套作法,但对IC设计来说,如何把人工智能整合到日常作业流程,恐怕还是门需要花时间研究的功课。

/3

/3