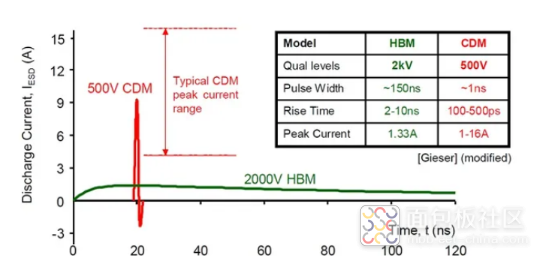

CDM(Charged Device Model)作为一种独特的ESD(Electrostatic Discharge)模拟方式,与HBM(Human Body Model)和MM(Machine Model)有所区别。此模型专注于模拟电子设备在生产或物流环节中积累的静电,在接触地面或其他导电物体时引发的快速电荷释放现象。CDM放电事件的特点是极其迅速的电流上升阶段,通常在0.1至0.5纳秒之间,整个放电过程大约持续6至8纳秒,其电流峰值相较于HBM模型在相同ESD条件下可达到数倍之高。

CDM模型对于电子元件的重要性,以及其与其他放电模型的区别。我们提供专业的ESD测试服务,包括针对CDM模型的测试,以确保电子元件在面临静电放电时的可靠性和稳定性。通过我们的测试和评估,客户可以更好地了解其产品在实际应用中可能遇到的挑战,并采取相应的措施来保护其设备免受ESD损害。

CDM测试装置

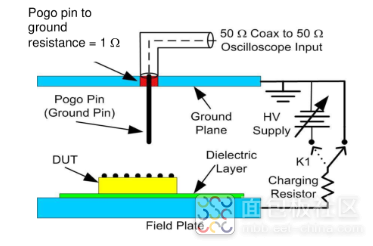

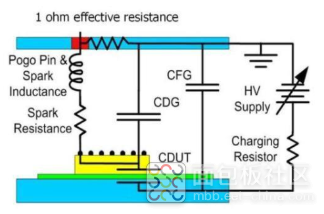

CDM测试装置主要由一个与高压电源相连的充电板Field Plate和一个接地的Pogo pin构成,Pogo pin能够在待测IC(DUT)的引脚间移动,以模拟实际的ESD事件。图1展示了实际的测试模块,而图2则为等效电路图,其中CDUT代表DUT与场板之间的电容,CDG代表DUT与地平面之间的电容,CFG代表场板与地平面之间的电容。

图1:实际测试各模块

图2:等效电路

(CDUT是DUT和场板间的电容,CDG是DUT和地平面间的电容,CFG是场板和地平面间电容。)

CDM测试规范

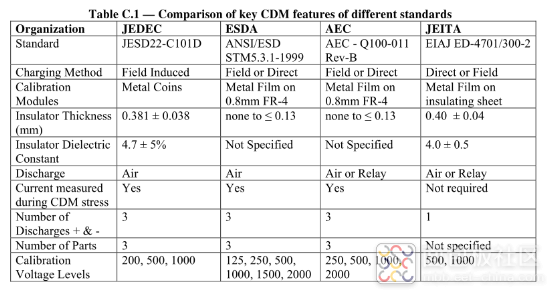

在CDM测试规范统一化之前,存在多个参考标准,包括JESD22-C101、ESDA S5.3.1、AEC Q100-011和EIAJ ED-4701/300-2等,这些标准在校准平台、示波器带宽和波形验证参数等方面存在差异。

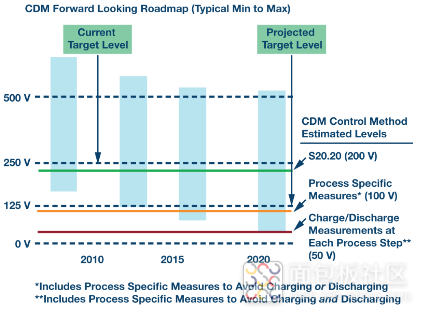

技术进步带来了晶体管性能的提升和更高的IO性能需求。随着IC芯片对高速IO的需求增加,以及在单一封装中集成更多功能的趋势,封装尺寸的增加对维持JEP157中推荐的CDM放电级别提出了挑战。考虑到不同测试设备的充电电阻差异,ESD协会(ESDA)在2020年的路线图中建议可能需要重新评估CDM放电目标级别。

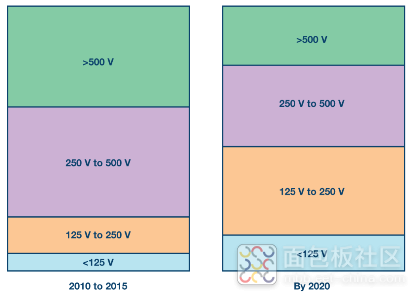

随着电子设备性能的提高,对ESD保护的需求也在增加,ESD测试服务,帮助客户评估其产品在静电放电环境下的表现,并根据最新的标准和建议提供定制化的解决方案。通过金鉴的测试服务,客户能够更准确地掌握产品的ESD性能,确保产品在实际使用中的可靠性和稳定性。如图3和图4所示,分别展示了历年CDM放电目标级别的变化和CDM ESD目标级别的预期分布变化。

图3:历年来CDM放电的目标级别

图4:CDM ESD目标级别的分布预期的变化

CDM测试标准调整的原因

使我们能够为客户提供专业的建议和解决方案,帮助他们在面对新标准时,及时调整产品设计和测试策略。JEP157标准中对CDM放电能力要求的降低反映了几个关键因素:

1. IC元件引脚数量和封装尺寸的显著增加

在固定的预充电压下,限制了芯片的CDM放电能力,尤其是封装尺寸。引脚数量和封装尺寸的增加意味着IC能够存储更多的电荷,导致CDM放电时峰值电流迅速上升。因此,在相同的峰值电流限制下,引脚数量和尺寸的增加会导致CDM能力的降低。

2. IC工艺技术的进步导致CDM放电能力的降低

随着工艺尺寸的缩小,CDM放电能力显著降低。工艺尺寸的缩小使得有源器件变得更小、更脆弱,金属互连变得更薄、电阻性增加,降低了ESD保护电路的鲁棒性。这使得在相同的电流水平下,实现CDM保护变得更加困难。

3. 随着高速数字、射频模拟和其他性能敏感引脚的混合信号IC变得更加普遍,对ESD保护提出了新的要求

在高频电路中,直接将ESD保护器件连接到I/O引脚可能会导致射频功能的显著降低,因此需要将射频保护结构与核心电路隔离。这通常通过在ESD保护器件和引脚之间插入并联电感/电容网络来实现,该网络在低频ESD事件中提供接近零的阻抗,在正常高频操作中提供高阻抗。

/4

/4