验证方法简介

设计验证是用于证明设计正确性的过程,要求和规格。

在数字设计流程中,验证可确保芯片按照设计意图正确运行,然后再将设计送去制造。

具体来说,验证方法是验证集成电路设计的标准化方法。

验证方法定义了创建的模型、它们的使用方式以及工具用于操作它们的方式。模型可以在多个抽象层次上定义设计,它们可以定义设计的要求,也可以定义闭合标准。

验证方法也是一种系统的做事方式,具有一套丰富的标准规则和指南。验证方法提供了构建稳健、可靠和完整的验证环境的方法。验证方法通过其预定义的库减少了验证工作。

验证方法进一步提供了一个框架,用于简化覆盖驱动的约束随机验证环境的实现。

验证方法也提高了可移植性。一致性和可移植性使第三方供应商解决方案的采用变得容易。第三方BFM(总线功能模型)的使用就是这样一个例子。

验证方法的主要目的是优化设计的某些方面,同时尽量减少花在设计上的时间。它还确保了公司内部的一致性,从而使重用成为可能。验证方法的主要目标是使采用最知名的验证实践更容易。根据该方法构建的验证环境提供了构建验证环境的一致性。验证方法将验证环境架构限制为某些标准模式。此限制在正确使用时允许一致性和标准化。

在第一个专用 HVL(硬件验证语言)出现后不久,验证方法就应运而生。采用方法论(如 UVM)的主要优点是

• 通过测试台重用和验证 IP 实现即插即用的可重用性

• 一种行之有效的方法,具有行业广泛的支持和具有现有知识和/或经验的工程师的可用性

• 模拟器和供应商独立性

验证方法的历史

验证方法基本上是一组基类库,我们可以使用它来构建我们的测试平台。验证方法本身不会进行任何功能验证。这只是一个推动者。

设计验证占设计总开发工作量的 40% 到 70%。

可供选择的验证技术种类繁多,大致可分为四类:基于仿真的技术、静态技术、形式化技术以及物理验证和分析。为了实现所需的验证目标,必须结合使用这些方法。

多年来,多家公司已经使用不同的语言发布了许多不同的方法。在这篇文章中,我们根据它们在今天的流行度列出了一些关键方法。

Accellera(开源)的通用验证方法(UVM)(SystemVerilog)

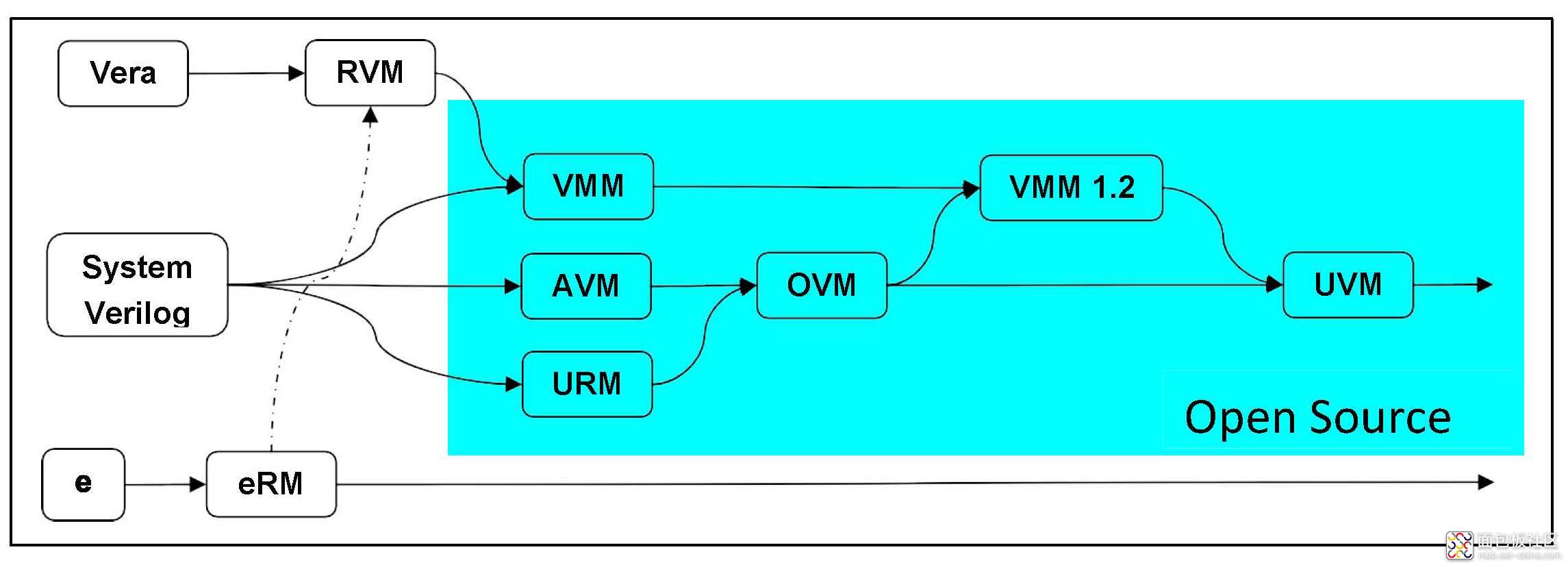

通用验证方法 (UVM) 是一种用于验证集成电路设计的标准化方法。 UVM 主要源自 OVM(OpenVerification Methodology),它在很大程度上是基于 Verisity Design 在 2001 年开发的用于 e 验证语言的eRM(e Reuse Methodology)。UVM 类库为SystemVerilog 语言,如序列和数据自动化功能(打包、复制、比较)等,与之前由模拟器供应商独立开发的方法不同,它是一个 Accellera 标准,得到了多个供应商的支持:Aldec、Cadence、Mentor Graphics、Synopsys、赛灵思模拟器 (XSIM)。资料来源:https://en.wikipedia.org/wiki/Universal_Verification_Methodology

Cadence Design Systems 和 Mentor Graphics 的开放式验证方法 (OVM)(SystemVerilog/ SystemC)

被UVM取代

开放验证方法 (OVM) 是第一个真正开放、可互操作且经过验证的验证方法。 OVM 是一个开源 SystemVerilog 类库和方法,它定义了可重用验证 IP (VIP) 和测试的框架。它是 100% IEEE 1800SystemVerilog,并提供构建块(对象)和一组通用的验证相关实用程序。 OVM 版本将采用 Apache 2.0 许可,任何人都可以将 OVM 库用于任何目的,包括创建衍生作品。

OVM 由 Cadence 和 Mentor Graphics 联合开发,以促进真正的 SystemVerilog 与标准库和经过验证的方法的互操作性。它完全开放,结合了 Cadence® Incisive® Plan-to-Closure Universal Reuse Methodology(URM) 和 Mentor Advanced Verification Methodology (AVM) 的优点,可用于全球三分之二的 SystemVerilog 系统。 OVM 还将促进以 SystemVerilog、SystemC® 和 e 语言编写的即插即用验证 IP (VIP) 的开发和使用。

2009 年 12 月,Accellera 选择 OVM 作为新兴的通用验证方法 (UVM) 的基础。 UVM 的第一个版本于 2010 年 5 月发布,基于 OVM2.1.1,其中“ovm_”名称由脚本转换为“uvm_”,并对回调和测试结束进行了一些小的更改,但是不是核心方法论或基类。

资料来源:https://www.cadence.com/en_US/home/alliances/standards-and-languages/open-verification-methodology.html

Aldec/Synthworks 的开源 VHDL 验证方法 (OSVVM)

OSVVM 是一种智能测试平台方法,允许将“智能覆盖”与定向、算法、基于文件和受约束的随机方法混合。 OSVVM 是一个专门用于验证 VHDL 的集成环境。 OSVVM 代表“开源 VHDL 验证方法”。 OSVVM 是一组 VHDL 包,最初由 Aldec 和 Synthworks 开发。 OSVVM 帮助您采用使用 VHDL 的现代约束随机验证技术。使用 OSVVM,可以将高级验证方法添加到他们当前的测试平台中,而无需学习一门新语言或抛弃现有的测试平台模型。 OSVVM 支持与基于其他验证方法的功能相同的功能。这包括事务级别建模、约束随机测试生成、功能覆盖、消息过滤、记分板和 FIFO、错误报告等。

来源:https://www.aldec.com/en/support/resources/documentation/articles/1902

通用 VHDL 验证方法 -Bitvis 的 UVM For VHDL (UVVM)

UVVM(通用 VHDL 验证方法)是一种免费的开源方法和库,用于非常有效地对 FPGA 和 ASIC 进行 VHDL验证 - 还可以显着提高质量。

UVVM(通用 VHDL 验证方法)是增长最快的 FPGA 验证方法——独立于语言。这是由于在 FPGA 质量和开发时间上提高了 UVVM 良率。这个开源库和方法具有最广泛的 VHDL 验证支持,让您以非常有效的方式验证真正复杂的 DUT,提供类似于 UVM 的模块化、可重用性、受约束的随机激励和功能覆盖。 UVVM 还拥有最大的开源 VHDL 验证模型和组件库。超过 50% 的 FPGA 设计人员使用 VHDL,UVVM为这些用户提供了出色的验证解决方案。

Synopsys 的验证方法手册(VMM) (SystemVerilog)

验证方法手册 (VMM) 是第一个成功且广泛实施的实践,用于在 SystemVerilog 中创建可重用验证环境。 VMM 由 SystemVerilog 的大力支持者之一 Synopsys 创建,利用诸如面向对象编程、随机化、约束、功能覆盖等语言特性,使新手和专家都能够创建强大的验证环境。 VMM 的贡献是创建 UVM 的一个重要因素。

Synopsys 的参考验证方法(RVM) (Open Vera)

参考验证方法 (RVM) 是一套完整的指标和方法,用于对复杂设计进行功能验证,例如针对特定应用的集成电路或其他半导体器件。它由 Synopsys 于 2003 年出版。

RVM 在 OpenVera 下实现。

RVM 的 SystemVerilog实现称为 VMM(验证方法手册)。它包含一个小型基类库。

Mentor Graphics 的高级验证方法 (AVM)(System C 和SystemVerilog)

被 OVM 和 UVM 取代

AVM 是用SystemVerilog 编写并由 Mentor Graphics 于 2006 年创建的验证方法和基类库,它是 OVM 和 UVM 的前身。它为组件层次结构和 TLM 通信提供了一个框架,为 SystemVerilog 验证环境提供了标准化的使用模型。不建议将 AVM 用于新项目,请参阅通用验证方法 (UVM)。

Verisity Design 的 e 重用方法 (eRM)(e 硬件验证语言)

被 OVM 和 UVM 取代

eRM Cadence Design Systems 为 SystemVerilog + Mentor Graphics 的 AVM 提供的 URM(通用重用方法) OVM(开放验证方法) UVM(通用验证方法)

e 重用方法 (eRM) 是硬件验证语言空间中出现的第一个重用方法,并与 e 硬件验证语言结合使用。它由 Verisity Design 于 2001 年发明并于 2002 年发布。该方法由以下主题的方法指南组成:

文件命名约定

测试平台的功能划分

代码打包指南

序列和消息类库

eRM 形成了由 CadenceDesign Systems 为 SystemVerilog 语言开发的 URM(通用重用方法)的基础。 URM 连同 Mentor Graphics 的 AVM 的贡献,后来成为 OVM(开放验证方法),最后成为今天的 UVM(通用验证方法)。

AgileSoC 的SVUNIT (Verilog/SystemVerilog)

SVUnit 是一个开源测试框架,供ASIC 和 FPGA 开发人员编写Verilog/SystemVerilog 代码。 SVUnit 是自动化的、快速的、轻量级的且易于使用,使其成为现有的唯一适合追求高质量代码和低错误率的设计和验证工程师的 SystemVerilog 测试框架。

用于验证工程师的 SVUnit

在用于子系统或芯片/产品级测试平台之前,验证工程师可以使用 SVUnit 单独验证测试平台组件。因为 SVUnit 对开发人员的限制很少,它可以用于为简单的基于 Verilog 的测试平台(用于定向测试)、复杂的基于 SystemVerilog 的约束随机测试平台以及介于两者之间的任何东西开发组件。 SVUnit 还支持开发基于 UVM 的验证测试平台和 IP。

SVUnit 设计工程师

验证工程师和整个 EDA 行业都未能提供对设计人员友好的 RTL 测试选项。 SVUnit 通过为设计工程师提供易于使用的实用框架来改变一切;它可以完成他们需要做的事情,而没有其他行业测试框架的不必要的开销和包袱。 SVUnit 为设计工程师提供了一个平台,用于在发布给验证团队之前进行详尽的独立测试和/或单元测试关键逻辑,同时避免维护临时测试平台所需的大量开销。结果是更高质量的 RTL 和整体减少的调试时间。

VUNIT (VHDL/SystemVerilog)

VUnit 是一个用于VHDL/SystemVerilog 的开源单元测试框架。它具有实现 HDL 代码连续和自动化测试所需的功能。 VUnit 并没有取代而是补充了传统的测试方法,它通过早期支持测试并且经常通过自动化来实现。

VUnit 通过支持自动发现测试平台和编译顺序以及包含用于常见验证任务的库来减少测试开销。它通过支持增量编译和将大型测试平台拆分为更小的独立测试来提高开发速度。它通过使大型回归套件能够在持续集成服务器上运行来提高项目的质量。

VUnit 不会对其用户强加任何特定的验证方法。当首先或最后编写测试,编写长时间运行的顶级测试或短期运行的单元测试,使用定向或约束随机测试时,可以享受 VUnit 的好处。通常,项目会针对不同的测试需求采用多种方法。 VUnit 已用于生产环境中,其中数千个测试需要几个小时才能在强大的多核机器上运行,也用于小型开源项目中,在几秒钟内只测试一个小包。

COCOTB(基于COroutine的COsimulation TestBench)

COCOTB 是一个基于COroutine 的 COsimulation TestBench 环境,用于使用 Python 验证 VHDL 和SystemVerilog RTL。

COCOTB 是一个基于CO-routine 的 CO-simulation Testbench 环境,用于使用 Python 验证 VHDL/Verilog RTL。它是一个开源环境,托管在 Github 上。 COCOTB 可以使用 Riviera-PRO 模拟器来模拟 RTL。它基本上有助于测试过程并使其舒适,特别是对于不太熟悉 HDL 验证概念的人。它使用与 UVM 相同的设计重用和功能验证概念,但使用 Python 实现。 VHDL、Verilog和 System Verilog 等硬件描述语言仅用于可综合设计。 COCOTB 还具有与 Jenkins 持续集成系统集成的内置支持。

COCOTB 需要一个模拟器来模拟HDL 设计,并已与 Linux、Windows 和 macOS 上的各种模拟器一起使用。

/3

/3