门电路分为:分立元件门电路和集成门电路。集成门电路又分为:集成TTL门电路和集成MOS门电路。

构成门电路的主要元器件:是各种半导体元件器,如二极管、三极管和场效应管。且它们均工作在开、关状态,用以实现门电路输出高、低两种电平。因此称其为“电子开关”。理想情况下,开关状态的转换是瞬间完成的,但实际中这种理想开关是不存在的。

1、半导体器件的开关特性

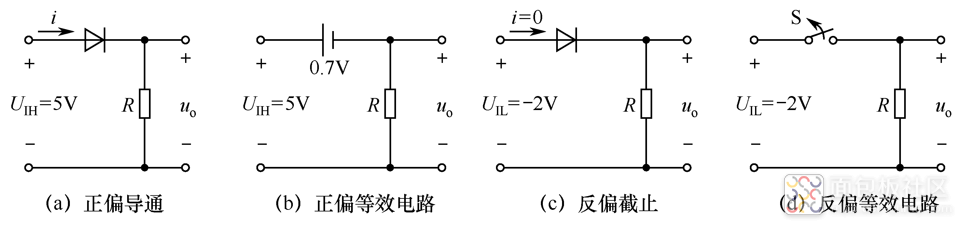

(1)二极管正偏时导通, 等效成0.7 V的电压源,其等效电路如下图(a)所示。(注意:理想情况下,二极管正偏时可看成短路,相当于开关闭合)。

(2)二极管反偏时截止,此时二极管相当于开关断开,其等效电路如下图(d)所示。

2、半导体三极管的开关特性

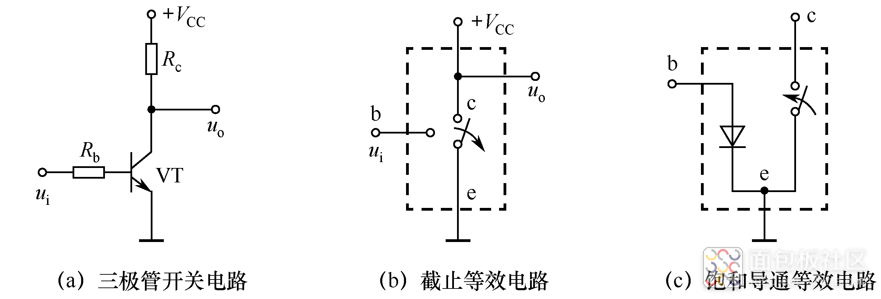

(1)当工作在截止状态时,发射结反偏,集电结也反偏,此时c-e间相当于开关断开。三极管截止时的等效电路如下图(a)所示,三个电极如同断开的开关。

(2)当工作在饱和状态时,发射结正偏偏,集电结也正偏,三极管c-e间相当于一个闭合开关。 等效电路如下图(b)所示。

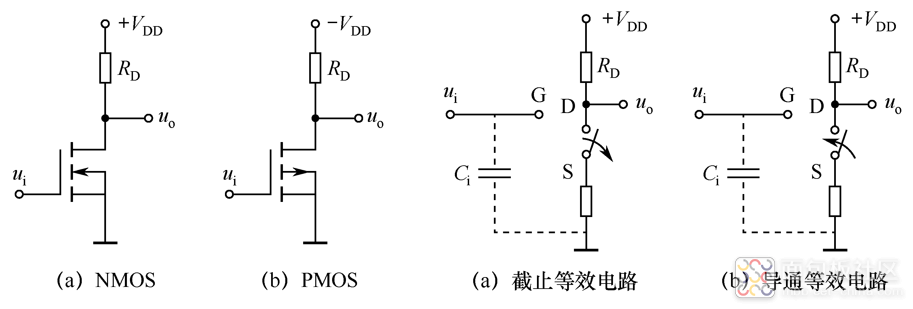

3、MOS管的开关特性

4、分立元件门电路

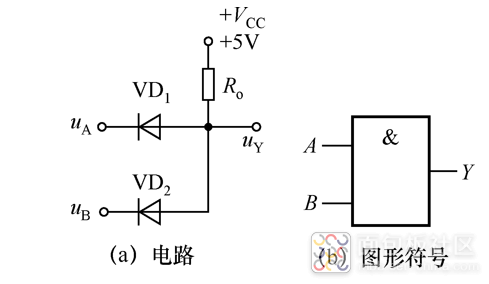

二极管与门:

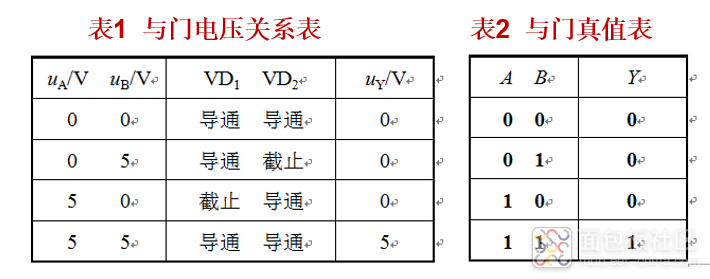

与门是实现与逻辑功能的电路,它有多个输入端和一个输出端。由二极管构成的与门电路如图(a)所示,uA、uB为输入电压信号,uY为输出电压信号;图(b)为与门的逻辑符号,其中A、B为输入变量,Y为输出变量。

二极管或门:

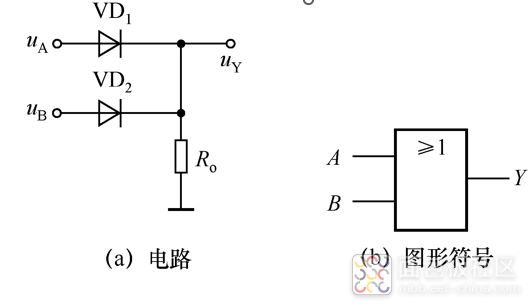

或门是实现或逻辑功能的电路,它也有多个输入端和一个输出端。由二极管构成的或门电路如图(a)所示,uA、uB为输入电压信号,uY为输出电压信号,其输入信号的高、低电平仍取5V和0V,图(b)所示为或门的逻辑符号。

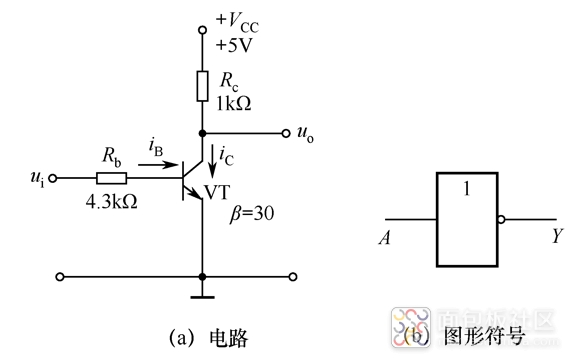

三极管非门(反相器):

实现非逻辑功能的电路是非门电路,也称反相器。利用三极管的开关特性,可以实现非逻辑运算。

5、集成门电路

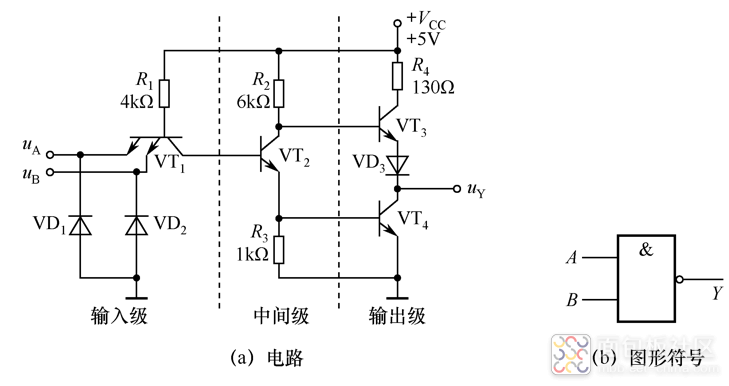

TTL与非门:

工作原理:

在图(a)中,若输入端中至少有一个是低电平0 V,则T1管基极电位uB1 = 0.7 V,这0.7 V电压不能使T1集电结、T2发射结、T4发射结三个PN结导通,所以T2、T4截止。此时,VCC通过R2使T3导通,uo = VCC -IB3R2 - uBE3 - uD3 ≈ VCC - uBE3 - uD3 ≈ 5-0.7-0.7 = 3.6V,输出为高电平UOH。

当输入信号A、B均为高电平3 V时,T1基极电位升高,足以使T1集电结、T2发射结、T4发射结三个PN结导通,三个PN结一旦导通,T1基极电位即被钳位于2.1V。T1的发射结反偏,集电结正偏,处于倒置工作状态,T1失去电流放大作用。三极管T2、T4导通后,进入饱和区,uo =UCES4 = 0.3 V,输出为低电平UOL。

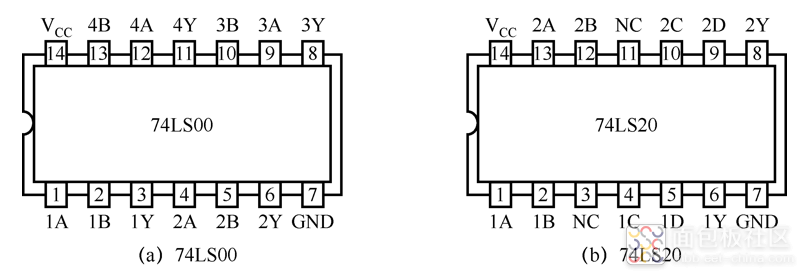

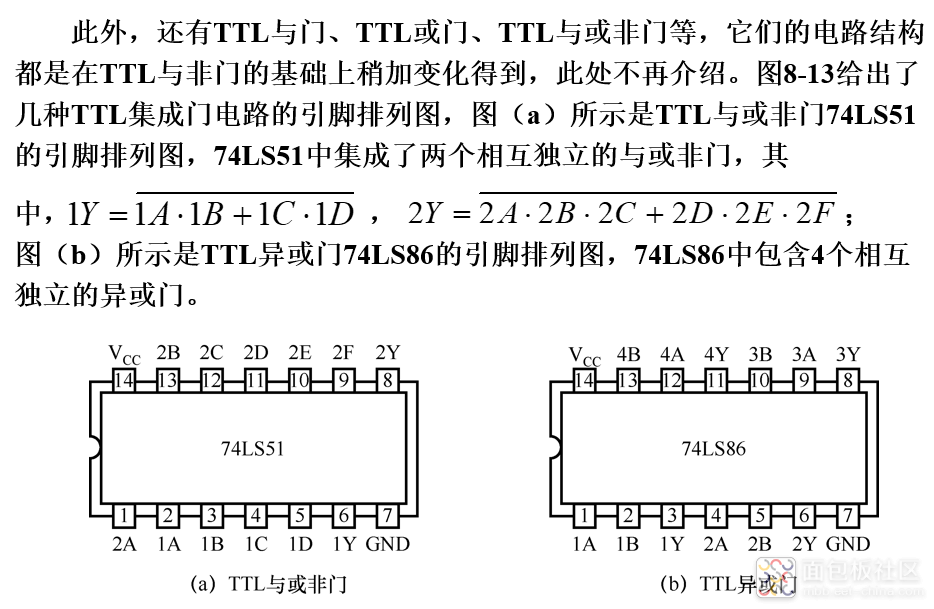

由此可见,只要输入端有一个为低电平,则输出高电平;只有输入端全为高电平时,才输出低电平。所以图(a)实现的是与非逻辑关系。下图所示是两种TTL集成与非门74LS00和74LS20的引脚排列图。74LS00内部集成了四个完全相同的2输入与非门,故简称为四-2输入与非门;74LS20为二-4输入与非门。

主要技术参数:

(1)输入、输出的高低电平

输入和输出高、低电平的数值为:

输出高电UOH = 3.6 V

输出低电平 UOL = UCES = 0.2 V

输入低电平 UiL = 0.4 V

输入高电平 UiH = 1.2 V

这些电平值是一种较理想的情况。对于TTL门电路(如74系列)来说,高、低电平的标准电压值为:UOL = 0.4 V,UOH = 2.4 V,Ui L = 0.8 V,Ui H = 2 V。

(2)噪声容限

实际的门电路都有一定的抗干扰能力。所谓抗干扰能力是指:电路在干扰信号的作用下,维持原来逻辑状态的能力。把在保证电路输出逻辑值不变(或者说uo变化范围不超过允许限度)的条件下,输入电平的允许波动范围称为输入端噪声容限。

在实际的数字系统中,往往前一级电路的输出就是后一级电路的输入。若设前级输出高电平的最小值为UOHmin,后级输入高电平的最小值为UIHmin,则它们的差值称为高电平噪声容限,用UNH表示,即

UNH = UOHmin – UiHmin

若设前级输出低电平的最大值为UOLmax,后级输入低电平的最大值为UiLmax,则它们的差值称为低电平噪声容限,用UNL表示,即

UNL = UILmax - UOLmax

(3)扇入、扇出系数

① TTL门电路的扇入系数取决于它的输入端的个数,例如一个3输入的与非门,其扇入系数Ni = 3。

② 扇出系数的情况则稍复杂。由于实际应用中,门电路输出端一般总接有一个或几个门。承受前级门输出信号的后级门称为前级门的负载门;带动负载门的前级门称为驱动门。驱动门输出的电流称为驱动电流;流经驱动门又流经负载门的电流称为负载电流。

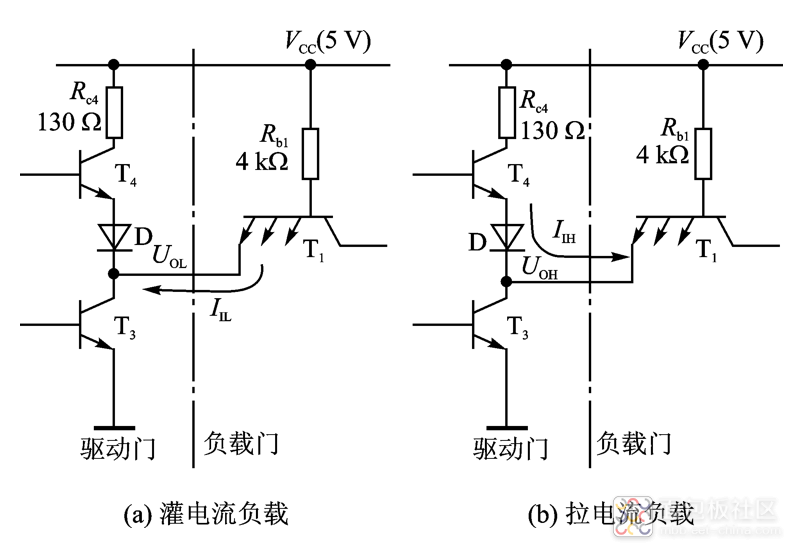

负载电流又有两种情况,一种是负载门电流灌入驱动门输出端,这种负载叫做灌电流负载,如图(a)所示,此时,驱动门输出为低电平UOL,为了保证输出UOL不高于规定值(0.4 V),要求负载门的个数不能无限制地增加。在输出为低电平的情况下,所能驱动同类门的个数由下式决定 :

另一种情况是,负载门电流是从驱动级中拉出来的,这种负载叫拉电流负载,如图(b)所示,此时,驱动门输出为高电平UOH,同样,输出高电平UOH也不能低于规定值(2.4V)。这样,输出为高电平时的扇出系数为

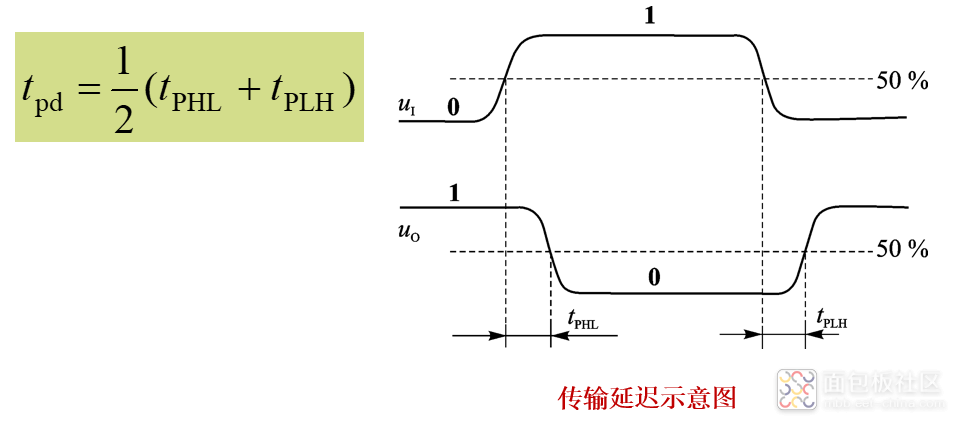

(4)传输延迟时间

传输延迟时间是表征门电路开关速度的参数。由于门电路中的二极管、三极管在状态转换过程中都需要一定的时间,且电路中有寄生电容的影响,因此,门电路从接收信号到输出响应会有一定的延迟。下图示意画出了与非门输入、输出的对应波形。平均延迟时间tpd为:

6. 集成TTL非门、或非门、集电极开路门和三态门

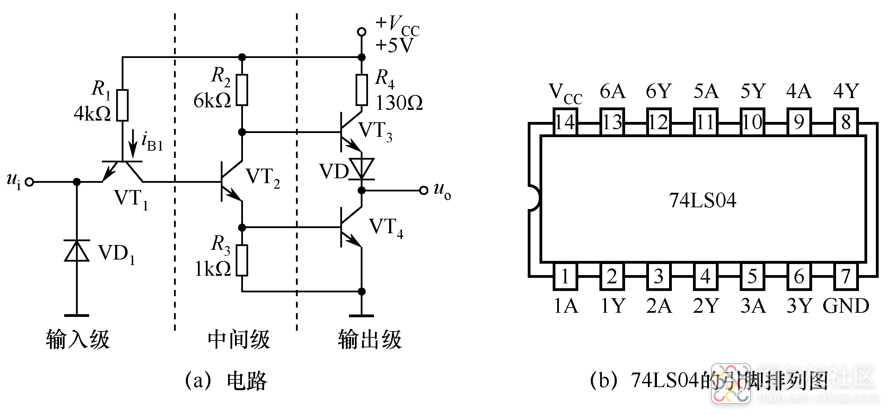

(1)TTL非门(反相器)

电阻组成:图(a)是TTL非门的基本电路,除了输入级T1由多发射极三极管改为单发射极三极管外,其余部分和图与非门完全一样。图(b)所示为集成反相器74LS04的引脚排列图,74LS04中包含6个相互独立的反相器。

工作原理:当输入电压ui = UiL= 0 V时,T1基极电流iB1流入发射极,即由非门输入端流出,因此iB2 = 0,T2截止,显然T4基极也没有电流,也截止。而T3和D将导通,uo = UOH =3.6 V,输出为高电平。当输入电压ui = UiH =3.6 V时,T1倒置,iB1流入T2基极,使T2饱和导通,进而使T4饱和导通,而T3和D将截止,uo = UOL ≤0.3V,输出为低电平。于是,电路实现了非逻辑关系。

(2)TTL或非门电阻组成:图(a)所示是TTL或非门的电路图,R1、T1、R1/、T1/构成输入级;T2、T2/ 和R2、R3构成中间级;R4、T3、D、T4构成输出级。图(b)所示为集成TTL或非门74LS02的引脚排列图,74LS02中包含4个相互独立的或非门。

工作原理:当输入信号A、B中只要有一个为高电平,例如A端ui =UiH = 3.6 V,那么iB1就会经过T1集电结流入T2基极,使T2、T4饱和导通,使得输出uo = UOL ≤0.3 V,为低电平。只有当输入信号A、B全为低电平时,iB1、i/B1均分别流入T1、T1/发射极,T2、T2/均截止,T4也截止,T3、D导通,输出为高电平。即电路实现的是或非逻辑功能。

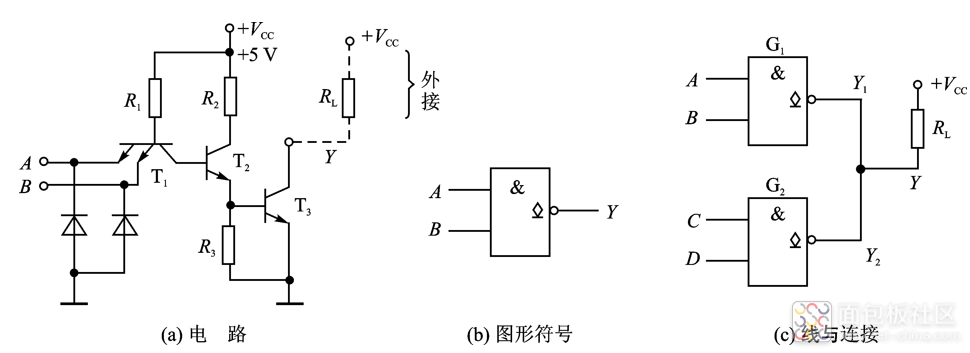

(3)集电极开路门(OC门)

线与:在工程实践中,往往需要将两个或多个逻辑门的输出端并联,以实现与逻辑的功能,称为线与。

然而,前面介绍的TTL门电路,其输出端不允许并联使用,也就无法实现线与功能。这是因为,对于一般的TTL门电路(以TTL与非门为例),若将两个(或多个)与非门的输出端直接相连,与非门G1与G2输出端并联起来,当G1门输出高电平,G2门输出低电平时,G1门的T3导通,G2门的T4/ 导通,将产生较大的电流io从G1门流经G2门,然后流入参考点。该电流值将远远超出器件的额定值,很容易将器件损坏。

为了解决这一问题,可以采用集电极开路门(OC门)。OC门的输出端可以直接相连,实现线与。

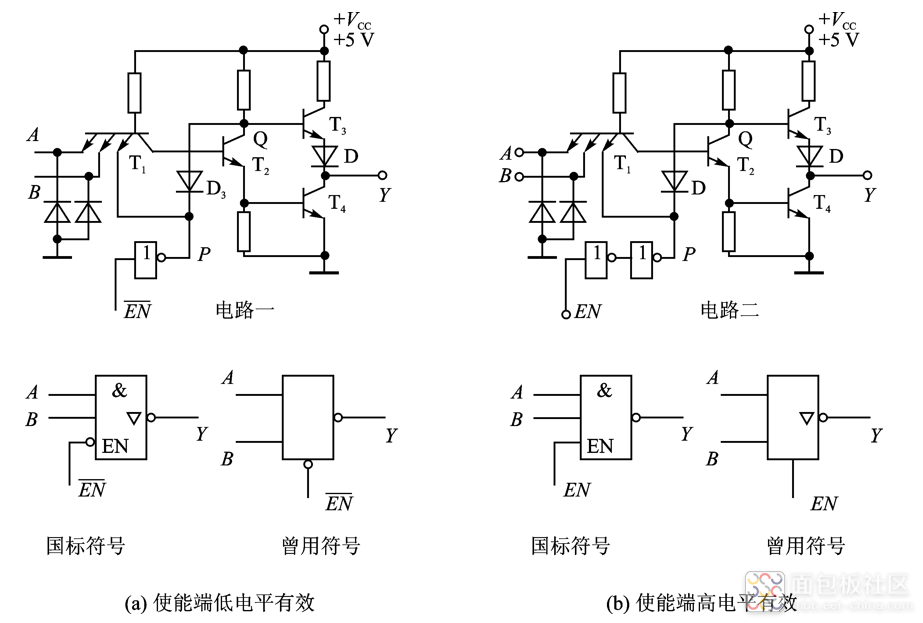

(4)三态门(TSL门)

三态:基本的TTL门电路,其输出有两种状态:高电平和低电平。无论哪种输出,门电路的直流输出电阻都很小,都是低阻输出。TTL三态门又称TSL门(Three State Logic),它有三种输出状态,分别是:高电平、低电平和高阻态(禁止态)。其中,在高阻状态下,输出端相当于开路。三态门是在普通门的基础上,加上使能控制信号和控制电路构成的。

图(a)所示是使能端EN低电平有效的三态与非门的电路图及逻辑符号,“EN低电平有效”是指当使能控制端信号EN为低电平时,电路才实现与非逻辑功能,输出高电平及低电平,而当EN为高电平时,输出为高阻无效状态。图(b)是使能端EN高电平有效的三态与非门的电路图及逻辑符号,其EN的有效电平与图(a)正好相反。

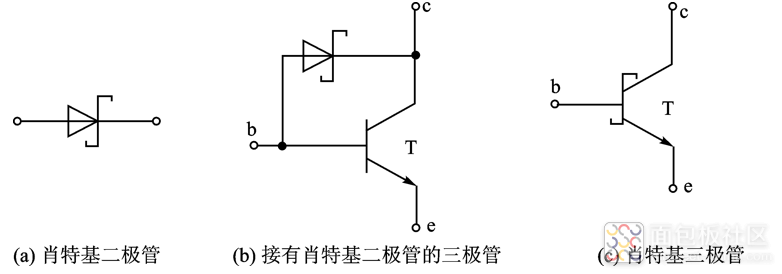

(5)改进型TTL门电路——抗饱和TTL门电路

三极管的开关时间限制了TTL电路的开关速度。肖特基二极管也称快速恢复二极管,它的导通电压较低,为0.4V~0.5V,因此开关速度极短,可实现1ns以下的高速度,其图形符号如图(a)所示。为了提高TTL电路的开关速度,人们在三极管的基极和集电极间跨接肖特基二极管,以缩短三极管的开关时间,其图形符号如图(b)所示。加接了肖特基二极管的三极管称为肖特基三极管,其图形符号如图(c)所示。由肖特基三极管组成的门电路称为肖特基TTL电路,即STTL门,它的传输延迟时间在10ns以内。除典型的肖特基型(STTL型)外,还有低功耗肖特基型(LSTTL)、先进的肖特基型(ASTTL)、先进的低功耗型(ALSTTL)等,它们的技术参数各有特点,是在TTL工艺的发展过程中逐步形成的。

7、CMOS集成门电路

特点:集成MOS电路是数字集成电路的一个重要系列,它具有低功耗、抗干扰性强、制造工艺简单、易于大规模集成等优点,因此得到广泛应用。

CMOS门电路:MOS集成电路有N沟道MOS管构成的NMOS集成电路、P沟道MOS管构成的PMOS集成电路、以及N沟道MOS管和P沟道MOS管共同组成的CMOS集成电路。CMOS是“互补金属-氧化物-半导体”(complementary metal oxide semiconductor)的英文缩写。由于CMOS电路中巧妙地利用了N沟道增强型MOS管和P沟道增强型MOS管特性的互补性,因而不仅电路结构简单,而且在电气特性上也有突出的优点。正因为如此,CMOS电路的制作工艺在数字集成电路中得到了广泛应用。

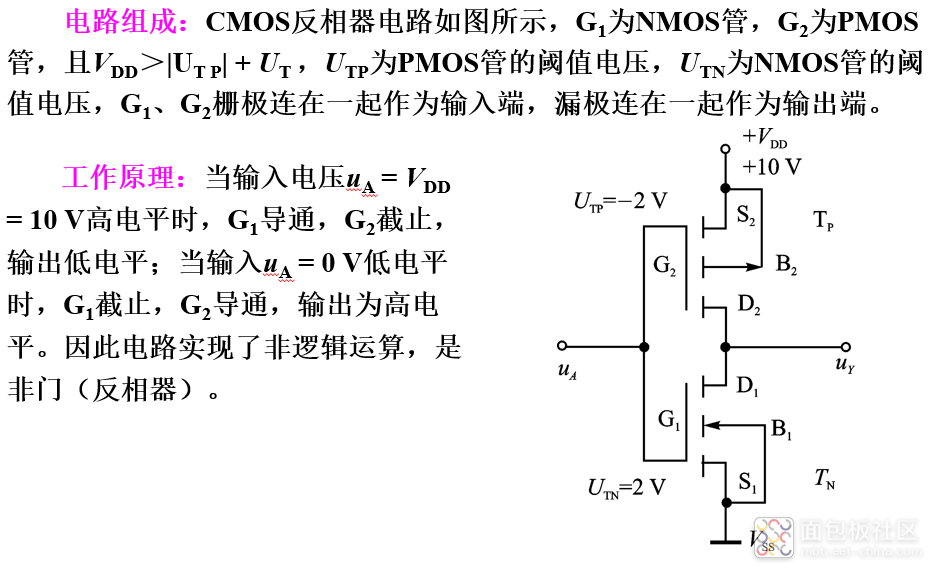

(1)CMOS反相器

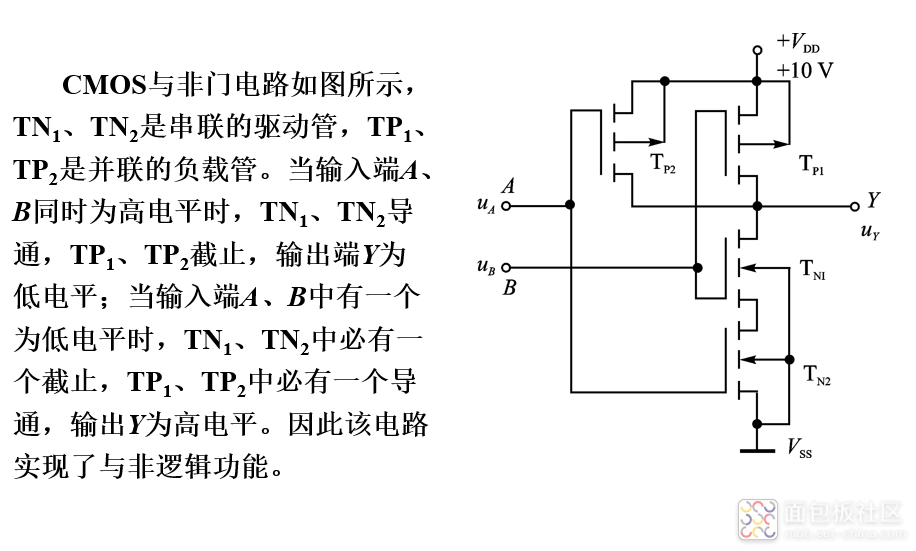

(2) CMOS与非门

/5

/5