本文简单介绍了晶体管结构从Planar FET向MBCFET演变。

芯片制程从微米级进入2纳米时代,晶体管架构经历了从Planar FET到MBCFET的四次关键演变。这不仅仅是形状的变化,更是一次次对物理极限的挑战。从平面晶体管到MBCFET,每一次架构演进到底解决了哪些物理瓶颈呢?

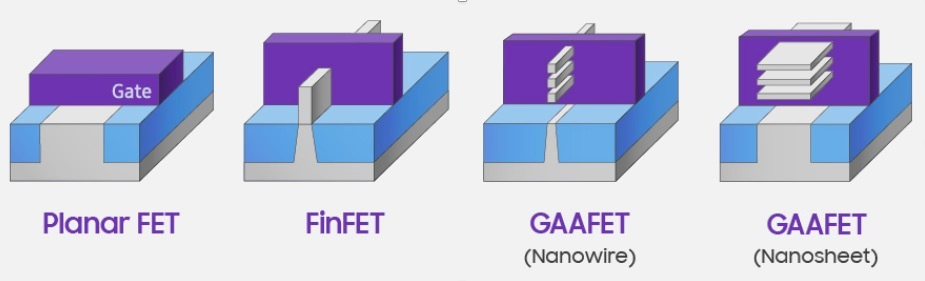

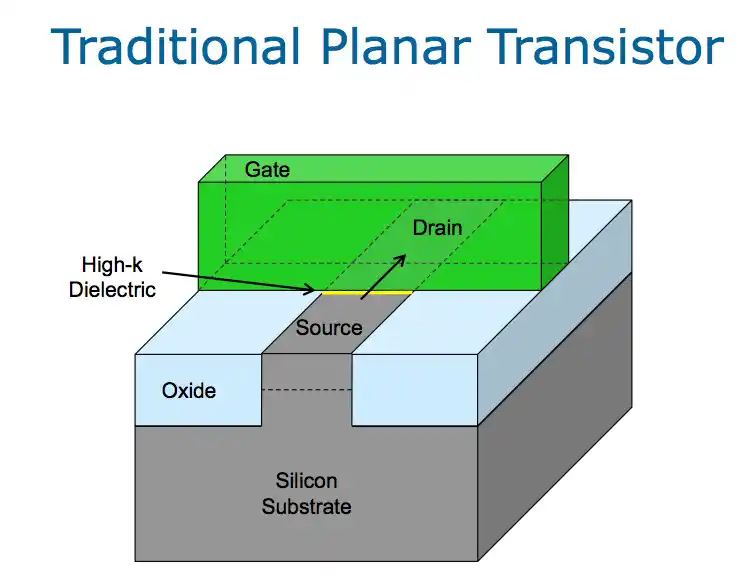

最初的Planar FET是二维平面的结构,也叫平面场效应晶体管。它的结构很简单:电子沟道是“趴在”硅片表面上的,而栅极则覆盖在沟道上方,整个电流的流动,是在晶圆表面上水平进行的。

这种设计在上世纪60年代诞生,并迅速成为主流。它构成了第一代大规模集成电路的基础,在90纳米以上的工艺节点上,表现非常出色,制造也非常成熟。但问题出现在制程继续微缩之后。尤其是到了28纳米以下,短沟道效应开始加剧,栅极对沟道的控制力越来越弱,晶体管就像“关不干净的水龙头”,漏电流不断上升。结果就是:功耗变高、发热增加、性能瓶颈越来越严重。

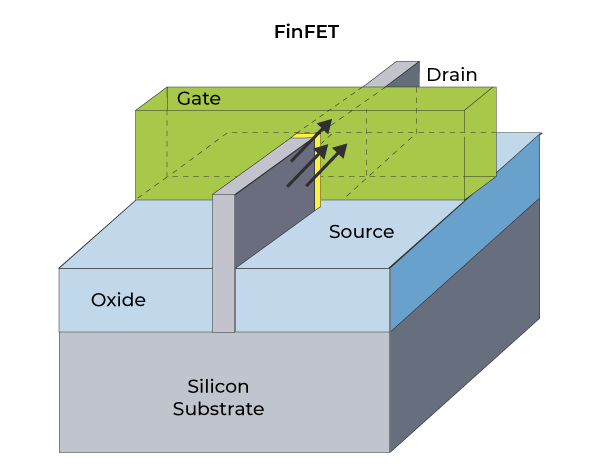

于是,在2011年,Intel率先推出了下一代晶体管结构——FinFET,也叫鳍式场效应晶体管。其结构看起来像鱼的鳍,因此得名FinFET。

你可以把它想象成:把原本“平躺在地上”的电子通道,竖起来变成一根鳍片,栅极不再只是覆盖在上方,而是从两侧甚至三面包裹住沟道。

这种三维结构,使用鳍状的3D结构来增加接触面积,极大地增强了栅极对电子的控制能力。结果就是:漏电少了,功耗降了,晶体管还能继续缩小,摩尔定律得以延续。

但FinFET也不是没有局限。随着制程逼近5纳米,它也遇到瓶颈。最关键的一点是——鳍片宽度是固定的,无法灵活调整。而当我们试图把鳍片做得更细、更小以适配更先进的制程时,制造难度却急剧上升,良率、可靠性、一致性都开始受到挑战。换句话说,FinFET的“鳍”已经变得太细、太脆,难以承受未来纳米级微缩带来的复杂性。

于是,GAAFET就在这种背景下应运而生。和FinFET最大的区别是,GAAFET把沟道变成了极细的纳米线,然后让栅极从四面——上、下、左、右把它完整包裹起来。这样一来,栅极对电流的控制能力更强,几乎做到了360度无死角的电场掌控。这使得晶体管在更小尺寸下也能稳稳“关掉”,极大降低了漏电流,非常适合5纳米以下的制程节点。

不过,GAAFET的“纳米线”虽然控制好,但也太细了,电流通过能力弱,不利于高性能芯片的电流驱动,限制了它在一些高频或高负载场景下的表现。

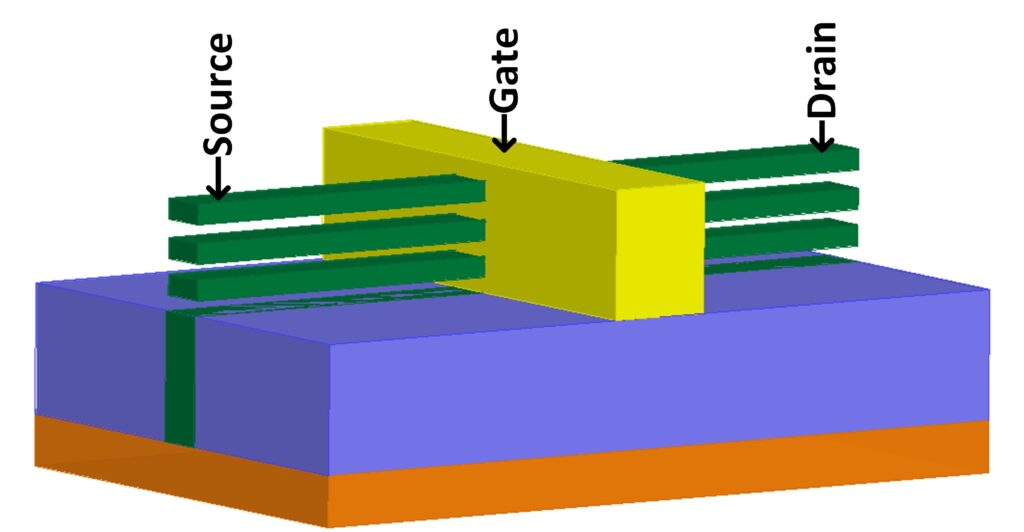

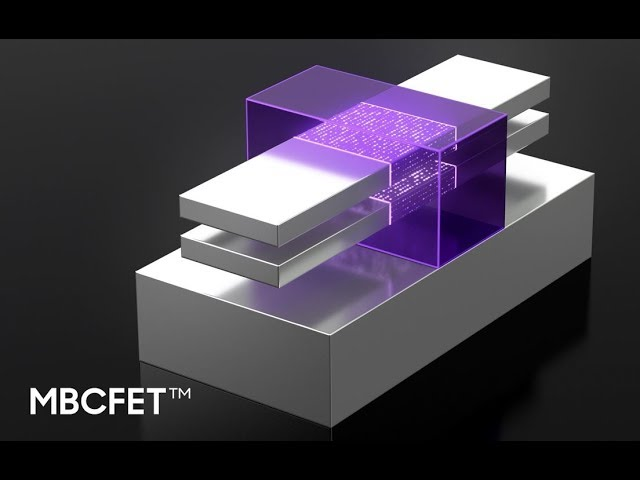

于是,新一代结构被提出——MBCFET,也叫多桥通道晶体管。

它的核心想法是:把纳米线“拉扁”变成一层层“纳米片”,然后横向叠起来,像搭积木一样堆出多个通道。每一层纳米片都被栅极环绕,不仅保留了GAA的强控能力,还进一步提升了导电能力和驱动电流。

更重要的是,MBCFET的通道宽度是可调的,可以根据设计需求,灵活权衡性能与功耗,是FinFET无法做到的。

/5

/5