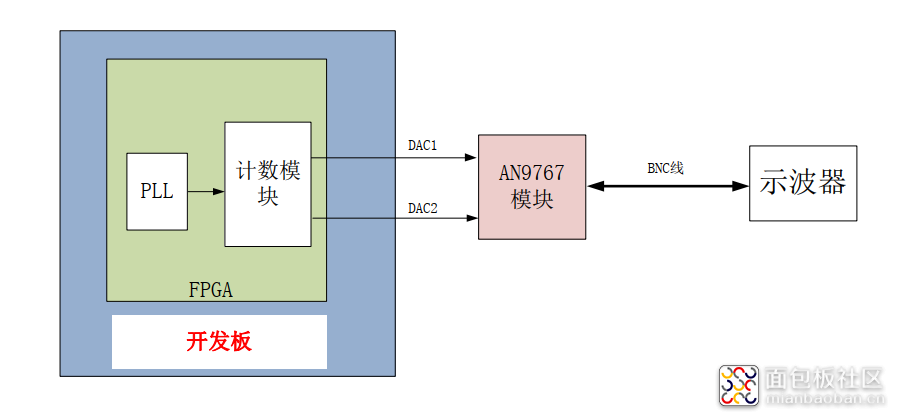

DA 转换芯片: AD9767;

通道数: 2 通道;

DA 转换位数: 14bit;

DA 更新速率: 125 MSPS;

输出电压范围: -5V~+5V;

模块 PCB 层数: 4 层,独立的电源层和 GND 层;

模块接口: 40 针 2.54mm 间距排座,方向向下;

工作温度: -40°~85° 模块使用芯片均满足工业级温度范围

输出接口: 2 路 BNC 模拟输出接口(用 BNC 线可以直接连接到示波器);

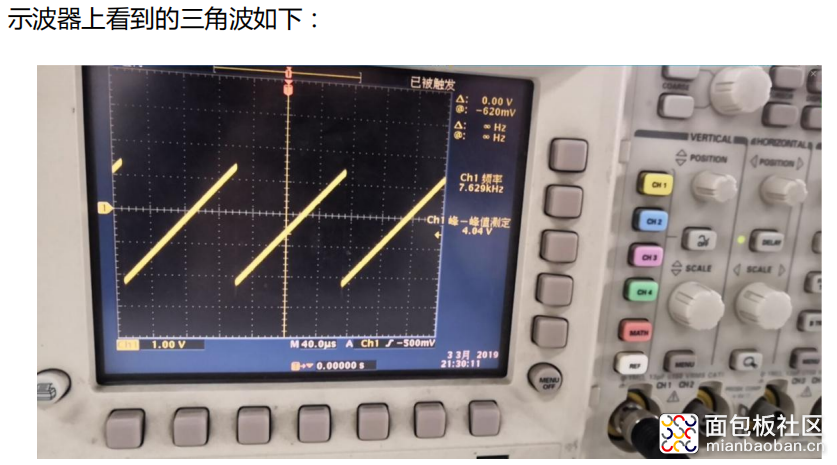

`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// //Two tri wave outputs -10V ~ +10V ////////////////////////////////////////////////////////////////////////////////// module ad9767_test ( input sys_clk, // input clock 50Mhz output da1_clk, //AD9767 CH1 clock output da1_wrt, //AD9767 CH1 enable output [13:0] da1_data, //AD9767 CH1 data output output da2_clk, //AD9767 CH2 clock output da2_wrt, //AD9767 CH2 enable output [13:0] da2_data //AD9767 CH2 data output ); reg [15:0] trig_data; wire clk_125M; assign da1_clk=clk_125M; assign da1_wrt=clk_125M; assign da1_data=trig_data; assign da2_clk=clk_125M; assign da2_wrt=clk_125M; assign da2_data=trig_data; //DA output sin waveform always @(negedge clk_125M) begin if (trig_data == 14'h3fff) trig_data <= 0 ; 4 / 5 else trig_data <= trig_data + 1'b1 ; end PLL PLL_inst (// Clock in ports .clk_in1 (sys_clk ), // IN // Clock out ports .clk_out1 ( ), // OUT .clk_out2 (clk_125M ), // OUT // Status and control signals .reset (1'b0 ), // IN .locked ( ) ); endmodule

复制代码

/5

/5