描述

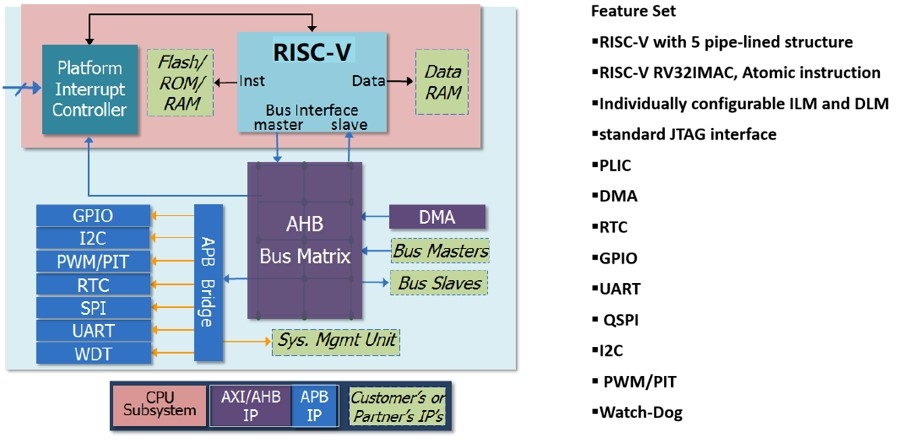

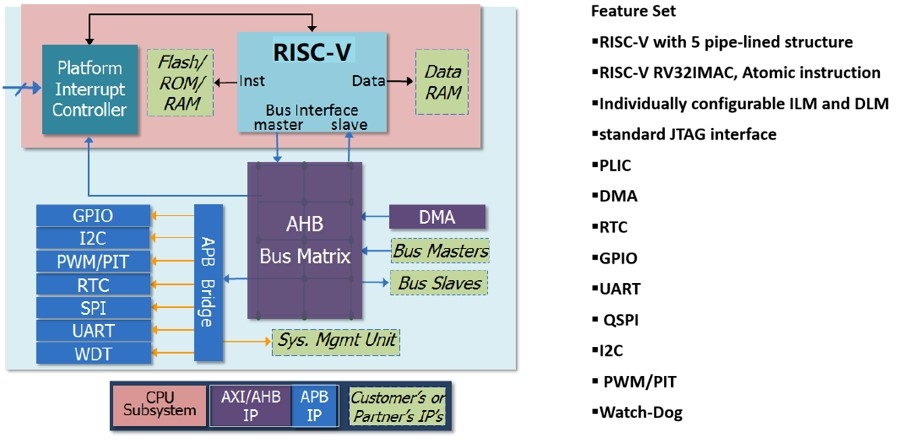

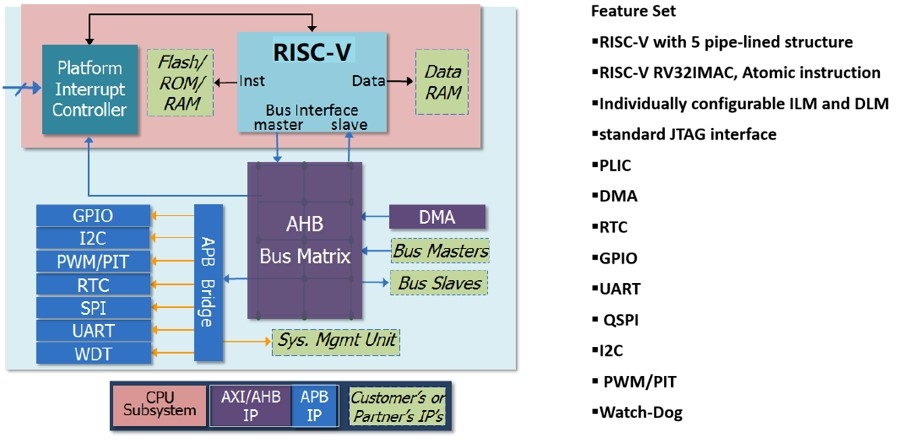

高云可提供基于GW2A系列FPGA的RISC-V软核IP,包含一个32-bit的RISC-V微处理器和系统外设,结构如下图所示:

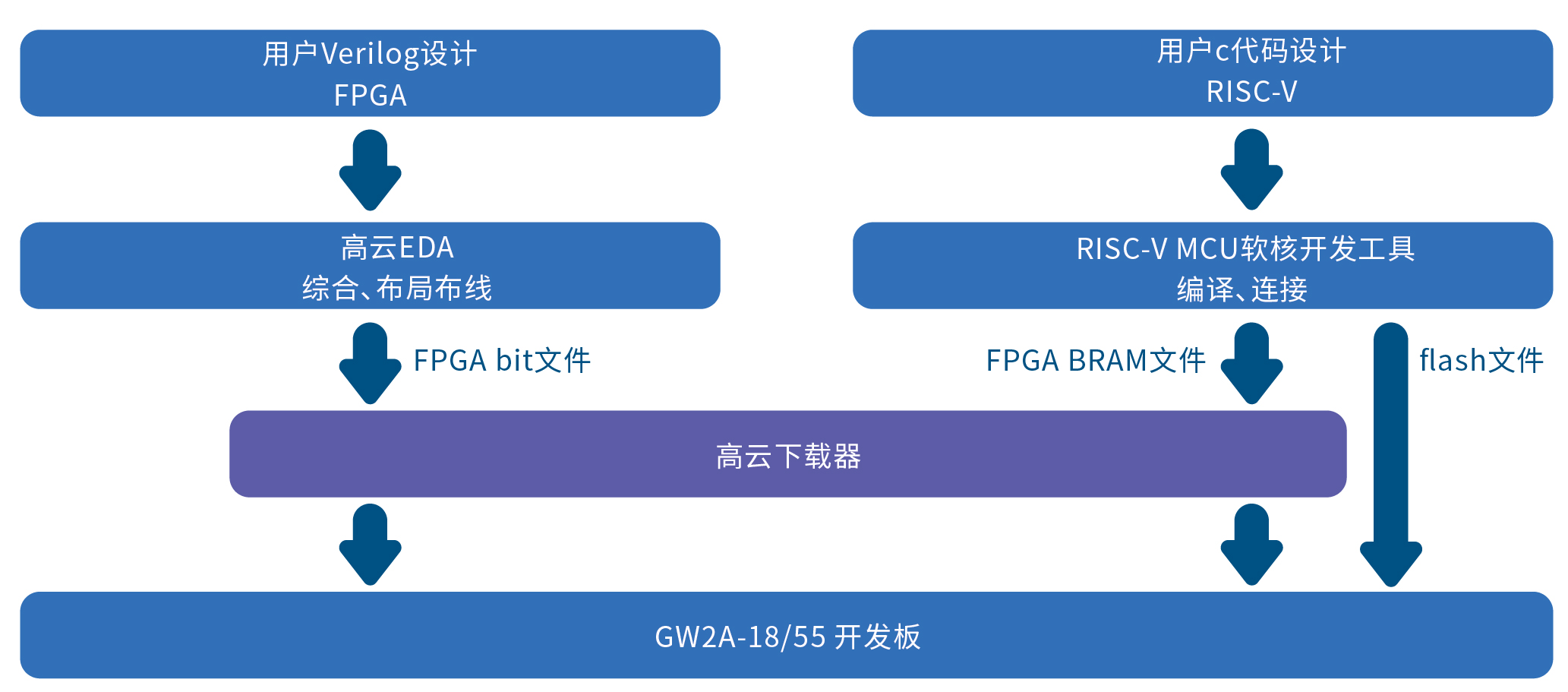

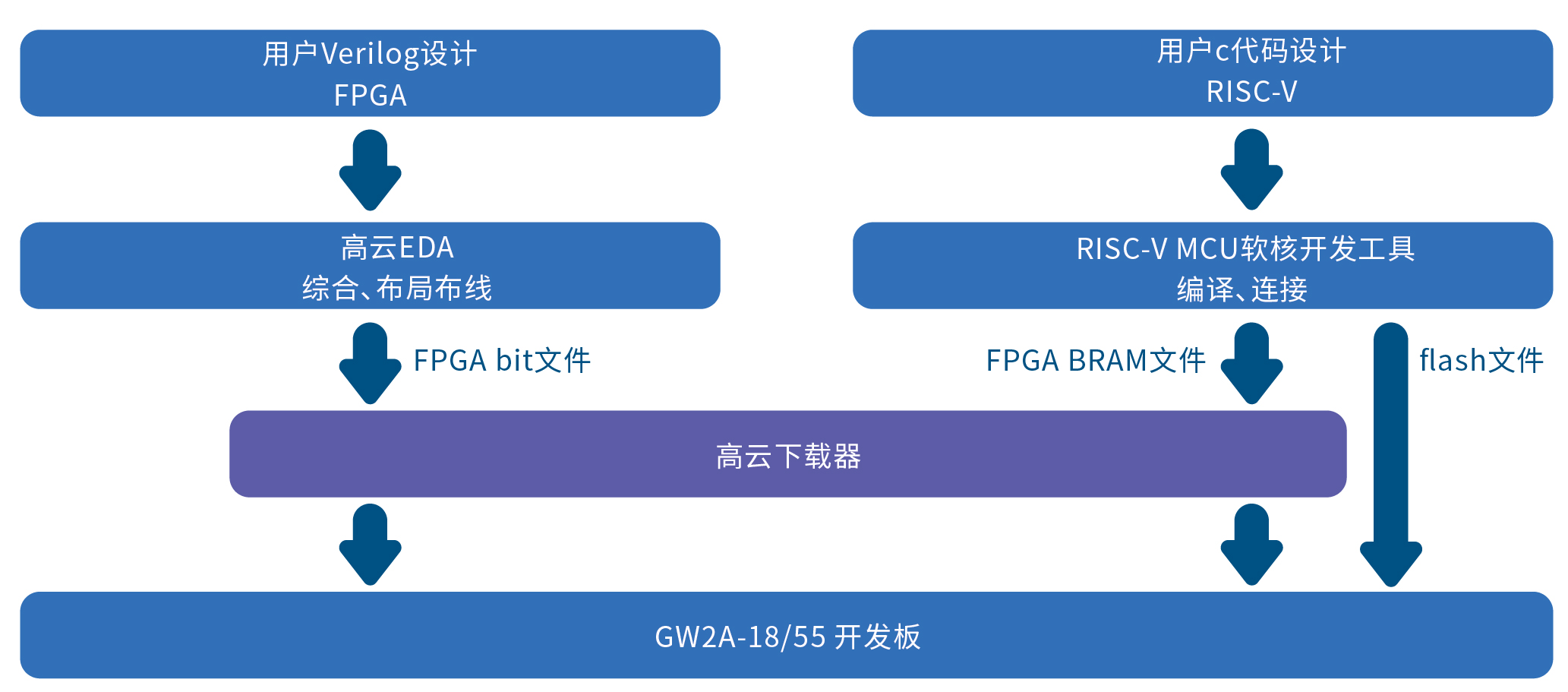

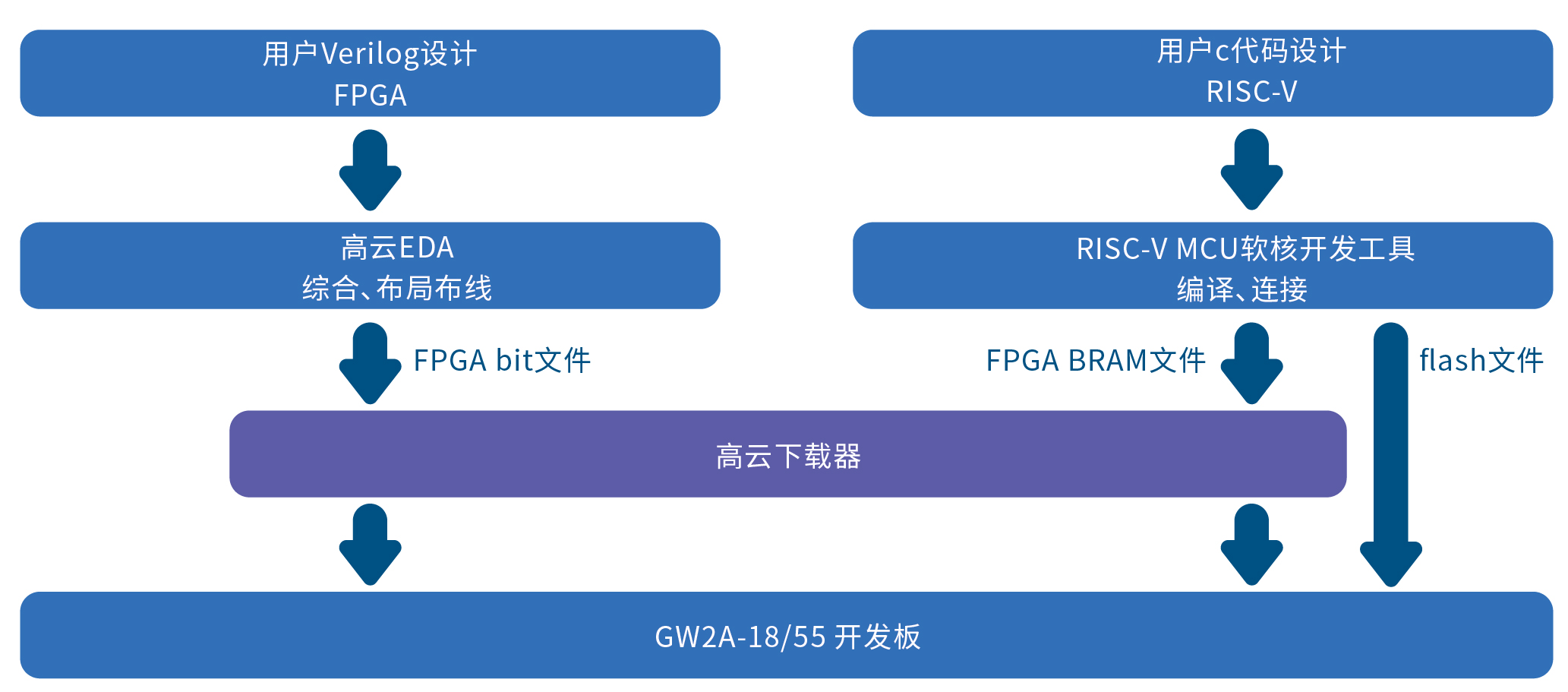

高云提供一体化的开发平台,将RISC-V软核处理器开发流程和FPGA硬件开发流程统一到同一个平台上,用户可以方便地在GW2A-18/55 FPGA上进行RISC-V软核和系统外设的开发。此开发平台支持FPGA的综合布局布线的同时,也支持RISC-V软件的编译、连接、仿真和调试。

高云可提供基于GW2A系列FPGA的RISC-V软核IP,包含一个32-bit的RISC-V微处理器和系统外设,结构如下图所示:

高云提供一体化的开发平台,将RISC-V软核处理器开发流程和FPGA硬件开发流程统一到同一个平台上,用户可以方便地在GW2A-18/55 FPGA上进行RISC-V软核和系统外设的开发。此开发平台支持FPGA的综合布局布线的同时,也支持RISC-V软件的编译、连接、仿真和调试。

暂无评论,快来抢沙发吧

暂无评论,快来抢沙发吧

/5

/5