无处不在的无线技术为高集成度电路创造了市场需求,比如发信机、接收机,以及片上频率合成器等。硅CMOS技术把这种集成变为可能,然而功率放大器(PA)却是个例外,它仍然是用非CMOS技术实现的典型。硅CMOS 功率放大器能够同其它无线构建模块紧凑集成到一起是再理想不过了。下面就是一些CMOS PA设计方案。

功率放大器涉及到许多不同参数的分配,包括附加功率效率(PAE)、线性度、输出功率、稳定增益、输入/输出匹配、散热和击穿电压。与许多RF组件设计技术一样,这些要求常常彼此矛盾,例如,获得较好的线性度往往以牺牲PAE指标为代价。典型地,线性度用输出三阶截点(OIP3)、1-dB压缩点(P1dB)、邻道功率比(ACPR)AM-AM失真(AM/AM)以及AM-PA失真(AM/PM)来*估。线性度改善一般依赖使放大器输出功率远离其饱和输出电平来实现,而且为了满足给定的线性要求,会消耗更多的直流功率。

尽管许多这类折衷摆在功放设计师者面前,放大器电路仍然在过去几年里得到充分地研究,可以查阅到很多设计方法。设计人员能设计出大量有意思的结构。为探究用硅CMOS制造功放的可能性,本文首先分析了单端CMOS 功放,然后是差分COMOS PA。本涉及两种改善线性度的简单结构,并在对高效率E类和F类CMOS PA讨论后得出结论。

相当一段时间内,单端AB类PA在大量应用里有可靠表现,这种类型实际上是A类与B类设计结合的混合体。在一个A类功放中,功率三极管在百分之百的时间内都不会出现偏置电流截止的情况。典型地,一个A类功放接近输出功率,并有着突出的线性,尽管该方法的理论效率只有50%。

通过在其导通门限处设置偏置,B类功放的效率得到改善,这个驱动放大器的输出会使末级功率放大器反复导通和截止,末级功率三极管在该时刻的效率达到50%,这样,B类设计使效率可以提高到78.5%。

AB类放大器实现A类与B类方法的折衷。晶体管的偏置比其导通电压略高,但晶体管自始至终都没有完全导通。AB类功放典型地采用多级实现(图1)以提高PAE,不只是为提高效率。在设计中,器件M1是驱动FET,而M2是输出级FET。输入、输出和中间级的阻抗匹配可以用L、T和Π型网络来完成。漏极到栅极反馈常用在AB类功放设计里来改善稳定性;这种反馈还能简化阻抗匹配。在这个专门的设计里,电阻R3和R5以及电容C2和C6是反馈元件。电阻R1和R2,电阻R4和R5构成简单的电阻驱动网络来对晶体管进行偏置。通过采用不同的电阻分压比,图1的基本电路可以改换到其它多种PA结构中,包括A类,B类和C类。

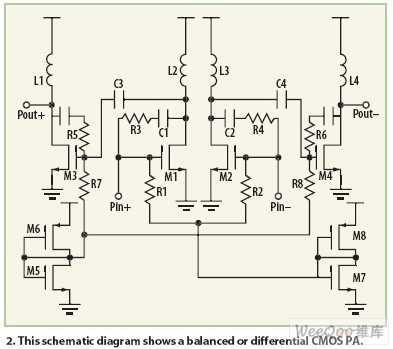

CMOS收发器一般采用差分电路来实现,以降低其对共模噪声的敏感程度。图2给出了一个标准的差分功放。它本质上是两个并联的单端功放。FET M5,M6以及M7和M8构成电阻分压器。为使放大器同外部滤波器连接,需要一个平衡(差分)输入滤波器,该滤波器的输出可以是非平衡的,以便同单端天线接口;也可以设计成平衡输出,以适用于双极子天线。

由于单端滤波器和天线应用广泛,实际设计时会在功放内部集成平衡非平衡(balun)变压器,图3给出一集成平衡非平衡变压器的通用差分功放。这种设计从图2的增益模块结构改进而来,并且采用了一种级联形式。级联降低了栅-漏极电容(Cgd)密勒效应,并使输入输出端口隔离度增加,不用反馈也提高了放大器稳定性。

同使用单级晶体管相比,这种设计方法还提高了增益。这里只详细讨论其中,因为整个电路使用了类似的电路结构。较低的晶体管M1采用镜像电流偏置,由于晶体管M10的作用,M1的偏置电流是偏置电流I2缩放。增加这样一个“二极管”类型偏置的好处在于,该偏置电流能跟踪功率FET的偏置变化情况,防止出现“热失控”问题。类似于M3,顶层级联晶体管被偏置在饱和区,这通过简单地把其栅极跟电源连接而实现。这样,栅极电压Vgd总是低于门限电压Vt,满足保持在饱和区的要求。输出平衡非平衡1倍变压器可以用螺旋型集成电感来实现。电容C5和C6是平衡非平衡变压器输入的阻抗匹配元件。有很多关于设计集成平衡非平衡变压器的理论和技术,这超出了本文讨论的范围。低损耗平衡非平衡变压器在许多设计中已见诸报道,可用作举例。

一些简单技术可用来改善CMOS功放的线性度而不消耗额外的直流功率。图4a 和图 4b显示了两个这类结构。前者采用了“二极管”类型的线性化电路(图4a),随着PA输出功率增加,晶体管增益开始下降(AM/AM 失真),其相位噪声开始增加(AM/PM失真)。幸运的是,基于FET的二极管会在这些情况下表现出相反的行为,它在扩大增益的同时相位噪声降低。通过仔细的器件选择和设计,功率放大器的线性度就能得到改善。图4a的电路跟前面给出的AB类相比略有改动,晶体管M3起到线性“二极管”的作用。

另一种提高PA线性度的简单方法是进行AM/PM补偿。绝大多数AM/PM PA失真来自栅极-源极电容(Cgs)的变化。通过用 一 PMOS FET抵消NMOS FET Cgs的变化,CMOS PA线性度就能得到改善。图4b给出了一个一般性设计,晶体管M3作用为补偿电容。图4a与图4b的线性化电路均可以对基本CMOS PA结构的输出功率级作改动后实现。

AB类和C类功放结构通过降低FET传导角度来提高效率。此外,E 类和 F类结构也可以提高效率。理论上,E 类和 F类结构能达到100%的效率。在E类功放中,功率管在导通与截止间切换,意在减少电流和电压波形通过FET漏极和源极时的交叠。交叠区代表未能交付给负载的功率,因此交叠要尽可能少。通过功率管导通和截止切换,同一时刻,电流或电压只有一个处于导通状态,不能同时导通。

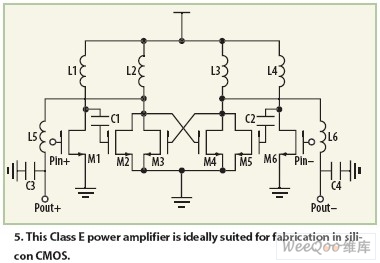

许多研究团队已经演示验证了E类CMOS 功放具有高效率。18、19图5显示出E类功放的一般性结构。在这个两级结构设计里,器件M1和M6为驱动级,而晶体管M2和M5构成输出功率级。器件M3与M4起到控制器件来改善输出器件M2和M5间的切换作用。

考查晶体管M3和M4工作情况的一种办法是研究振荡器注频模式锁定。E类功放会对输入频率/相位改变作出反应而不是对幅度作出反应。正如注频模式锁定理论解释的那样,如果有另一个源在附近,振荡器会典型地振荡在一个不同频率。交叉耦合器件M3和M4以及储能电路必然形成CMOS振荡器。前往功率级的输入信号必然会牵引基于M3和M4的振荡器振荡频率。这种方案有助于通过降低输入驱动要求来提高效率。

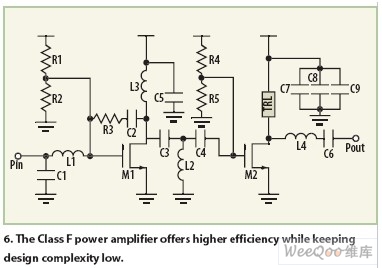

F类功放(图6)通过对输出漏极电压和漏极电流整形来提高效率。这种结构可通过再次修改图1中的AB类功放基本形式得到,即对第二级改动。该思想是让晶体管M2的漏极对基频和奇次谐波表现为高阻抗,这样电压波形就变成方波。不过,在偶次谐波频率处,阻抗很低。这种谐波端接技术把电流整形为半正弦波。谐波端接用四分之一波长传输线(TRL)以及C7、C8和C9等电容来实现。尽管F类功放实现起来相当直接,集成四分之一波长传输线却仍是个挑战,它一般被制作在功率放大器的印刷电路板上而不是在芯片上。

就其本身而言,CMOS 功放在性能上还不能同其他射频/微波器件技术相竞争,如GaAs FET放大器,甚至GaAs异质结双极晶体管(HBT)。不过,但它确实为更高程度集成硅CMOS电路带来了潜在希望,特别是在当射频电路必须与数字信号处理部分集成在收发器IC内的时候。

/2

/2