超低噪声LDO

噪声好像是人人讨厌的东西,LDO中自己产生的噪声主要是1/f噪声和热噪声。而LDO输出的是直流电压,也就是说是频率为零的纯净信号。可是自己本身就要产生噪声,你让吃瓜群众怎么说呢?

反正我到现在还没有看得哪个大牛文献把1/f 噪声用模型,从理论到实践讲清楚,也许因为爱因斯坦那一年集中注意力研究光电效应,于是有了今天的各种自拍和美图秀秀,却没有人讲得清楚1/f噪声。一般认为半导体电路中的1/f噪声是由于载流子的涨落效应。频率越低越严重,电流越小噪声越严重。热噪声取决于温度和电阻。于是做陀螺仪的和做LDO的,这些注定要输出低频,极低频信号的器件,一生都要和它搏斗。

可是我们真的要对付那些噪声吗?你们那些运放不是都号称PSRR很高的吗?动辄90dB,100dB,十万分之一哎,什么噪声会影响这么厉害?还有,你们的RF信号,神龙见首不见尾的高频信号,动辄频率高到2.4GHz,5.8GHz,干吗非要对付我们电源上那些趴在那儿,只有几十kHz,几百kHz的噪声呢?

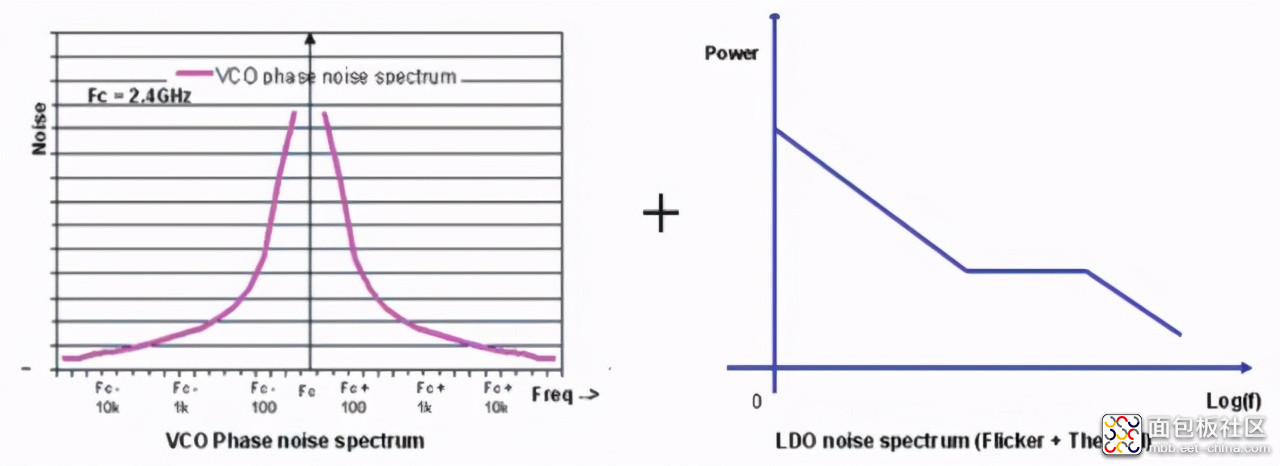

其实无论精密信号,还是RF信号,最终都会受到低频信号的影响。前者本身就是低频信号,后者的心脏PLL很容易受到低频噪声的影响。下图左是2.4GHz VCO(锁相环的核心)相位噪声谱,右边是典型的固有噪声(1/f噪声+热噪声):

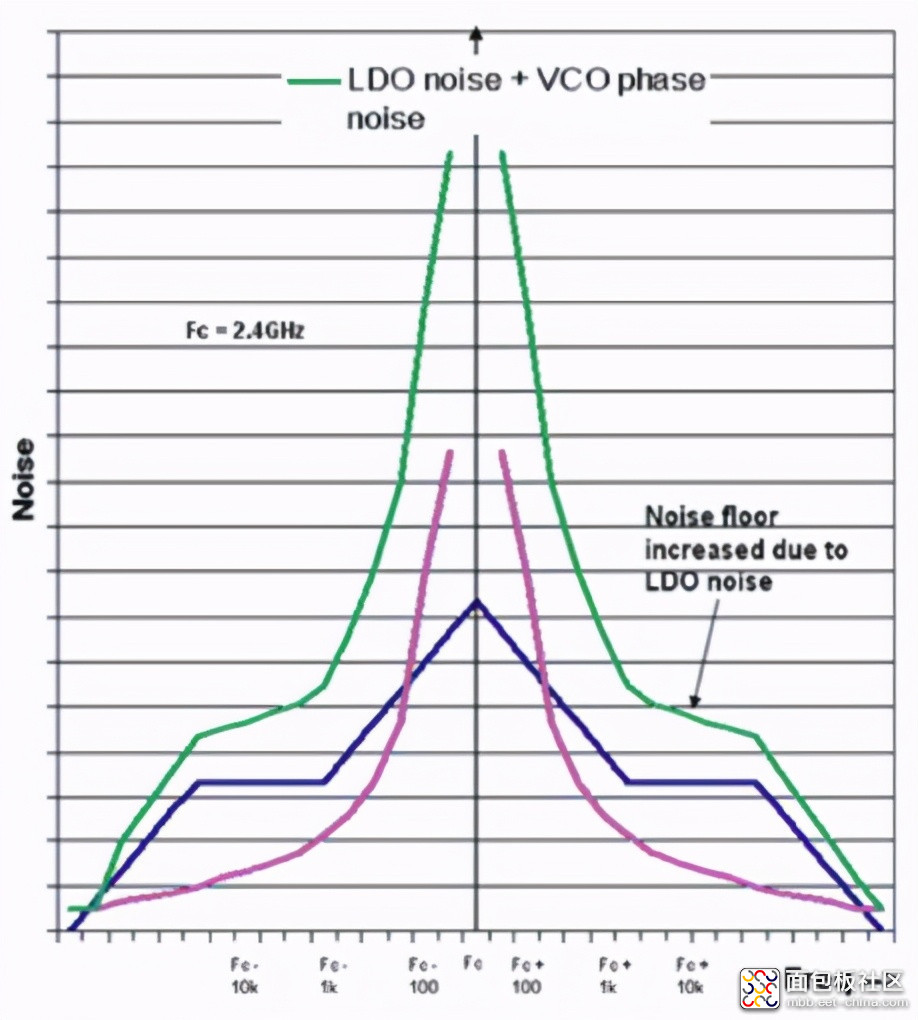

最后LDO电源噪声被载波频率调制,反应在VCO就是背景噪声上升:

工程上解决LDO的噪声似乎不太难。

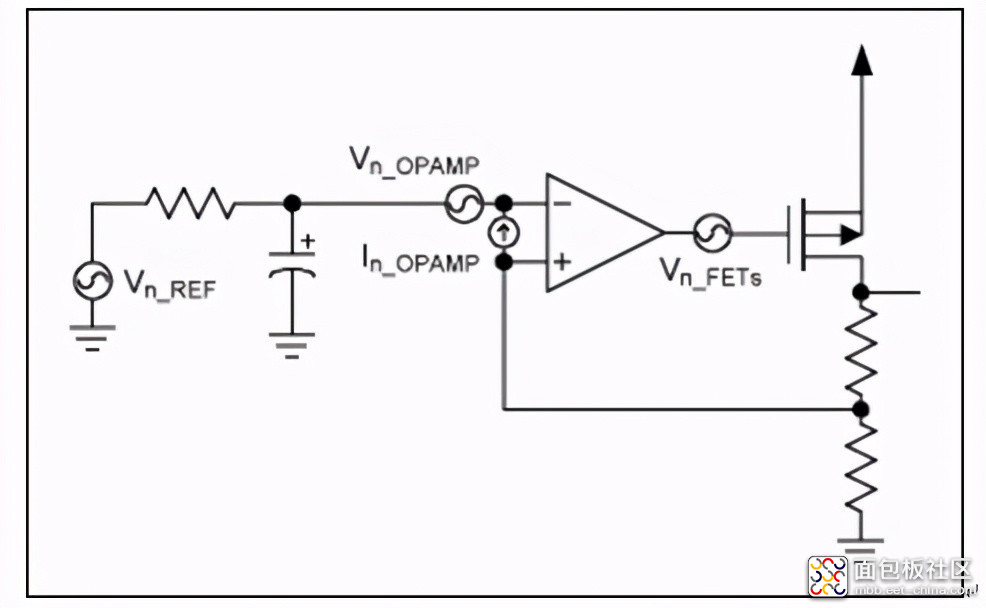

下图是常用的低噪声LDO结构图。

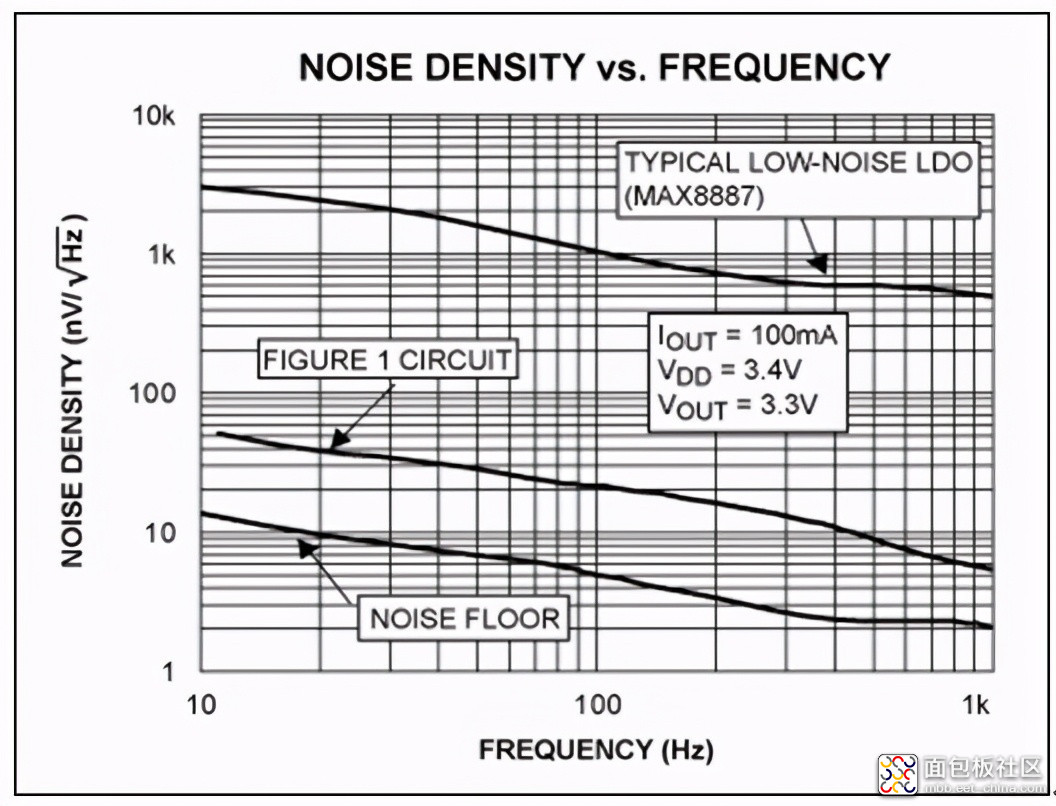

就是在电压基准上串一个电阻,加上一个电容,对基准电压构成一阶低通滤波。假定R=10k,C=100uF,f3db=0.16Hz,整个噪声密度可以降低38db。Maxim有一个工程实验,下图是结果对比:

用这种技术做成的低噪声LDO,往往有一个外接电容,一般在0.1uf与2.2uF之间,也有内置电容的,效果略差。

上述架构进一步降低噪声密度很难了,因为带隙基准本身有噪声,片内电容很难做大,用来做低通滤波的电阻本身有热噪声,而且电阻越大,滤波效果越好,但同时热噪声越大,这构成了根本矛盾。

超低电流LDO

LDO是处理电流的器件,但就好像财务是处理资金的,但也要发工资。

LDO的消耗电流和LDO上面流过的电流是有一个函数关系。

因为这个开销,许多超低功耗的物联网应用干脆不用LDO,直接接在电池上,默默承受电压的不稳定。

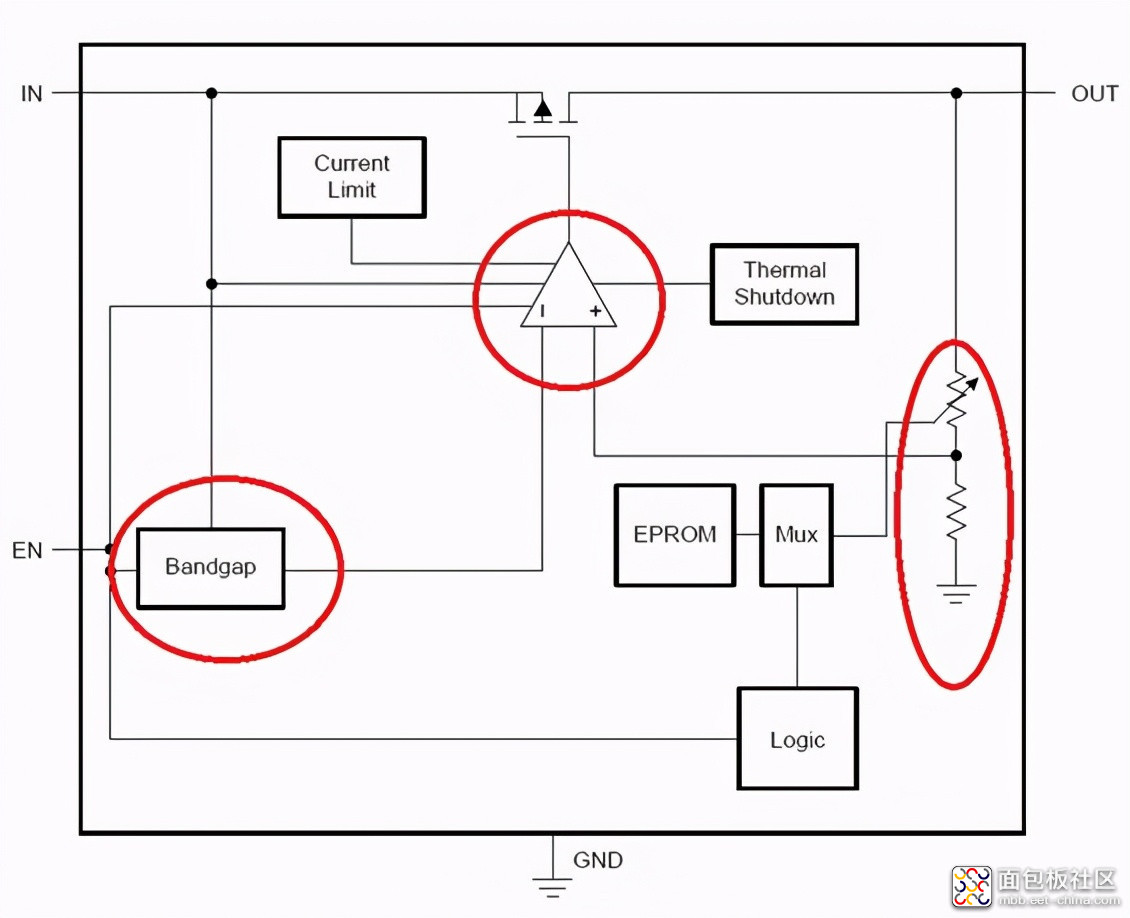

上图是一个静态电流低到只有420nA的LDO内部结构,可以看出,其中有3个电流消耗大户,一是带隙基准,二是误差放大和驱动电路,三是分压网络,分别3个红圈。驱动电路的功耗一般和输出电流有关,一般应用不太在乎,因为系统本身功耗远大于LDO的自身功耗。

系统工程师最在意的是Badgap的绝对功耗,分压网络功耗,因为常见的分压网络通常外置,本身就要消耗几个uA。其次LDO最好能有使能端可选,在设计需要的时候把整个LDO关闭。

该内容是小编转载自 开源Block

/4

/4