根据AMD目前的规划,他们目前唯一计划中的,具有 3D V-Cache 的当前一代锐龙处理器(Ryzen 7 5800X3D)尚未上市,因此 AMD 将在 ISSCC 2022 上提供一些超出我们已经知道的实施细节。

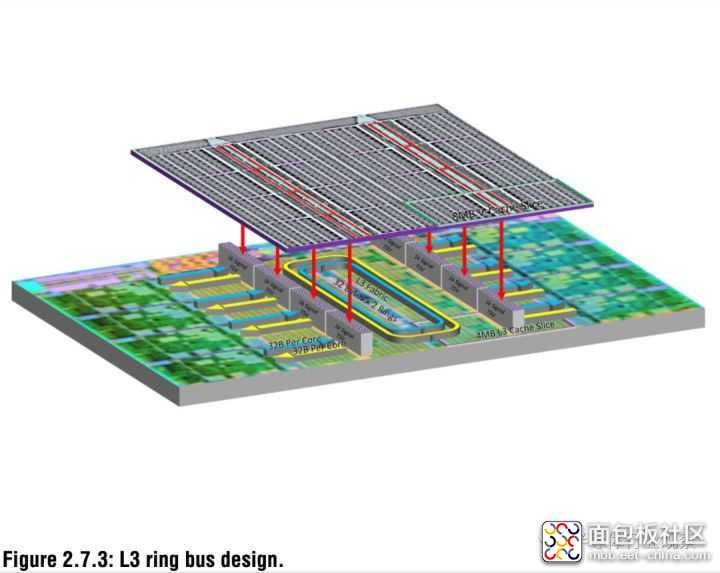

首先,我们首先回顾一下,在缓存层次结构中,Zen 3 架构最大的变化是共享 L3 缓存,容量为 32 MB,最多可支持 8 个核心。核心计算复合体以前被划分为 2x 16 MB。这伴随着新的划分为八个而不是四个切片(部分),并且相关的互连成为双向环形总线,环形总线上的每个时钟每个时钟 32 字节(在每个核心)。这带来的结果是更高的带宽和更低的延迟,以帮助 Zen 3 架构实现其性能目标。

从理论上讲,现在每个内核都可以使用完整的 32 MB 三级缓存。但 L3 缓存的生产也发生了变化。AMD 现在使用高密度 (HD) 位单元,而不是以前使用的高电流 (HC) 位单元。这导致面积减少了 14%,缓存阵列泄漏减少了 24%。

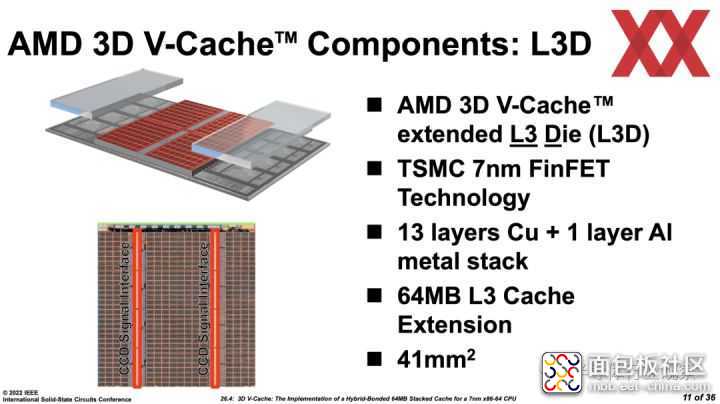

但AMD也留了一个“后门”,这在实践中还没有发挥作用。那就是L3 高速缓存可通过额外的 SRAM 芯片从 32 MB 扩展到 96 MB。尺寸仅为 36 mm² 的缓存芯片放置在 CCD 的 L3 区域,并通过铜焊相互连接。两个芯片的界面之间的纯粘合就足够了。不需要焊接。

现有缓存阵列和附加缓存之间的连接是通过 TSV 实现的。AMD 在缓存块之间提供两行 TSV 连接。对于每个 8 MB 3D V-Cache Slide,AMD 提供 1,024 个连接。因此,CCX 和 3D V-Cache 之间有 8,192 个连接。

TSV 接口提供每片超过 2 TBit/s 的带宽。L3 高速缓存的环形总线在两个方向上也实现了超过 2 TB/s 的速度,因此能够为内核提供最大的 L3 高速缓存带宽——即使使用额外的 3D V-cache 也是如此。

制造的进一步改进

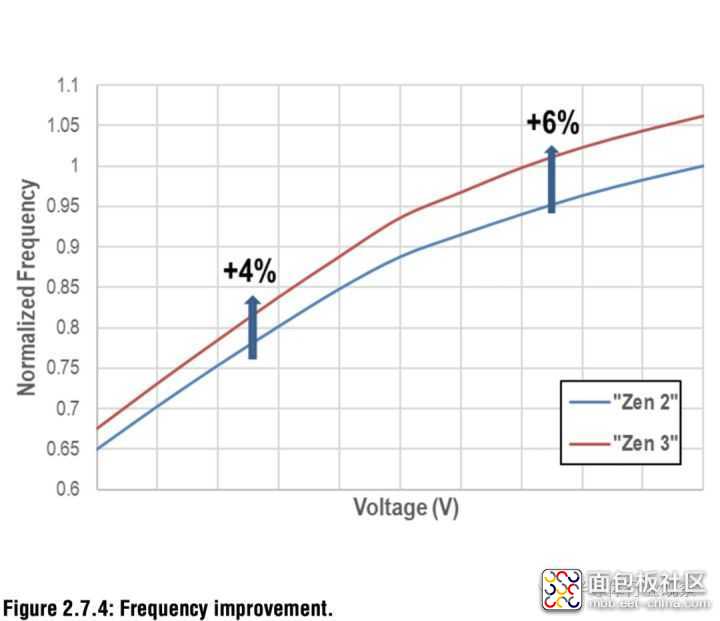

在生产中,台积电在 7 nm 工艺中进行了优化,13 层中的下层设计用于高密度,上层设计用于尽可能高的时钟频率。目的是在保持电压的同时将时钟增加 4%。单线程区域的峰值性能可提高 6% 的电压。

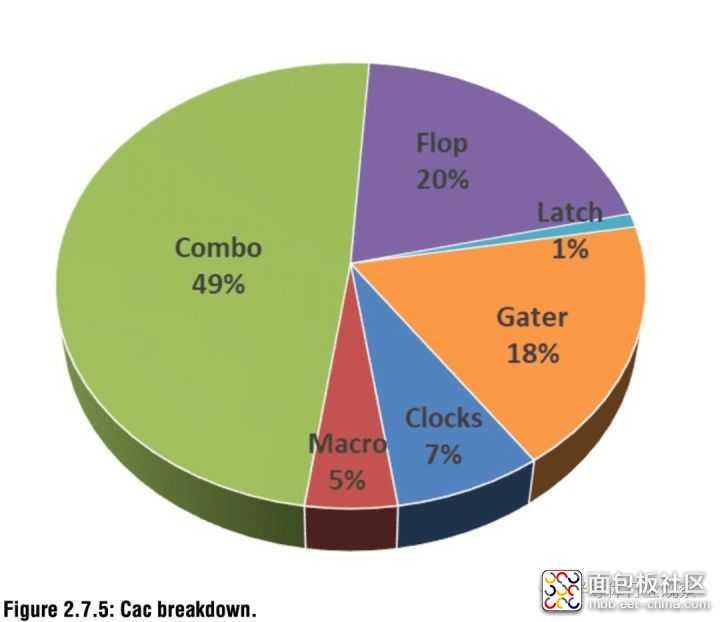

然而,对于 Zen 3,AMD 还尝试了逻辑块的结构化布局、HC 和 HD 单元的选择以及优化的布线工程,以实现高压下的大幅频率提升。核心的单个tile尽可能小,以便每周进行多次设计迭代。为了实现 19% 的 IPC 增加和 6% 的时钟增加,AMD 必须将 CCX 有效开关电容 (Cac) 提高 15%。

与上一代相比,时钟门消耗的 Cac 百分比略有增加。另一方面,由于 Zen-3 架构的额外时钟门效率优化,触发器和组合逻辑消耗的部分略有下降。稍高的泄漏被频率的增加和功率效率的进一步提高所抵消。

AMD 为 Zen 3 架构感到自豪——尤其是在 L3 缓存的可能扩展方面。

更多细节

在分组讨论中,AMD 详细介绍了 3D V-Cache 的实施。快速说明:我们还将在下文中更频繁地使用术语 SRAM 和 L3D。这总是意味着 L3 缓存的扩展。

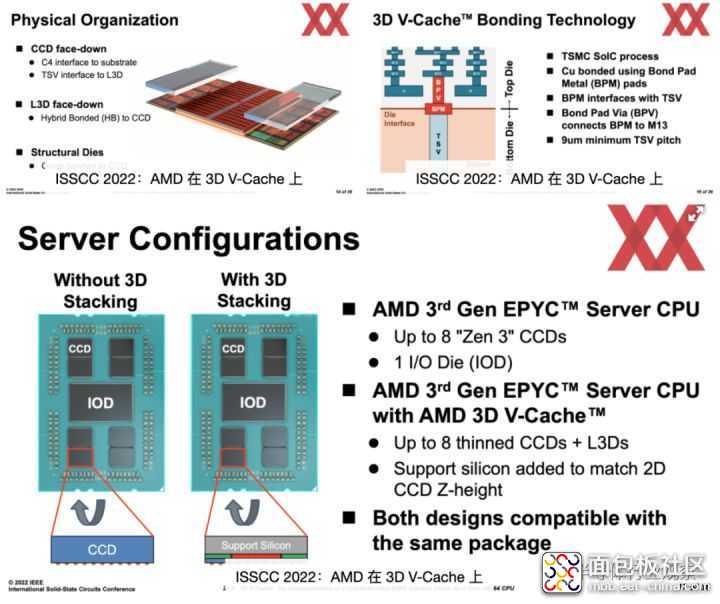

首先,AMD 重申了一个事实,即 CCD 被磨平以允许将 SRAM 放置在顶部。C4接口,即连接,都在载体基板的方向上对齐。研磨将暴露 TSV。然后将 SRAM 芯片“面朝下”放置在 CCD 上。在没有 SRAM 但核心暴露的地方,放置结构芯片。到目前为止,AMD 公布的尺寸为 36 平方毫米(6 x 6 毫米)。现在有传言说 SRAM 的尺寸为 41 mm²。

AMD 使用 TSMC 的 SoIC 技术进行 3D V-Cache 的封装和布局。焊盘金属 (BPM) 焊盘应用于 TSV。Bond Pad Vias (BPV) 然后将此 BPM 连接到第 13 个金属层的最低层。支持硅,即无源硅元件,也应用于 CCD,使 CCD 具有与 IOD 相同的高度。

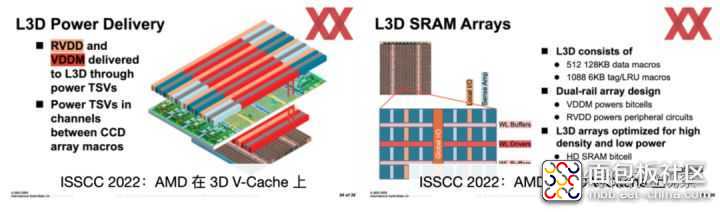

SRAM 也通过 TSV 提供。可用于内核的 RVDD 和 VDDM 电压轨通过 CCD 路由到 L3D (SRAM)。

为了将 3D V-Cache 的访问保持在与 CCD 中的 L3 缓存类似的级别,AMD 将 SRAM 划分为 512 个数据块,每个数据块为 128 kB。此外,还有 1,088 个 6 kB 标签宏,以便能够快速找到数据。带宽应大于 2 TB/s。根据 AMD 的说法,访问扩展的 L3 高速缓存时的延迟应该只有四个额外的时钟周期。

SRAM 也通过 TSV 提供。可用于内核的 RVDD 和 VDDM 电压轨通过 CCD 路由到 L3D (SRAM)。

为了将 3D V-Cache 的访问保持在与 CCD 中的 L3 缓存类似的级别,AMD 将 SRAM 划分为 512 个数据块,每个数据块为 128 kB。此外,还有 1,088 个 6 kB 标签宏,以便能够快速找到数据。带宽应大于 2 TB/s。根据 AMD 的说法,访问扩展的 L3 高速缓存时的延迟应该只有四个额外的时钟周期。

深度测试AMD 3D V-Cache技术,过誉了?

近日,科技评论网站Chips and Cheese发布了 AMD 新3D V-Cache技术的评论,展示了其与前几代 Zen 处理器相比的性能。Chips and Cheese 选择了 AMD 的 EPYC(霄龙)服务器处理器来担任这个角色,包括支持 3D V-Cache 的 EPYC 7V73(Milan-X)和 vanilla Zen 3 EPYC 7763(Milan)。

3D V-Cache 是 AMD 开发的一项新技术,可以让 L3 缓存垂直堆叠,这样可以在占用很少空间的情况下显着增加缓存的大小。AMD 已经通过新技术展示了令人印象深刻的性能提升,因为它允许 CPU 内核始终如一地获得更多信息。

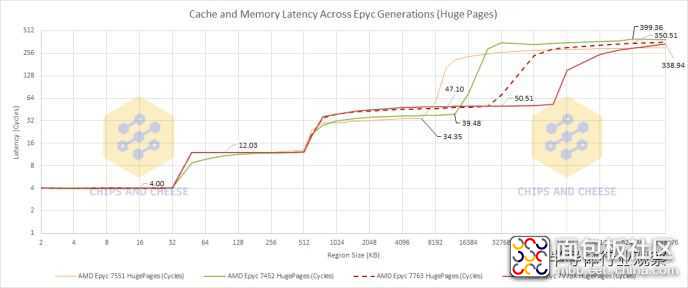

单独比较 Zen 3,有无 3D V-Cache 时,Chips and Cheese 注意到,当测试没有使用更多的 L3 缓存时,带有 3D V-Cache 的EPYC 7V73的性能仅比普通 Zen 3 EPYC 7763 差一点。7763 必须提供什么。延迟差异为三到四个周期,由于 3D V-Cache,这是一个必要的权衡。

然而,一旦 7763 上的缓存被填满,7V73 凭借其巨大的缓存大小,使得芯片的延迟比 7763 显着减少,直到 3D V-Cache 被填满。有趣的是,7V73 的内存延迟也比 7763 略低。

在将 Zen 1 和 Zen 2 EPYC 芯片(如 7551 和 7452)添加到组合中时,我们看到了 AMD 3D V-Cache 芯片真正经过精心设计的更好画面。Chips and Cheese 指出,L3 缓存设置为从 Zen 1 计数到 Zen 2 会产生大约 5 个周期的额外延迟。然后从 Zen 2 统一 Zen 3 上的双 16MB L3 缓存块的举措增加了更高的 7 到 8 个延迟周期。

与此同时,AMD 从 Zen 3 迁移到 Zen 3 3D V-Cache,并将 L3 缓存大小增加三倍只需要三到四个周期的延迟,这是迄今为止我们看到的最微不足道的损失。

Chips and Cheese 的图表显示,所有 Zen 世代的 L1 和 L2 缓存延迟几乎相同。尽管如此,当谈到 L3 缓存时,延迟会随着代际之间的 L3 缓存使用量的增加而减少,尤其是在 Zen 3 到带有 3D V-Cache 的 Zen 3 中。

- 带宽

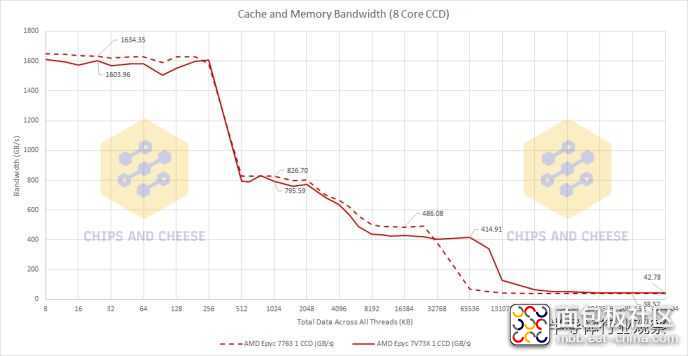

在带宽结果中,Chips and Cheese 发现 AMD 的 7V73X 3D V-Cache 提供的带宽不如 AMD 所宣传的那么多。在测试中,它注意到 7V73X 在单线程缓存带宽测试中每个周期只增加了大约 25% 的字节——这与 AMD 承诺的 2 倍带宽增益相去甚远。

然而,Chips 和 Cheese 认为,一旦 CPU 处理利用 L3 缓存的更大工作负载,时钟速度可能会降低,这确实解释了这种差异。

另一个奇怪的现象出现在7V73X上,单颗CCD缓存带宽测试显示,3D V-Cache芯片的带宽相比标准7763略有不足,约为12.5%。Chips and Cheese 怀疑这是为了控制功率,因为两个芯片上都加载了 64 个内核。这很有意义,因为 3D V-Cache 确实占用了更多空间并且需要更多的功率,这使得 CPU 冷却变得更加复杂。

有趣的是,同样的现象也发生在 AMD 基于 Zen 2 微架构的 EPYC 7452 芯片上。EPYC(霄龙)7763 Zen 3 CPU 是唯一一款在单 CCD 带宽测试和单线程带宽测试中表现均等的芯片。

对于那些想知道 Zen 1 的人来说,缓存带宽甚至比 Zen 2 和 Zen 3 还差。在绝大多数测试中,经过测试的 EPYC 7551 的带宽不到一半。直到测试的中期和结束阶段,它才接近赶上。

- 结论

那么所有这些数据在现实世界的表现方面意味着什么呢?Chips and Cheese 运行了多个基准测试,包括 Gem5、libx264 4K 转码、7-Zip 等。只有在 Gem5 中,3D V-Cache 才对性能产生了显着影响。其余的则乏善可陈,几乎不引人注意,大约 5% 的性能优势有利于 3D V-Cache 芯片。

Chips and Cheese 的初步结果表明,3D V-Cache 的影响并不像 AMD 已经预测的那样显着。但是,它需要更深入的测试才能通过判断。此外,我们不能忘记这是 AMD EYPC 服务器处理器上的 3D V-Cache,因此 3D V-Cache 在其消费者对应产品上的行为可能会有所不同。

一方面,7V73X 是一个拥有 64 个核心的怪物芯片,因此该芯片对热量和功率输出很敏感,如果需要,它会迅速限制 CPU 核心。它是通过添加缓存来调整的,对 CPU 增加了更多的功率和散热要求。

另一个是服务器工作负载,由于其性质,传统上它的计算量比延迟敏感度更高。3D V-Cache 只有在内核不是瓶颈并且不运行需要大量时间来处理的线程时才会被证明是有用的。

在消费领域,我们看到芯片的内核数量大大减少,这降低了功率要求,并允许内核在时钟速度偏差较小的情况下伸展它们的腿。强大的冷却系统和主板包含强大的供电解决方案,其空间远大于 CPU 在 PC DIY 空间中所需的空间,这不是问题。

消费场景中的应用的计算密集度通常要低得多,这使得缓存延迟发挥了更关键的作用。这在视频游戏中是非常正确的,其中 CPU 很少加载到 100%,但是具有较低的延迟意味着预渲染帧可以更快地传输到 GPU,减少输入延迟并提高帧速率。

来源:本诺电子材料

/2

/2