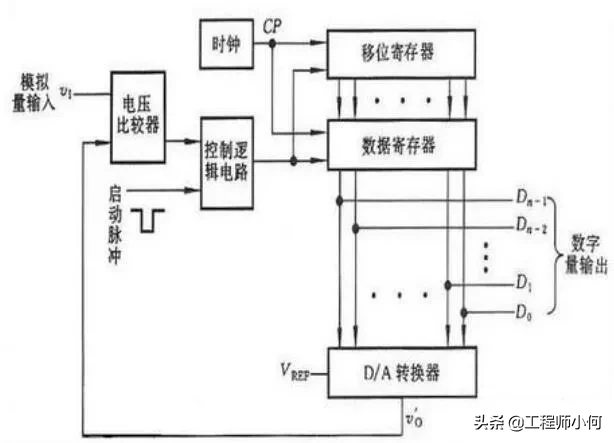

逐次逼近型ADC是由1个比较器、1个数模转换器、1个逐次逼近寄存器(SAR)和1个逻辑控制单元组成。将采样输入信号与已知电压不断进行比较,1个时钟周期完成1位转换,N位转换需要N个时钟周期,转换完成,输出二进制数。下图为逐次逼近ADC框图。

图片来源于网络,侵删

我们通常用天平称重来跟SAR ADC来做类比。天平称重的时候先放最重的砝码,如果物体重于砝码,则移去砝码换上次重的;若物体轻于砝码,则加上次重的再次进行比对。依次循环上述过程,直到天平平衡为止,则砝码重即为被测物体重量。

SAR ADC也与此类似。4bit的SAR ADC输出范围为0000~1111,为4位二进制数。逻辑控制单元首先将最高位取1,其余为0,即1000,然后通过DAC将1000数字量转换为模拟量的形式输出Vo’,Vo’送入电压比较器,与待转换的模拟输入量作比较。这时,

1> 若Vo’<Vin,则保留最高位1,并且把次高位设为1,其余位依旧保持0不变,即得到数字量1100,再转换为模拟量与输入作比较,循环上个过程直到完成4位转换;

2> 若Vo’>Vin,则去除最高位的1,换成0,再将次高位设为1,其余位保持不变,即得到数字量0100,,再转换为模拟量与输入作比较,循环上个过程直到完成4位转换。

因此,SAR ADC为从高到低逐位比较,逐次逼近至相等,由此得名。

误差:

SAR ADC也存在量化误差,还是以4bit为例,若6.1幅度的信号,量化后为6,即0110,7.9幅度的信号,量化后为7,即0111。可以看出来,信号都是直接抹去小数部分,而不是进行四舍五入的。这也跟原理有关,因为它会首先拿最高位做比较,7.9<8,最高位置0,次高位比较,7.9>4,置1,再第三位第四位比较,最终得出7。因此SAR ADC量化误差最大可以到最低位的90%。

在后期处理中,可以通过软件编程来进行误差补偿,来减小误差的大小,常见的是最低位(LSB)+0.5的方法,这里不展开说明了。

优缺点:

SAR ADC的转换精度由于逐次逼近,相对来说比较高,转换速度相对来说也比较快((n+1)Tcp,其中n为位数,Tcp为一个时钟周期)。但是抗干扰能力没有双积分型的强。并且可以通过调整参考电压Vref来调整ADC的测量范围。

应用:

由于转换速度固定,且比较快,因此被广泛应用在实时采样比较的模块电路中,例如电压采样模块、温度检测模块等。

来源:手机射频驿站

/5

/5