在集成电路设计中,经常会用到MOS管作为电容,由于MOS电容是一个栅控电容,所以其容值并不精确,所以在高精度电路中MOS电容不能被应用,但是MOS电容的优点是节省面积,所以在对容值精度要求不高的电路中,MOS电容应用较多,比如作为稳压电容,滤波电容等等。由于MOS电容容值随电压变化,下面我们分析MOS电容的C-V特性。

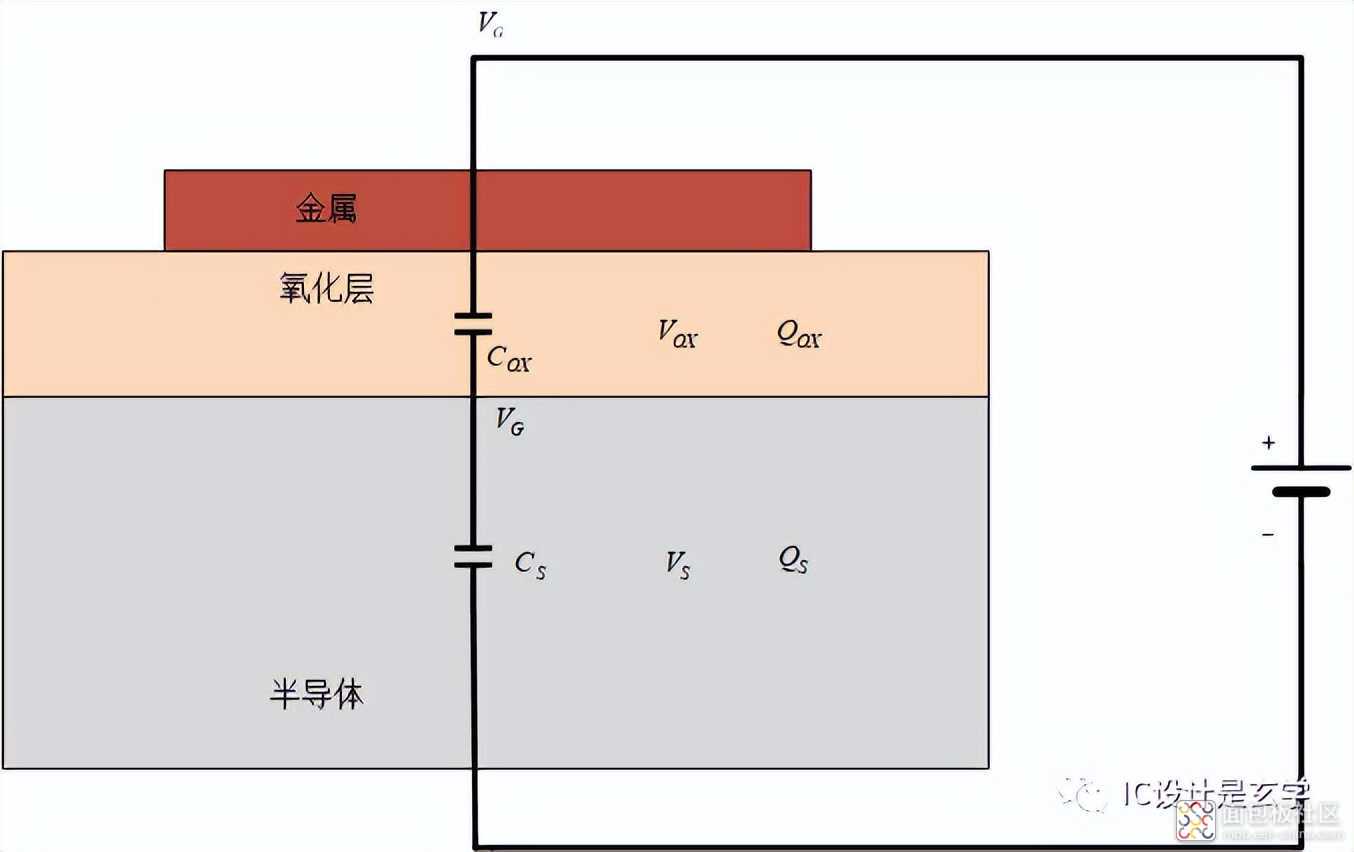

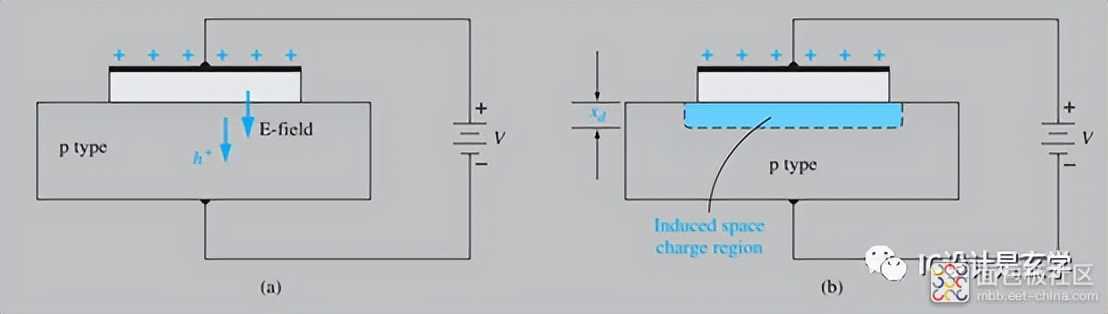

MOS结构如下图所示:

MOS电容可以等效为氧化层电容和耗尽层电容的串联,氧化层电容为COX,耗尽层电容为CS,降落在氧化层上的电压为VOX,降落在耗尽层上的电容为VS,氧化层电容感应出的电荷为QOX,耗尽层电容感应出的电荷为QS。

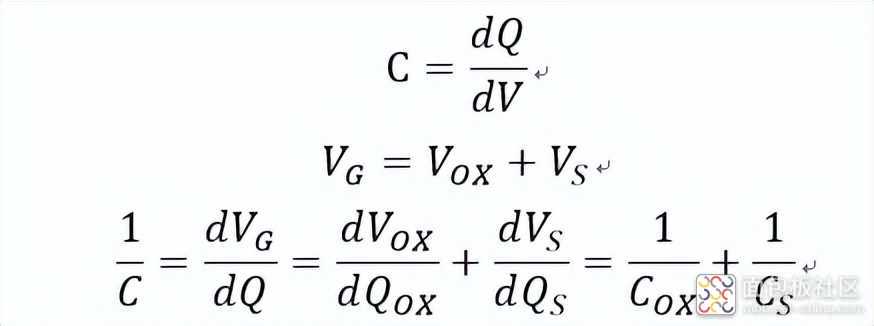

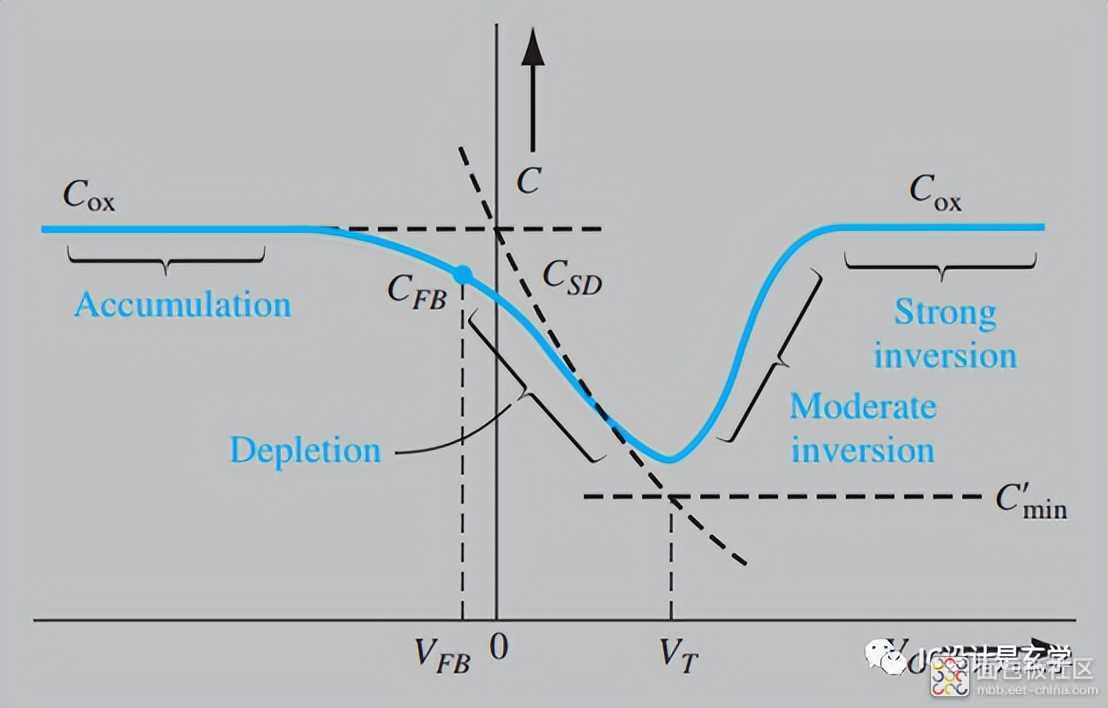

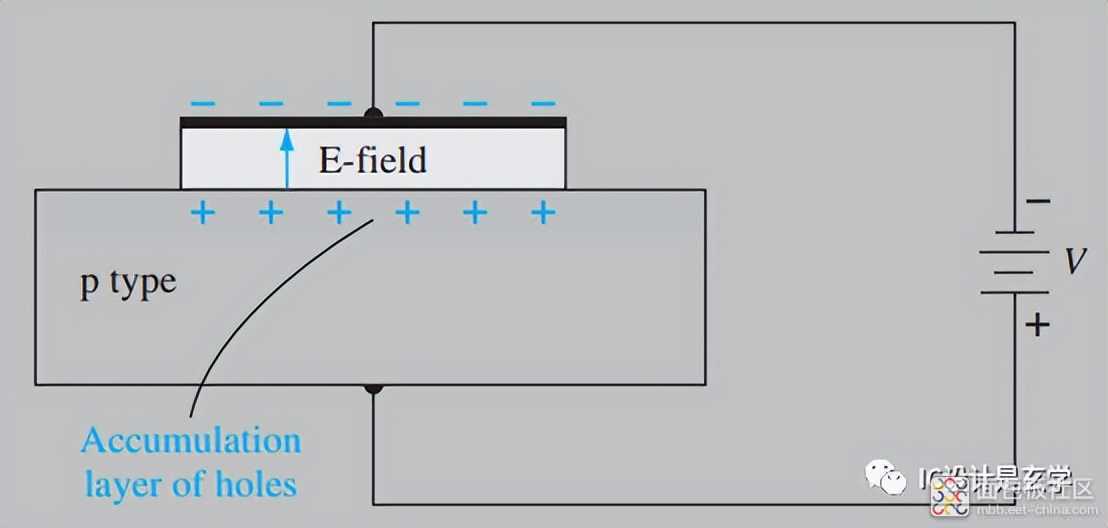

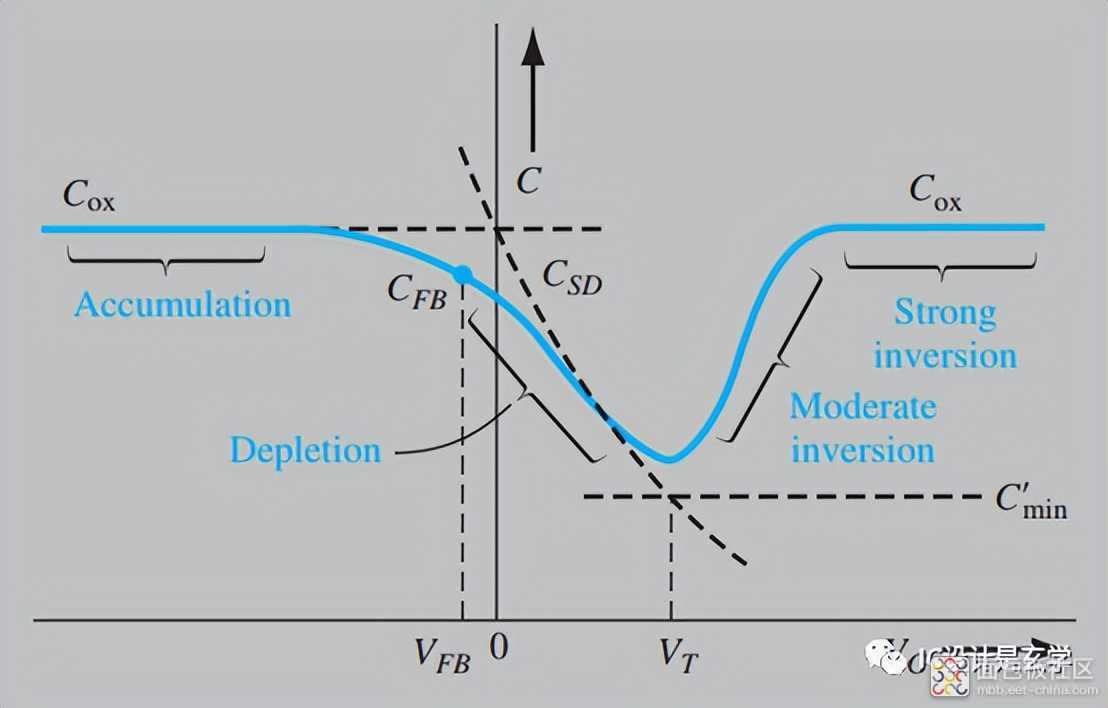

NMOS两端加负压后,金属极板带负电荷,所以在半导体一侧(对于NMOS结构半导体一侧是p-sub,下文用p-sub来代表半导体一侧)就会感应出正电荷,由于p-sub中多子是空穴,所以在p-sub顶端就会感应出多子空穴,此过程称为多子积累,这样电压VG的变化只会在氧化层两端感应出相应的电荷,所以MOS电容就是氧化层电容。氧化层电容的容值为:

在正电压比较小时(反型前),在栅极感应出正电荷,在加正压后,电场方向由栅指向p-sub,所以氧化层下面的空穴会被排斥如图4(a)所示,所以在氧化层下面会出现空间电荷区,这个电荷区是带负电的。随着电压的增大,空间电荷区逐渐变宽。这时表现出来的就是氧化层电容和空间电荷区电容的串联。所以,随着MOS两端电压的增大,耗尽层逐渐变宽,MOS电容可由下式决定

随着电压的继续增大,开始出现反型层电荷,这时p-sub的负电荷来自两部分一部分来自p-sub空间电荷区的展宽,另一部分来自p-sub顶端的反型层电荷,随着电压的增大,空间电荷区增加,空间电荷区的增加导致电容减小,同时反型层电荷也在增加,而反型层电荷的增加会导致电容变大,随着外加电压VG的增加,反型层电荷所占的比重越来越大,所以在弱反型阶段,MOS电容是一个先减小后增大的过程。

随着电压的继续增大,出现强反型,此时空间电荷区达到最大,此时半导体p-sub一侧的负电荷基本都由反型层电荷提供,所以此时的电容就是氧化层电容。所以强反型以后,MOS电容基本不变,强反型MOSC-V特性如下:

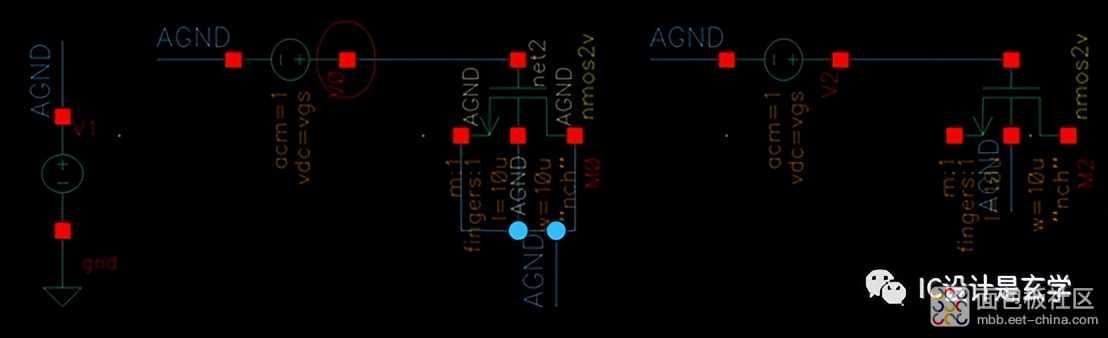

所以最终C-V特性如下图所示。

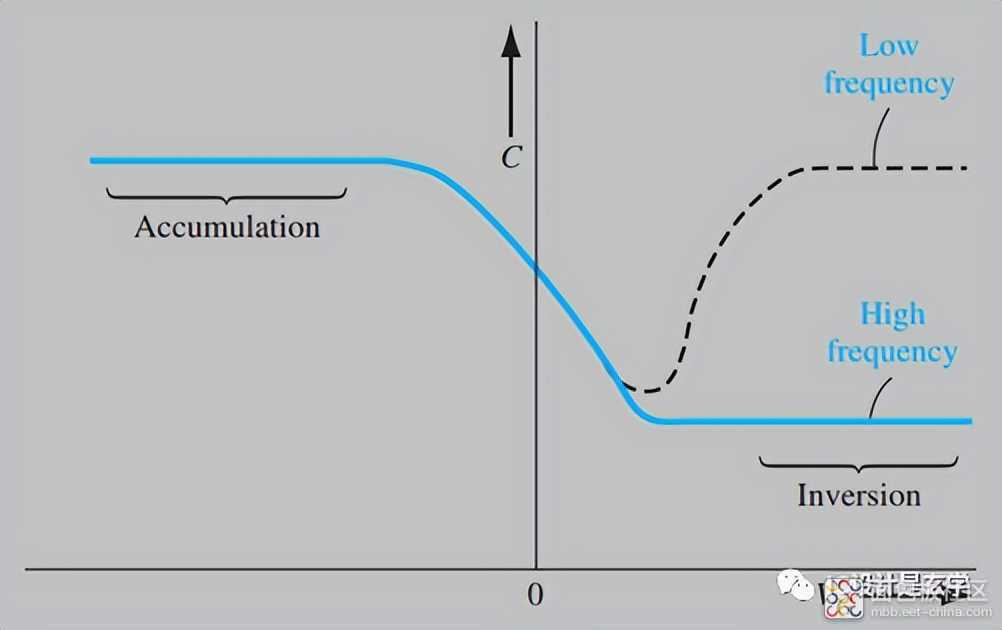

在MOS两端加负压和小的正压时(反型前),p-sub处在积累和耗尽状态,MOS高频和低频C-V特性是相同的,因为积累是电容下极板产生空穴,而空穴是多子,数量很多,所以能够跟得上高频信号的变化。在耗尽情况下,p-sub感应出空间电荷区,空间电荷区的负电荷是由不可动的受主杂质提供,这与低频情况下是一样的,所以在MOS在反型前,高低频C-V特性一致。

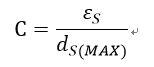

当在高频情况下,在MOS反型时,由于反型层电荷的产生不是一个很快的过程,所以跟不上高频信号的变化,所以反型层电荷并不贡献电容。同时在强反型时,耗尽层厚度达到最大值,当高频信号变化时,耗尽层厚度会产生轻微的变化来响应高频信号,所以在高频情况下强反型时MOS C-V电容只有耗尽层贡献。表达式如下:

在p-sub内部,载流子的产生与复合一直在发生并处于动态平衡中,在MOS加正压开始产生反型层电荷时,由于在p-sub和氧化层附近有很强的电场,所以在载流子产生时,电子就被电场扫到p-sub顶端(氧化层底端),这就是反型层电荷的来源。那么电子和空穴是成对产生的,电子被电场扫到p-sub顶端(氧化层底端),剩余的空穴去哪里了呢?空穴也会被电场向下排斥,最终这些空穴会被电源上的电子所复合。

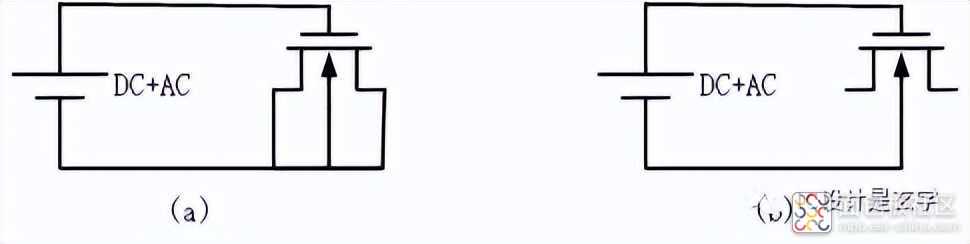

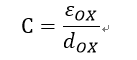

NMOS电容在电路中当作电容应用时,一般都是D,S,B都接地,而不是只有B接地,为什么?

/4

/4