向先进封装的转变使芯片制造商能够满足用于高性能计算、AI和其他用途的不断增长的带宽、时钟速度和功率密度的需求。这种改变通过分散芯片来缓解热问题,但它使热分析复杂化,因为一个芯片上的热点会影响相邻芯片的热分布。在模块中,芯片之间的互连速度也比在单个SoC慢。

西门子数字工业软件公司电子和半导体行业负责人John Parry表示:“在出现多核等技术之前,一个芯片的功率最高可达每平方厘米150瓦,作为一个单点热源,可以向周围散发热量,所以功率密度可以较高;但是如果在一个芯片周围放了其他芯片,它们会互相加热,这种情况下每个芯片无法达到最高的功率级别,因为现在面临的热问题更加艰巨。”

这也是3D-IC堆叠技术迟迟无法进入市场的主要原因之一。虽然从能效和集成的角度来看,这个概念是有意义的(并且在3D NAND和HBM中工作得很好),但如果把逻辑考虑在内,那就是另一回事了。逻辑芯片产生热量,逻辑越密集、利用率越高,热量就越大。这使得逻辑堆叠十分罕见,也解释了2.5D倒装芯片BGA和fan-out设计流行的原因。

选择正确的封装

设计师需要选择最好的封装,并将芯片集成其中,这对性能至关重要。组件、硅、TSV、铜柱等,都有不同的热膨胀系数(thermal coefficients of expansion,简称TCE),影响封装良率和长期的可靠性。

Rambus研究员、杰出的发明家StevenWoo表示:“一般来说,如果长时间不使用某个组件,关掉它可能会比较好。但如果以很高的频率去开关(如每秒100次),可能会遇到热循环问题。PCB、焊锡球、硅都以不同的速度膨胀和收缩。因此,从封装角落看到热循环失败是很常见的,如焊锡球可能会破裂。”

目前流行的带有CPU和HBM的倒装BGA封装约为2500 mm2。OntoInnovation软件产品管理主管Mike McIntyre表示:“我们看到一个大die可能会变成四五个小die。所以总体而言,面积是会变大的,因为小die之间也要有I/O实现相互通信,还要有空间去散热。根据应用的不同,这样做可能会有所帮助,但从另一个角度看,小die之间的通信变得复杂了(单个die可以通过内部总线进行通信)。”

最终,它变成了一个需要一系列复杂权衡的系统挑战,只有在系统级别才能处理。FraunhoferIIS自适应系统工程部高级系统集成小组组长Andy Heinig表示:“我们可以通过先进的封装实现很多新东西,但现在的设计要复杂得多。当die之间紧密互联时,相互之间会产生很多影响。我们必须检查流程、电源分配等,这使得设计变得非常困难。”

事实上,有些设备非常复杂,很难轻易地更换组件,只能为特定领域的应用定制这些设备。这就是为什么许多先进的封装产品都用于较大体量或价格较高的组件,如服务器芯片。

chiplet模块仿真与测试研究进展

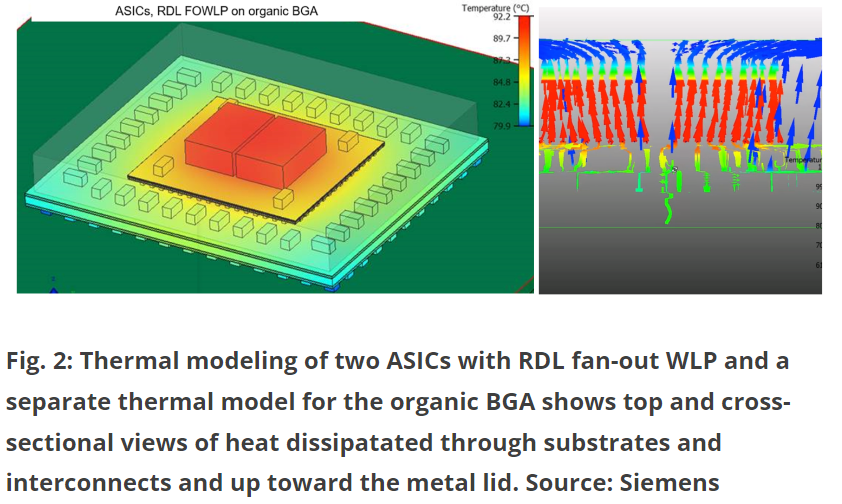

尽管如此,工程师们正在寻找新的方法,在封装模块之前对封装的可靠性进行热分析。例如,西门子提供了一个基于双ASIC模块的例子,该模块包含一个扇出RDL(Re-distributed layer,重布线层),安装在BGA封装中的多层有机基板上。它使用了两种模型,一个是基于RDL的WLP,另一个是多层有机衬底BGA。这些封装模型可以在导入EDA信息之前被参数化,包括基板层stack-up和BGA,并可以使能早期的材料评估和die placement。导入EDA数据后,对于每个模型,材料图可以对各层铜分布进行详细的热描述。最后的散热模拟考虑了除金属盖、TIM和底部填充材料外的所有材料,如下图所示。

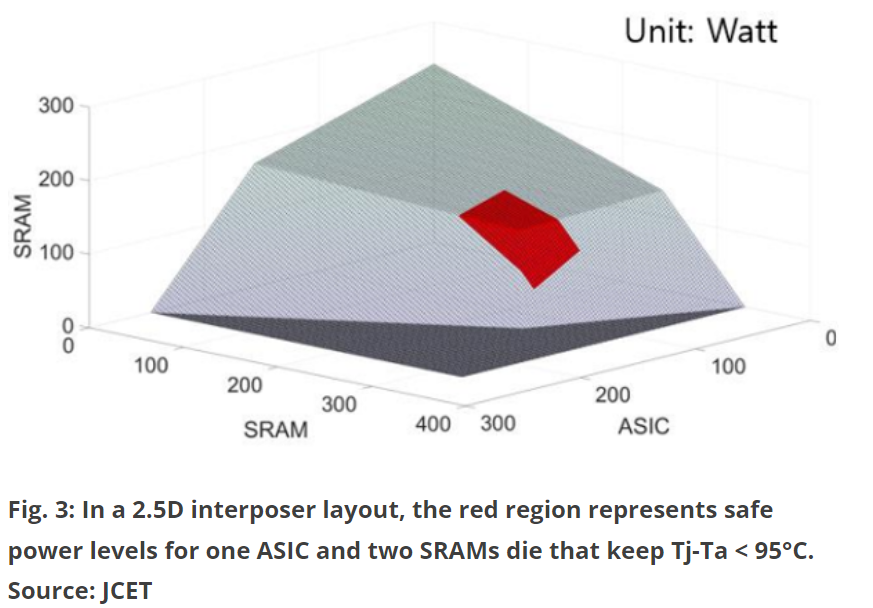

长电科技市场总监Eric Ouyang与工程师们比较了包含一个ASIC和两个SRAM的MCM(multichipmodule)、2.5D插入器、3D堆叠die以及单芯片之间的热性能。为了保证公平,必须在各种情况下保持服务器环境、散热器、真空室与TIMs相同。结果显示,在热性能方面,2.5D和MCM优于3D芯片和单芯片。

Ouyang与其同事设计了一个功率图,可用于早期模块设计,确定不同芯片的输入功率水平和设定的结温(芯片内PN结温度)能否可靠地结合在一起。如图所示,图中的红色区域为每个芯片满足可靠性标准的功率范围。

Ouyang解释说,在设计过程中,电路设计师可能了解模块中各种芯片的功率级别,但却不清楚功率级别是否在可靠范围内。该图确定了一个chiplet系统中多达三个chiplet的安全电源区域。该团队开发了一种用于更多chiplet的自动功率计算器。

量化热电阻

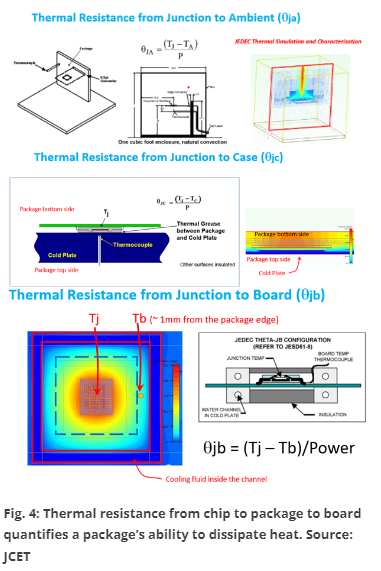

热量如何通过芯片、电路板、胶水、TIM或封装盖传播是很容易理解的。已经有标准方法来跟踪每个接口的温度和电阻值,这是一个温度差和功率的函数。

Ouyang表示:“热路径由三个关键值来量化——芯片到环境的热阻,芯片到封装外壳的热阻,以及芯片到PCB的热阻。”他指出,长电科技的客户至少需要这三个热阻值,用于系统设计。

详细的热模拟是探索材料和配置选项的最廉价的方法。Ouyang解释道:“芯片的模拟通常会识别一个或多个热点,我们可以在热点下方的基板中添加铜来帮助散热,或者改变封装的材料,添加一个散热器。对于多个模组,我们可以改变配置或考虑新的方法来防止热串扰。”

在模拟之后,封装厂商要进行实验设计(DOE),以得出最终的封装配置。但是由于DOE要使用专门设计的测试车辆,耗时且昂贵,所以在此之前需要先做仿真。

选择TIM

在封装中,超过90%的热量通过封装从芯片顶部散热,通常是带垂直翅片的阳极氧化铝散热器。在芯片和封装之间放置高导热的热界面材料(Thermal interface material, 简称TIM),以帮助散发热量。用于CPU的新一代TIM包括金属薄片合金(如铟、锡)和银烧结锡,它们的导电性能分别为60W/m-K和50W/m-K。

随着企业从大型SoC过渡到chiplet模块,我们将需要更多有不同性能和厚度的TIM。

对于高密度系统,芯片和封装之间TIM的热电阻对封装模块的整体热电阻有更大的影响,Amkor 研发高级总监YoungDo Kweon表示:“功耗正在急剧增加,特别是在逻辑方面,因此我们要保持低结温,以确保芯片可靠运行。”他补充说,虽然TIM供应商为其材料提供热电阻值,但实际上,从芯片到封装的热电阻受到封装过程的影响,包括芯片和TIM之间的粘结质量和接触面积。

孔隙是一个特别的问题。Parry表示:“材料在封装中的表现是一个相当大的挑战。我们已经知道了粘合剂或胶水的材料属性,以及材料与表面的接触方式会影响材料呈现的整体热阻,即接触电阻。如果有些地方没有被胶水填充,就会对热流造成额外的阻力。”

处理热量的不同方法

芯片制造商正在扩大解决热约束问题的范围。Keysight Technologies的内存解决方案项目经理Randy White 表示:“如果把die的面积变小(如变为四分之一),但封装不变,外部封装的连接线进入die,可能会出现一些信号完整性差异。由于电线更长,电感更大,所以die的面积缩小后速度就会加快。如何在一个足够小的空间里散热是另一个需要研究的关键问题。”

这导致了在前沿键合技术方面的重大投资,目前来看重点是混合键合。Woo表示:“如果有两个芯片,芯片之间有空气间隙,这不是最佳的散热方式。我们可以用一些材料填充空气间隙,但即使这样也不如直接与芯片接触。因此,混合直接键合是人们正在研究的一件事。”

但混合键合技术成本高昂,可能仍局限于高性能处理器类型的应用,TSMC是目前仅有的几家提供该技术的公司之一。尽管如此,在CMOS芯片上结合光电技术或在芯片上结合氮化镓技术的前景仍然是巨大的。

结论

先进封装背后的最初想法是,它将像乐高积木一样工作——在不同工艺节点上开发的chiplet可以封装在一起,从而减少热问题。但这是需要付出代价的,从性能和功耗的角度来看,信号传输的距离很重要,always-on电路或者需要时不时关闭的电路都会影响热性能。仅仅将一个die分解成多个chiplet以获得更好的良量和灵活性并没有看起来那么简单,封装中的每一个互连都必须优化,热点不再局限于单个芯片。

早期的建模工具可以用来确定chiplet的不同组合,这为复杂模块的设计人员提供了很大的帮助。在这个功率密度不断增加的时代,热模拟和新TIM的引入仍然是必不可少的。

原文链接:

https://semiengineering.com/keeping-ic-packages-cool/

本文由编辑推荐,原出处:https://www.eet-china.com/mp/a158393.html

/5

/5