随着科技和时代的发展,PCB设计和组件都变得更快更小。换句话说,也就是需要和要求都变高了。了解PCB设计的关键网络和走线、阻抗及PCB如何影响信号性能至关重要。

随着电路的速度日益提高,CHz范围内的信号很常见。因此,受控的走线阻抗对信号完整性和电路板的性能起着重要作用。

一、PCB阻抗控制是什么?

PCB阻抗控制也就是对走线阻抗进行控制,这个阻抗也被叫做受控阻抗。受控阻抗是由 PCB 走线及其相关参考平面形成的传输线的特性阻抗。当高频信号在 PCB 传输线上传播时,它是相关的。受控阻抗对于解决信号完整性问题很重要,信号完整性问题是信号的无失真传播。

电路的阻抗由 PCB 的物理尺寸和介电材料决定。它以欧姆(Ω)为单位进行测量。需要控制阻抗的PCB传输线类型有单端微带、单端带状线、微带差分对、带状线差分对、嵌入式微带和共面(单端和差分)。

二、为什么要对 PCB 阻抗进行控制?

通常,你需要控制用于高速数字应用的PCB阻抗,例如射频通信、电信、使用100MHz以上信号频率的计算、高速信号处理以及高质量模拟视频(例如DDR、HDMI、千兆以太网),ETC。

在高频下,PCB上的信号走线就像传输线,在信号走线轨迹上的每个点都有阻抗。如果这个阻抗从一个点到下一个点变化,就会有一个信号反射,其幅度将取决于两个阻抗之间的差异。差异越大,反射越大。这种反射将沿信号的相反方向传播,这意味着反射信号将叠加在主信号上,结果,原始信号会失真。

原本要从发送端发送的信号一旦到达接收端就会发生变化。失真可能很大,以至于信号可能无法执行所需的功能。因此,要获得不失真的信号传输,PCB信号走线必须具有统一的受控阻抗,以最大限度地减少由反射引起的信号失真。

PCB上的均匀传输线具有确定的走线宽度和高度,并且与返回路径导体的距离一致,通常是与信号走线有一定距离的平面。

三、影响 PCB 受控阻抗的因素

影响 PCB 阻抗容差的因素包括材料的树脂含量百分比、树脂的 Dk 值和所用玻璃布的类型,以及其他物理 PCB 容差,如走线顶部和底部的走线高度和宽度。

当需要制造的PCB具有一定公差范围内的正确图案尺寸和位置。你必须确保制造商提供蚀刻特征的正确尺寸、位置和公差。否则,你的 PCB板 将每个都不一样,这样会使调试与性能相关的问题变得非常困难,

四、为什么指定板的电介质,而不是确定 IC是好的?

走线的阻抗也由板上使用的 PCB 材料决定。材料的介电常数和基于某些参数的预期阻抗称为受控电介质,如果你擅长数学,可以采用受控介电方法来控制所需的阻抗。进行计算后,你可以指定晶圆厂铜层之间所需的介电空间,然后,用正确的走线和空间布置走线。

在这种情况下,请求受控阻抗板而不是受控介电板可能会更好。对于受控电介质,你是否指定了要使用的玻璃布类型?材料的树脂百分比?如果没有,那么你无法确定制造商使用的是什么。此外,你是否确保走线宽度在公差范围内?如果你要求使用受控介电板,则负担落在自己身上。

那如何设计阻抗可控硅的PCB板?看下文。

五、如何设计阻抗可控的PCB板?

你应该遵循下面提到的受控阻抗布线策略来设计PCB∶

大多数时候,电气工程师会指定哪些信号网络需要特定的受控阻抗。但是,如果不这样做,设计人员应查看集成电路的数据表以确定哪些信号需要受控阻抗。

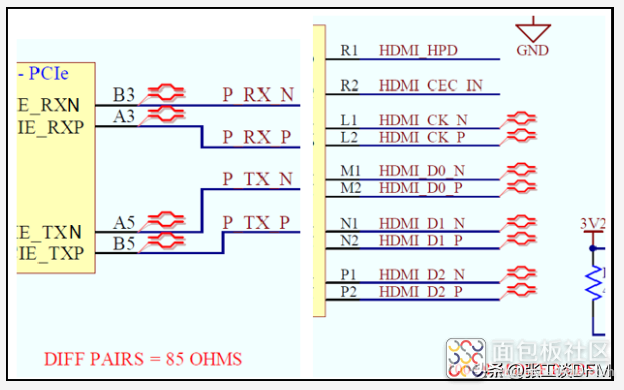

数据表通常为每组信号及其阻抗值提供详细指南。间距规则和路由特定信号的层的信息也可能出现在数据表或应用笔记中。DDR走线、HDMI走线、千兆以太网走线、RF 信号是受控阻抗走线的一些示例。

电路板的设计始于设计工程师设计电路原理图。

- 工程师必须在原理图中指定受控阻抗信号,并将特定网络分类为差分对(1002、902或852)或单端网络(402、502、552、602或752)。

- 在原理图中差分对信号的网络名称之后添加N 或P极性指示是一种很好的设计。

- 工程师还应在原理图或单独的“自述”文件中指定布局设计人员应遵循的特定受控阻抗布局设计指南(如果有)。

PCB 迹线由其厚度、高度、宽度和蚀刻迹线的 PCB 材料的介电常数(Er)定义。在设计受控阻抗 PCB时,必须注意这些参数。你可以向制造商提供层数、特定层上的阻抗走线值(第3层502、1002)和PCB设计材料。

制造商为你提供垦层,其中提到了每层上的走线宽度、层数、叠层中每个电介质的厚度、走线厚度和PCB材料。他还通过计算需要阻抗控制的迹线的可行厚度、宽度和高度来处理受控阻抗要求。记住以下规则以了解阻抗如何取决于尺寸∶

- 阻抗与走线宽度和走线厚度成反比。

- 阻抗与层压板高度成正比,与层压板介电常数(Er)的平方根成反比。

受控阻抗走线宽度必须与板上的其余走线区分开来。它允许 PCB制造商快速识别它们,并在必要时对走线宽度进行适当的更改,以实现特定的阻抗。例如,如果你需要一条 5mil 的走线来实现 50Ω的阻抗,并且如果你还路由了其他宽度为5mil 的信号,那么PCB制造商将无法确定哪些是受控阻抗走线。因此,你应该使502阻抗走线5.1mil 或 4.9mil 宽。

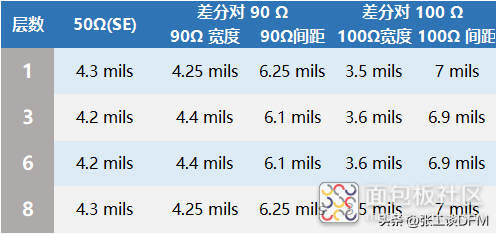

下表显示了不同层上受控阻抗的走线宽度和间距。非阻抗信号走线不应使用3.5、3.6、4.2、4.25 和4.3mil的走线宽度。

高速差分对信号走线需要彼此平行布线,并且它们之间的间距恒定。需要特定的走线宽度和间距来计算特定的差分阻抗。差分对需要对称布线。你应该尽量减少指定间距因焊盘或端部而扩大的区域。

为减少串扰,黑白走线间距应为3W或至少为2W。请注意,这个规则不适用于间距b/w差分对。

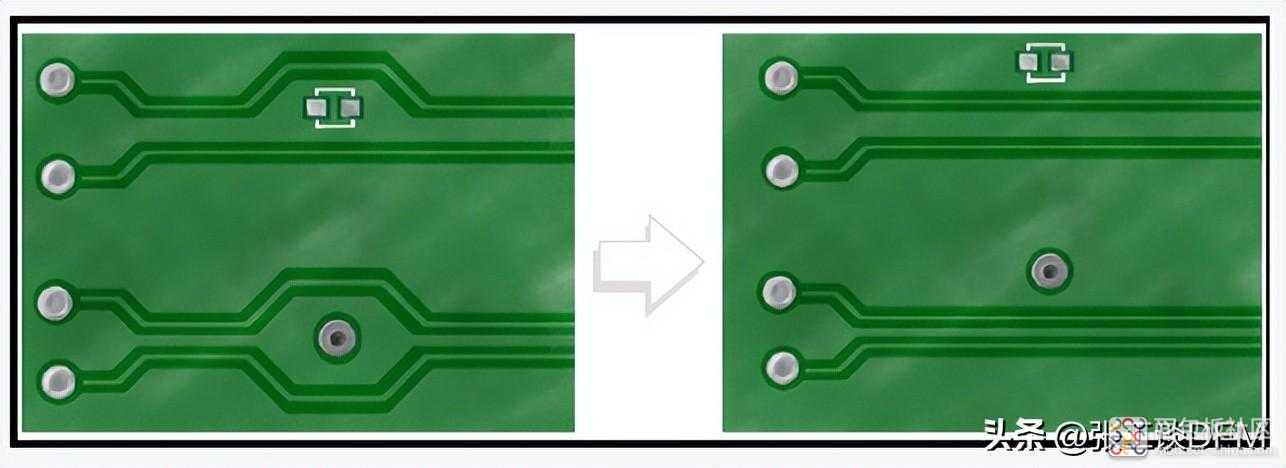

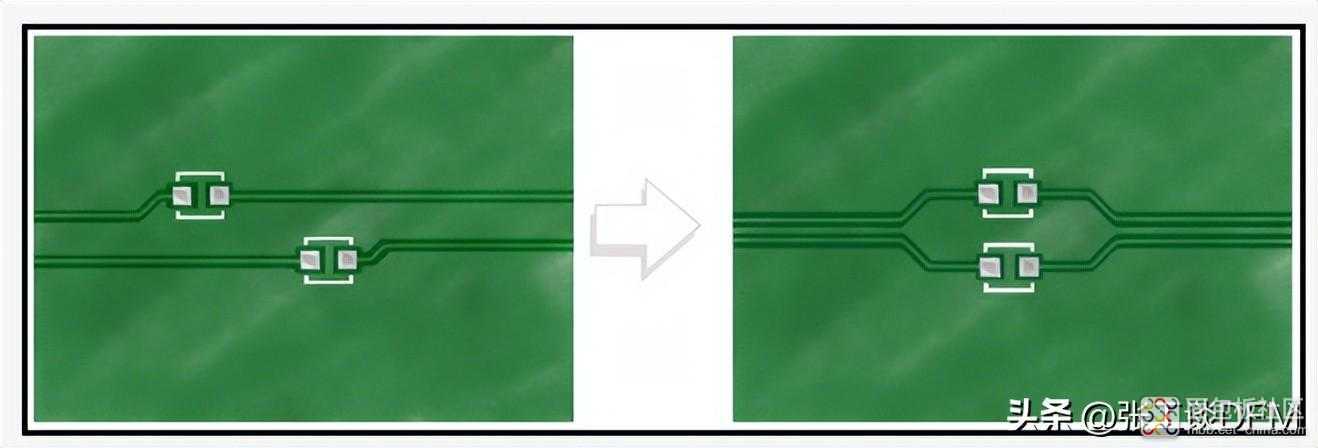

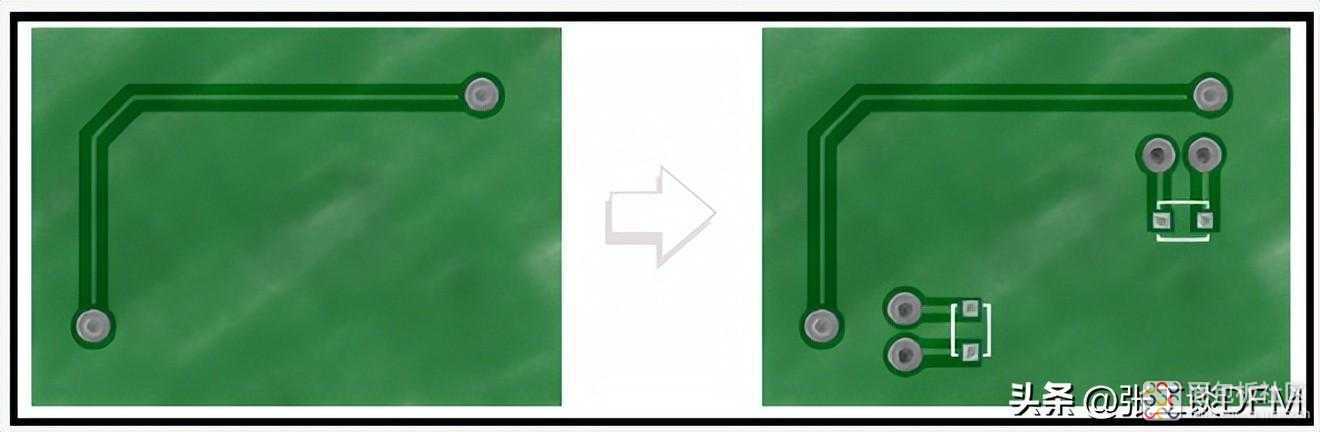

组件或过孔不应放置在差分对之间,即使信号围绕它们对称布线,组件和过孔会造成阻抗不连续,并可能导致信号完整件问题。

- 对于高速信号,一个差分对与相邻差分对之间的间距不应小于走线宽度的五倍(5W)。你还应该与任何其他信号保持30密耳的距离。

- 对于时钟或周期性信号,你应该将保持距离增加到50mil以确保适当的隔离。

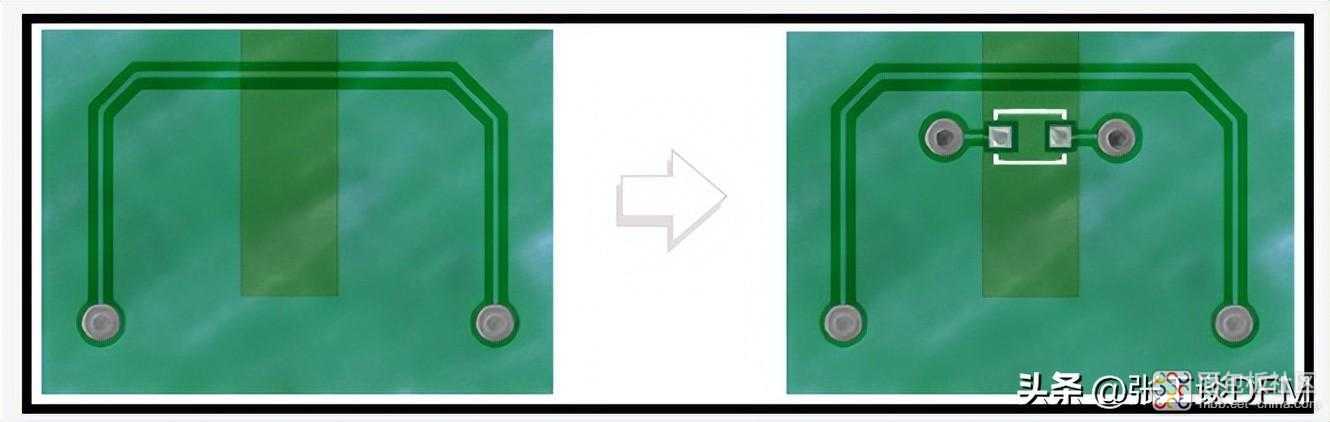

如果高速差分对需要串联耦合电容,则需要对称放置,如下图所示。电容会产生阻抗不连续性,因此将它们对称放置将减少信号中的不连续性。

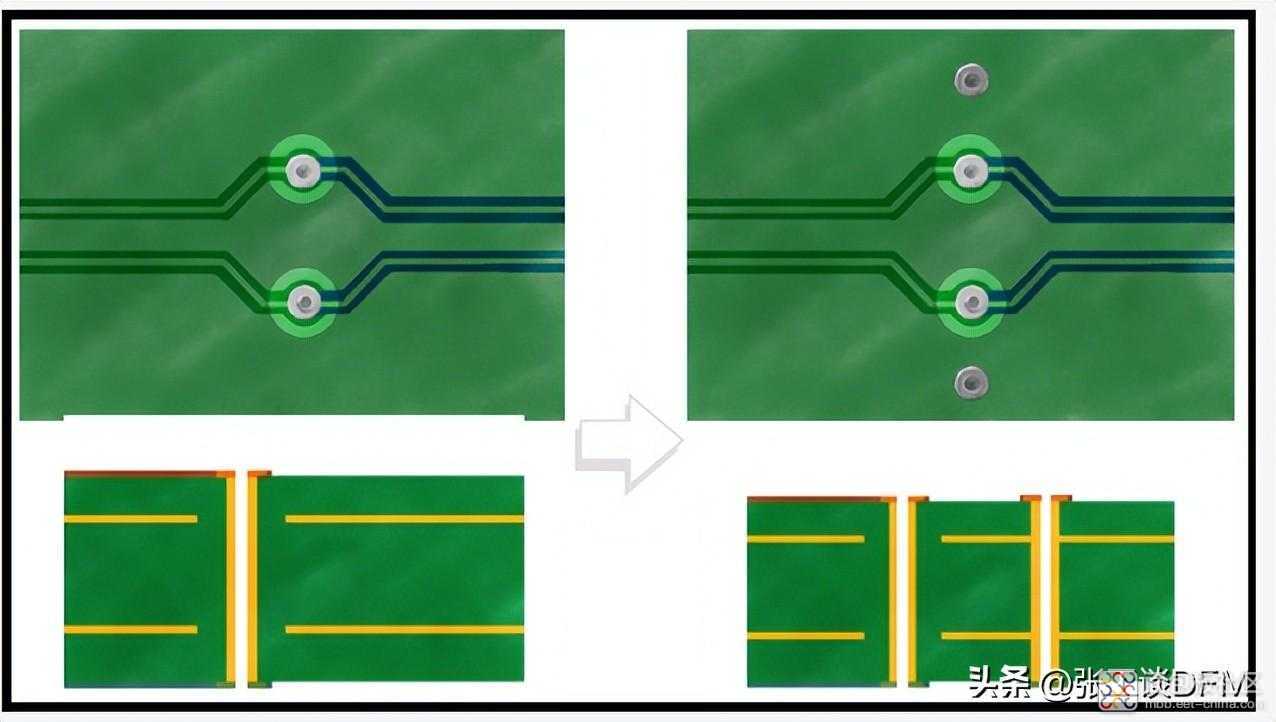

你应尽量减少差分对过孔的使用,如果确实是这样放置它们,它们需要对称以尽量减少不连续性。

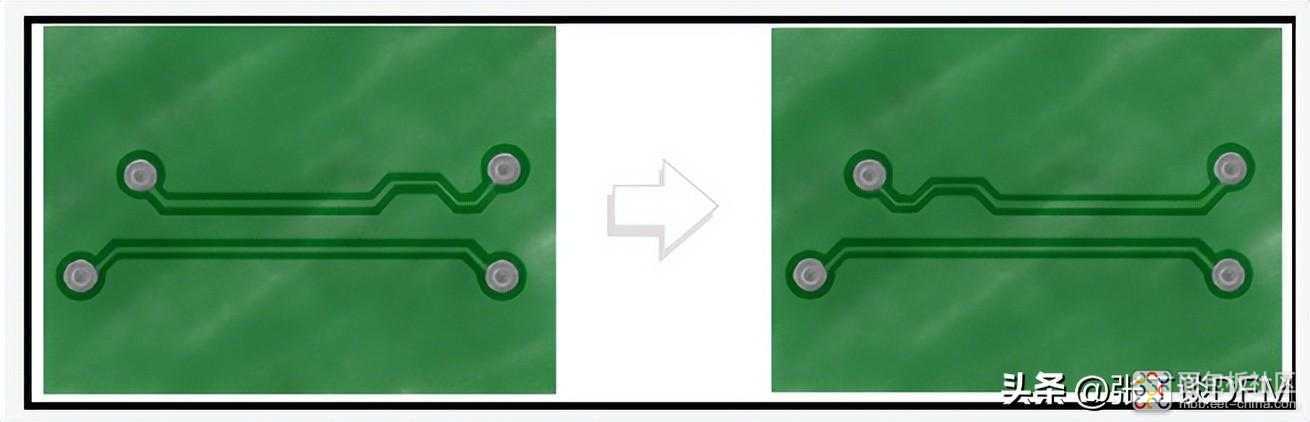

如果不同走线上的信号速度相同,长度匹配可以实现传播延迟匹配。当一组高速信号一起传输并预计同时到达其他目的地(在指定的失配容限内)时,可能需要长度匹配。

形成差分对的走线长度需要非常紧密地匹配,否则,这将导致不可接受的延迟偏差(正信号和负信号之间的不匹配)。

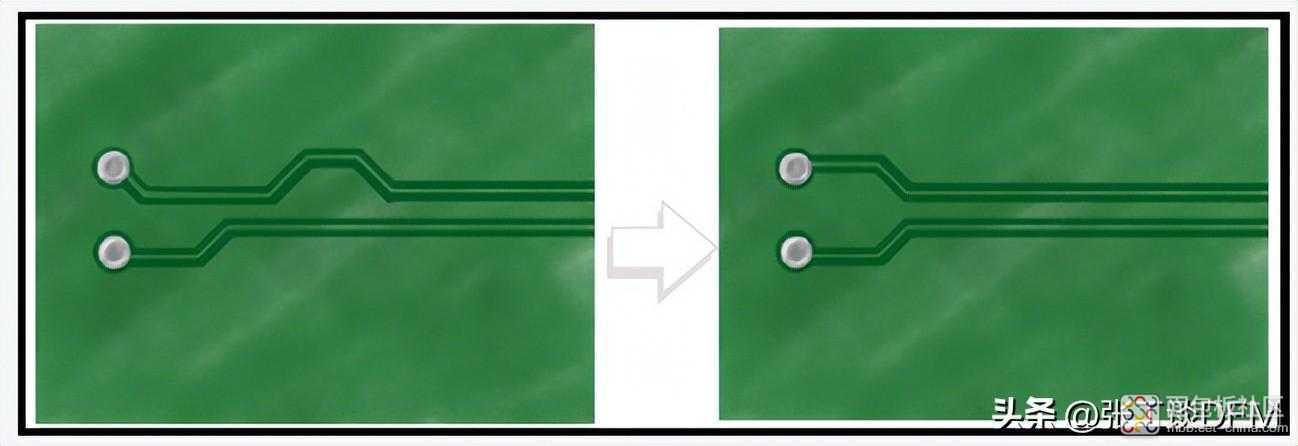

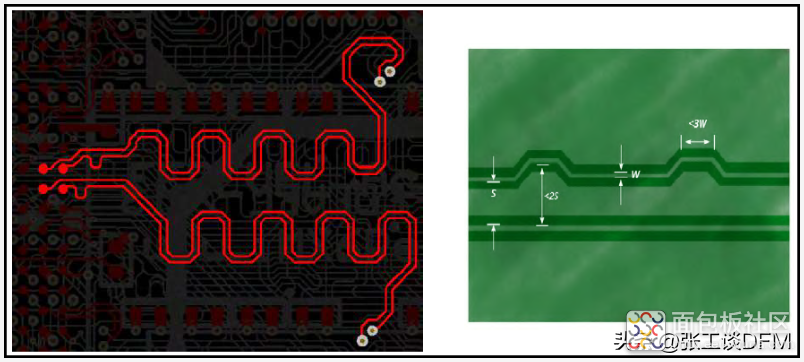

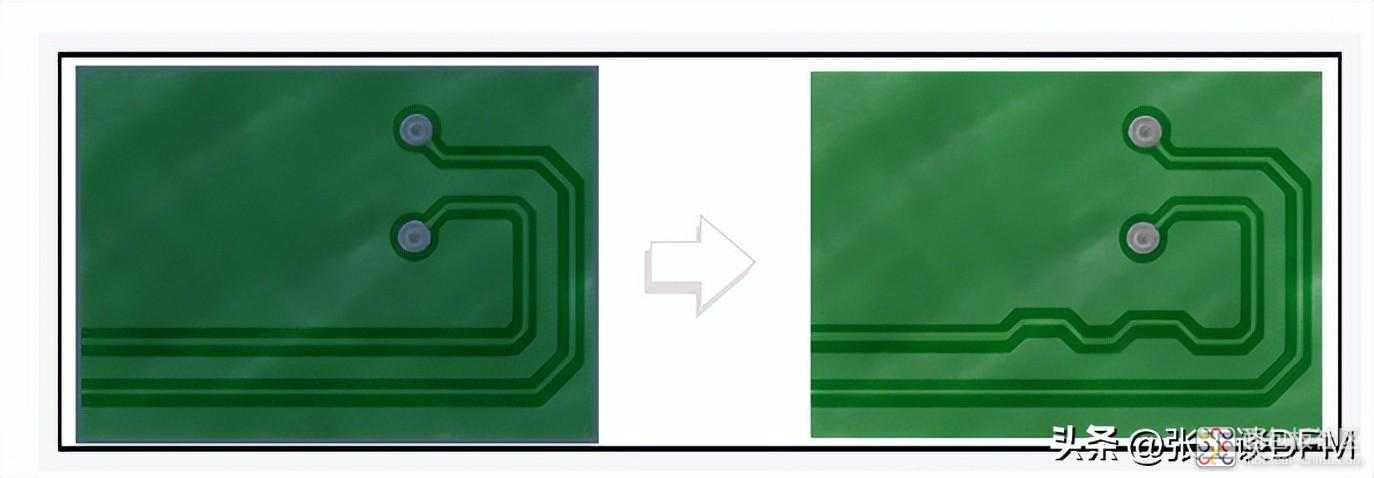

长度的不匹配需要通过在较短的迹线中使用蛇形线来补偿。需要仔细选择蛇形迹线的几何形状以减少阻抗不连续性。下图显示了理想蛇形走线的要求。

蛇形走线应尽可能靠近失配源。它确保尽快纠正失配。在下图中,你可以看到不匹配发生在左侧的一组过孔上,因此需要在左侧而不是右侧添加蛇形。

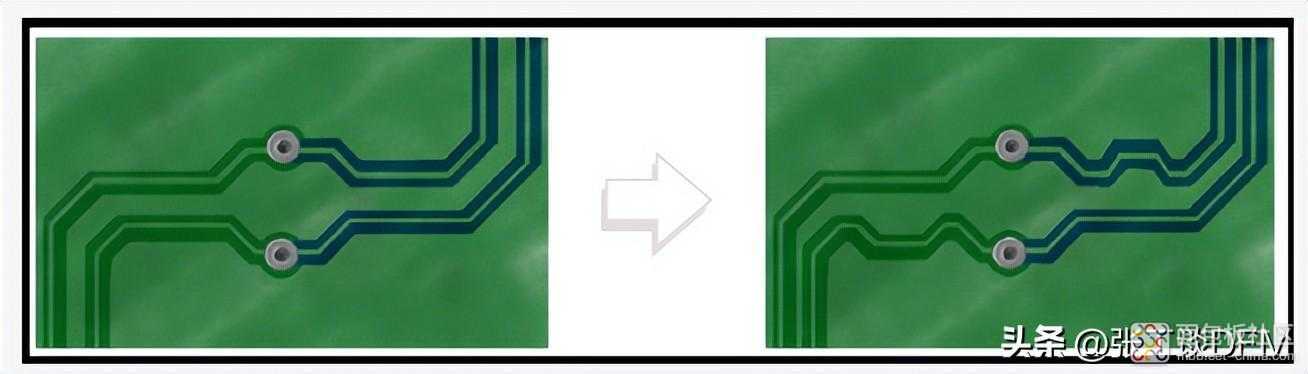

同样,弯曲会导致不匹配,使内部弯曲上的走线小于外部走线。因此,我们需要在靠近弯曲区域的地方添加蛇纹石,如果有一对有两个小于15毫米的弯曲,他们会相互补偿,因此不需要添加蛇纹石。

当差分对信号使用过孔从一层更改到另一层并且有弯曲时,需要单独匹配该对的每一段。蛇形线应放置在靠近弯曲处的较短走线上。你需要手动检查此违规行为,因为它不会在设计规则检查中被捕获,因为总信号的长度将紧密匹配。由于各层走线的信号速度可能不同,如果差分对信号需要长度匹配,建议在同一层布线。

所有高速信号都需要一个连续的参考平面用于信号的返回路径。不正确的信号返回路径是噪声耦合和EMl问题的最常见来源之一。高速信号的返回电流紧跟信号路径,而低速信号的返回电流采用可用的最短路径。通常,高速信号的返回路径设置在最靠近信号层的参考平面中。

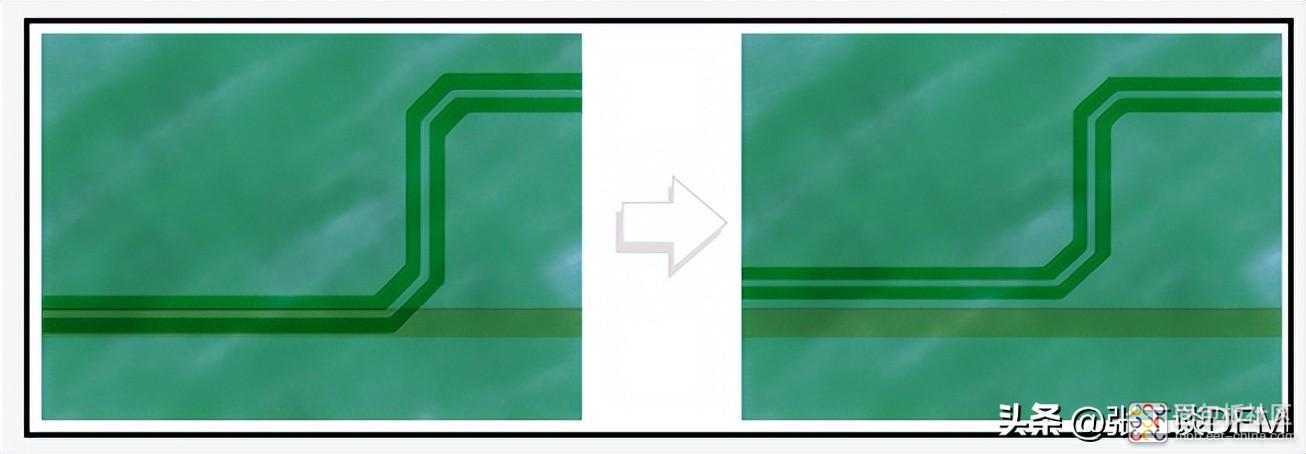

高速信号不应在分割平面上布线,因为返回路径将无法眼随走线。为了更好的信号完整性,你应该围绕分割平面布线。此外,请确保接地层在每侧至少是走线宽度的三倍(3W规则)。

如果需要在两个不同的参考平面上路由信号,则需要在两个参考平面之间放置一个拼接电容。电容需要连接到两个参考平面,并应靠近信号路径放置,以保持信号与返回路径之间的距离较小。电容允许返回电流从一个参考平面流向另一个参考平面,并最大限度地减少阻抗不连续性。拼接电容的一个好的值是在10nF和100nF之间。

应该避免在信号迹线下方的参考平面中出现分裂平面障碍物和槽。如果插槽是不可避免的,则应使用缝合过孔来最大限度地减少由分离的返回路径造成的问题。电容的两个引脚都应连接到接地层,并应放置在信号附近。

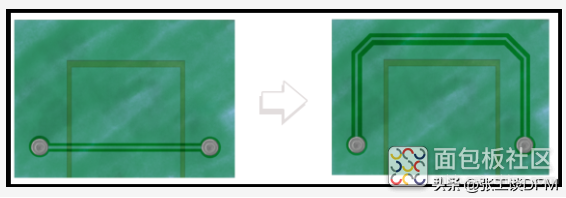

当过孔放置在一起时,它们会在参考平面中产生空隙。为了最大限度地减少这些大空隙,应该错开过孔以允许在过孔之间提供足够的平面馈电。错开过孔允许信号具有连续的返回路径。

最好使用接地平面作为参考。但是,如果将电源层用作参考层,则需要添加一个拼接电容,以允许信号将参考从地更改为电源层,然后再返回到地。应该在信号输入和输出点附近放置一个电容,并将一端连接到地面,另一端连接到申源网络。

如果高速差分对或单端信号切换层,则应在层更改过孔附近添加拼接过孔,这种做法还允许返回电流改变接地层。

六、PCB 受控阻抗设计

- 受控阻抗线应在 PCB 原理图中标出。

- 差分对走线长度应与信号上升/下降时间的20%容差相匹配。

- 应使用高数据频率连接器。

- 对于微带结构,在微带走线下方使用完整的接地。

- 对于带状线结构,在差分对的上方、下方和侧面使用接地或不间断电源。接地层和电源层提供返回电流路径,它还减少了EMI问题。

原文链接:

https://www.protoexpress.com/blog/controlled-impedance-really-matters/

转载文章麻烦备注来源:张工谈DFM

/2

/2