CMOS是名副其实的“表面工艺

首先,你的手机和电脑里面,有很多这样的电路板PCB,每个黑盒子

(传统的封装就是长这样)里面就是一块芯片:

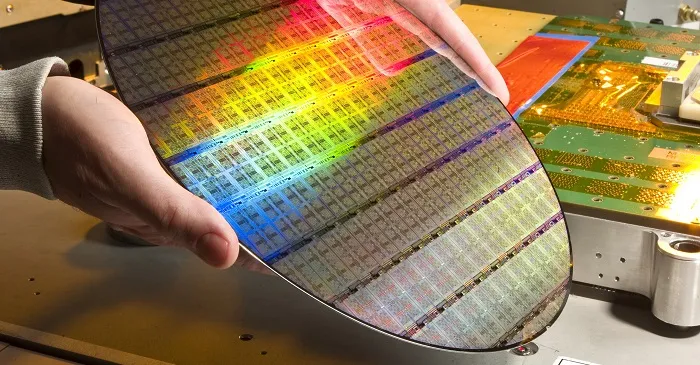

你以为的集成电路

(这里指CMOS)是这样的硅片wafer上面一块块切出来的(每一小块最终就被封装到了上面那种黑盒子里面了):

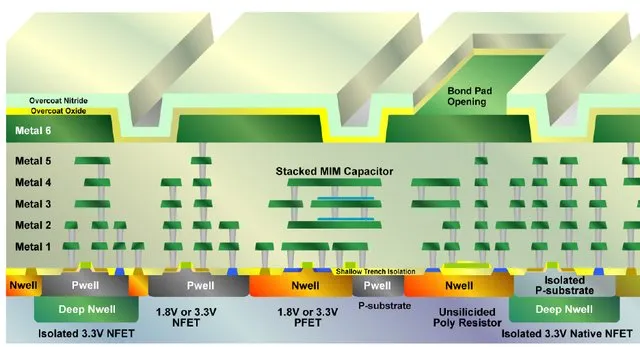

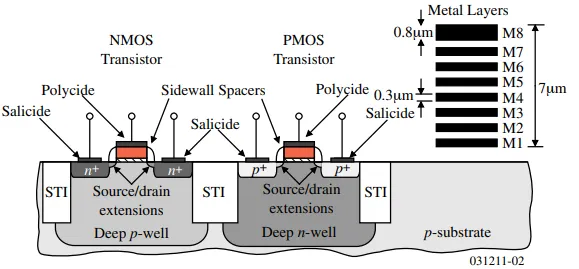

然后,你以为上面每一小块的die里面的器件长这样:

其实,一块wafer的厚度大概有700um(0.18um工艺最厚这样,当然你可以叫foundry打磨,最薄100um应该可以做到,当然这样wafer就很脆,后续加工很容易断裂),然后上面的厚度大概是:

所有的金属层加起来才7um。

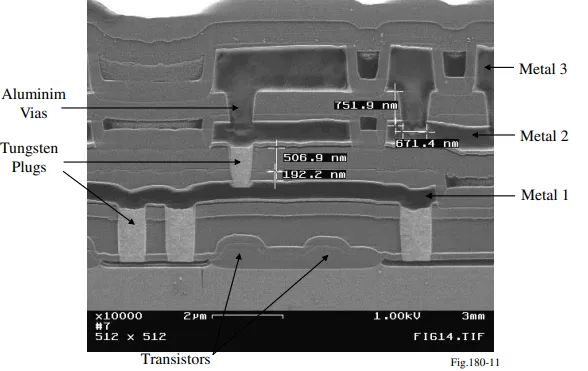

或者再看看显微镜

下的:

全部厚度加起来超过10um都很难。

最后归纳一下:10um VS 700um。大家对于“表面工艺”四个字有感觉了吗?

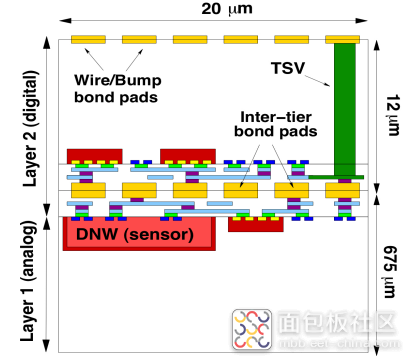

再给大家看个TSV的图,也就是两块wafer“脸贴脸”放在一起:

数字应该很直观了吧?

最后多说一句:大家都知道CMOS上表面需要不停的抛光打磨,那大家有没有想过下表面呢?其实没有特殊的要求时,foundry

不会管你的下表面。大多数时候,下表面都特别粗糙,反正没人看……

Reference:

- https://en.wikipedia.org/wiki/Wafer_(electronics)#:~:text=The%20size%20of%20wafers%20for,from%20100%E2%80%93450%20mm%20diameter.

- http://portal.unimap.edu.my/portal/page/portal30/Lecture%20Notes/KEJURUTERAAN_MIKROELEKTRONIK/Semester%202%20Sidang%20Akademik%2020172018/EMT%20367%20Microelectronic%20Fabrication/Lecture%20Notes/Lecture%204%20CMOS%20Well%20Technology_201718.pdf

- CMOS Processing Technology;

- http://pallen.ece.gatech.edu/Academic/ECE_4430/Summer_2004/DSMCMOSTech(2-UP).pdf

/3

/3