3W原则的概念

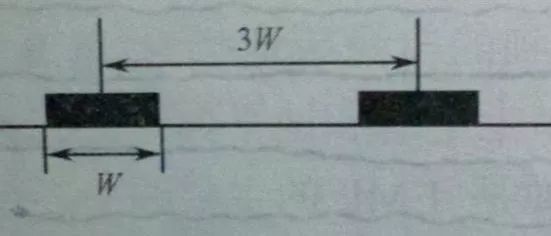

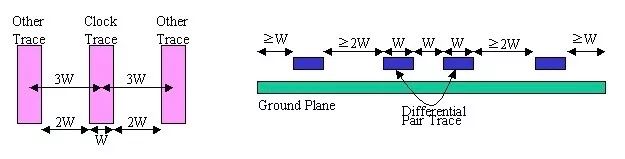

所以在时钟走线、差分线、视频、音频,复位线,以及其他系统关键电路等,多个高速信号线长距离走线的时,为了减少线与线之间的串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。如下图所示。

满足3W原则能使信号间的串扰减少70%,而满足10W则能使信号间的串扰减少近98%.

3W原则成立条件

3W原则虽然易记,但要强调一点,这个原则成立是有先前条件的。

从串扰成因的物理意义考量,要有效防止串扰,该间距与叠层高度、导线线宽相关。

对于四层板,走线与参考平面高度距离(5~10mils),3W是够了;

但兩层板,走线与参考层高度距离(45~55mils),3W对高速信号走线可能不够。

3W原则一般是在50欧姆特征阻抗传输线条件下成立。

3W原则是指多个高速信号线长距离走线的时候,其间距应该遵循3W原则,例如时钟线,差分线,视频、音频信号线,复位信号线及其他系统关键电路需要遵循3W原则,而并不是板上所有的布线都要强制符合3W原则。

吴川斌的博客,电子工程师之家

/5

/5