米尔科技的MYC_C7Z010_20核心板上板载有1GB DDR3 SDRAM内存,是由两片美光的DDR3颗粒组成,每个颗粒的数据总线宽度为16比特,一起组成32比特的总线宽度,内存是挂接到ZYNQ芯片的PS侧,最高速度可以跑到533MHz, 即1066Mbps的数据速率。下面就以测试DDR3内存为例Step BY Step初步体验下Zynq开发过程,软件环境为Vivado 2018.3和Xilinx SDK 2018.3版本。如没有安装软件的童鞋自行到赛灵思官网:https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/2018-3.html下载,需要注册一个帐号才能下载,具体安装过程和软件License文件网上很容易找到,这里就不再赘述了。(PS: 今天访问赛灵思官网发现Vivado工具已经刚发布了2019.2版本,我们试用体验还是使用Vivado2018.3版本)

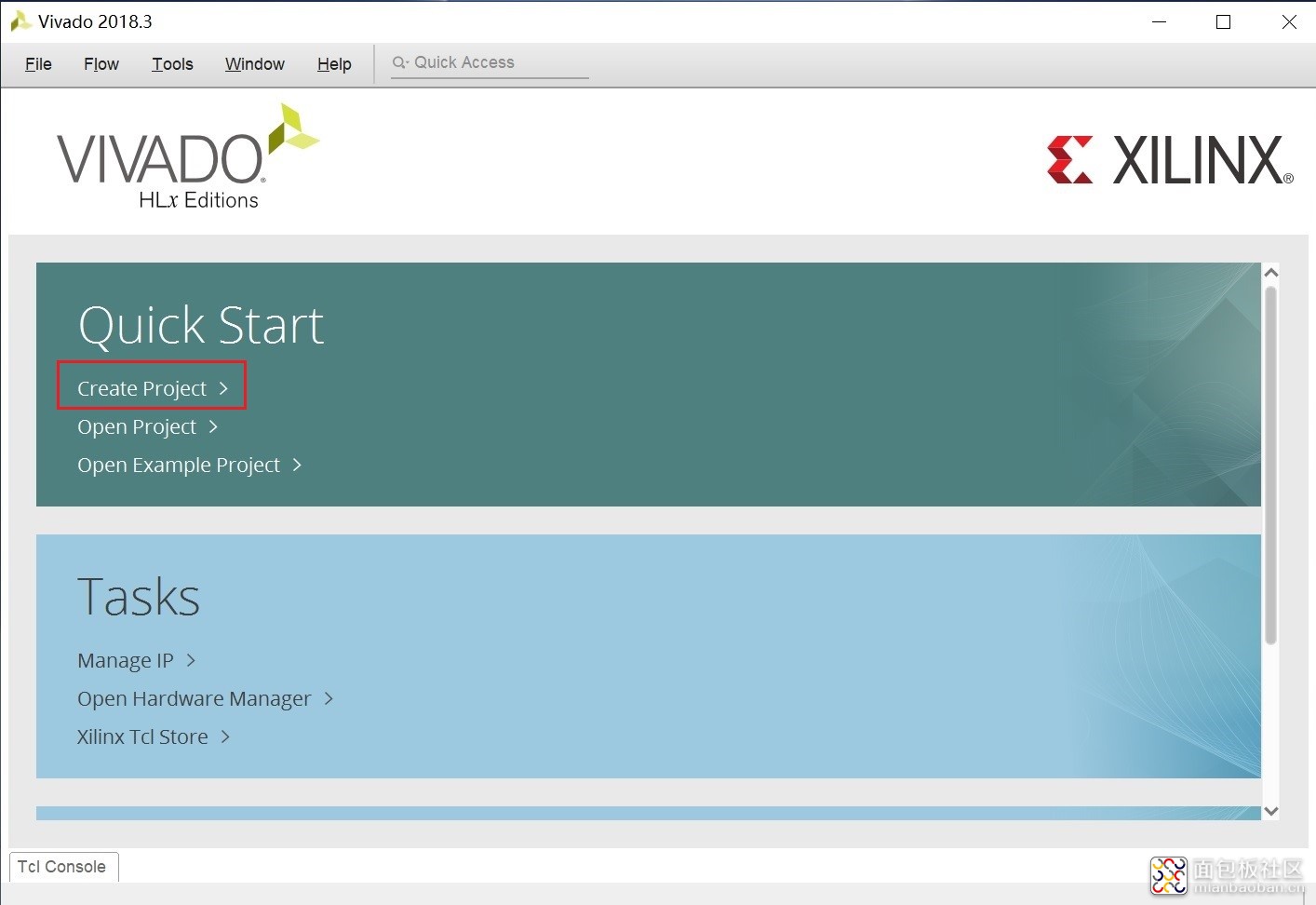

1、双击桌面Vivado2018.3图标打开软件,选择新建工程,如下图示:

2、按Next出现New Projec页面,填写工程名: ddr3_test, 选择一个工程目录,勾选上create project subdirectory,然后按Next,如下图示:

3、工程类型页面选择RTL Project,勾选上Do not specify sources atthis time,然后按Next,如下图示:

4、器件选择页面通过Package选择clg400, Speed选择-1过滤下,在Part内选择我们试用的MYD-C7Z010开发板对应的xc7z010clg400-1器件,然后按Next,如下图示:

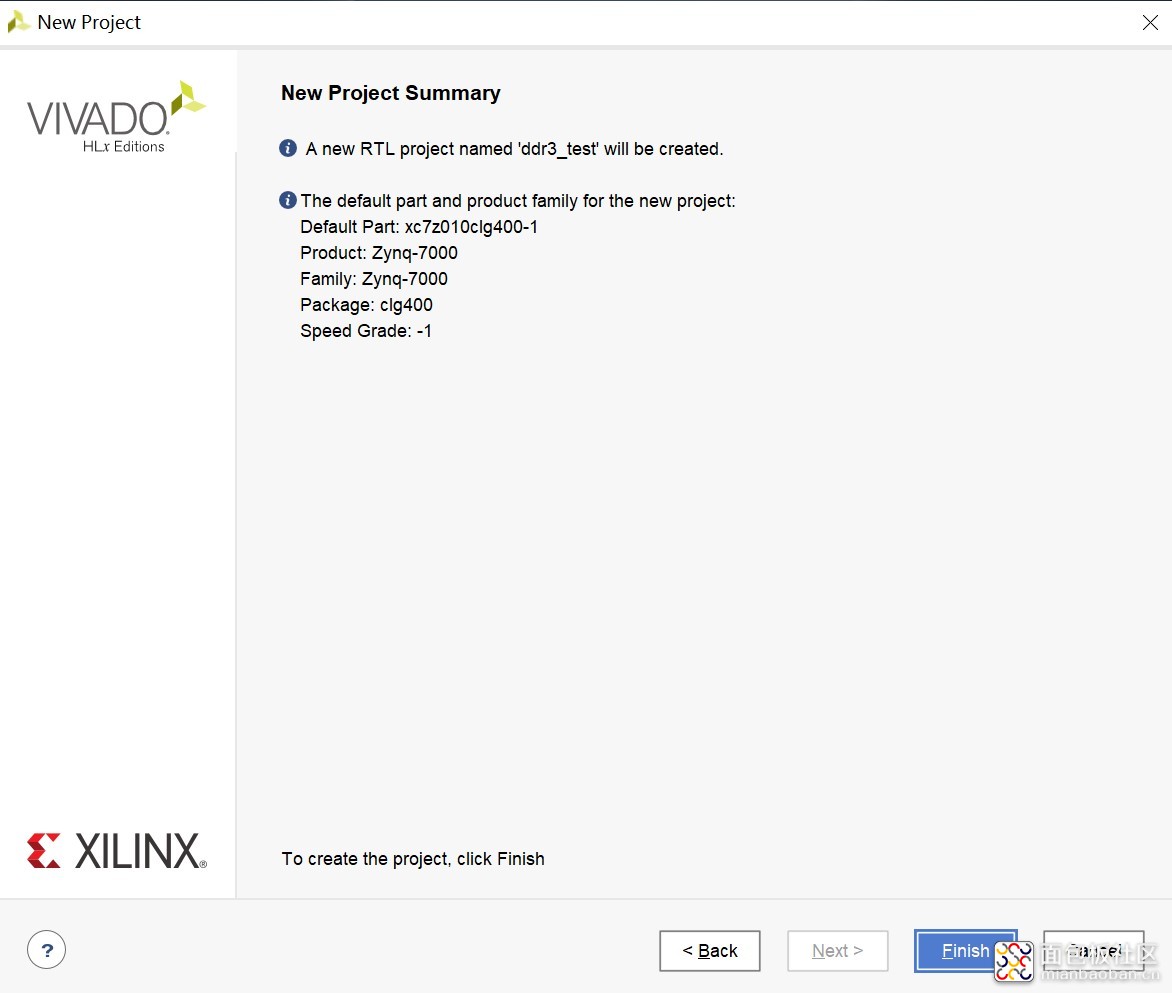

5、在总结页面(New Project Summary)按Finish后开始创建新工程,如下图示:

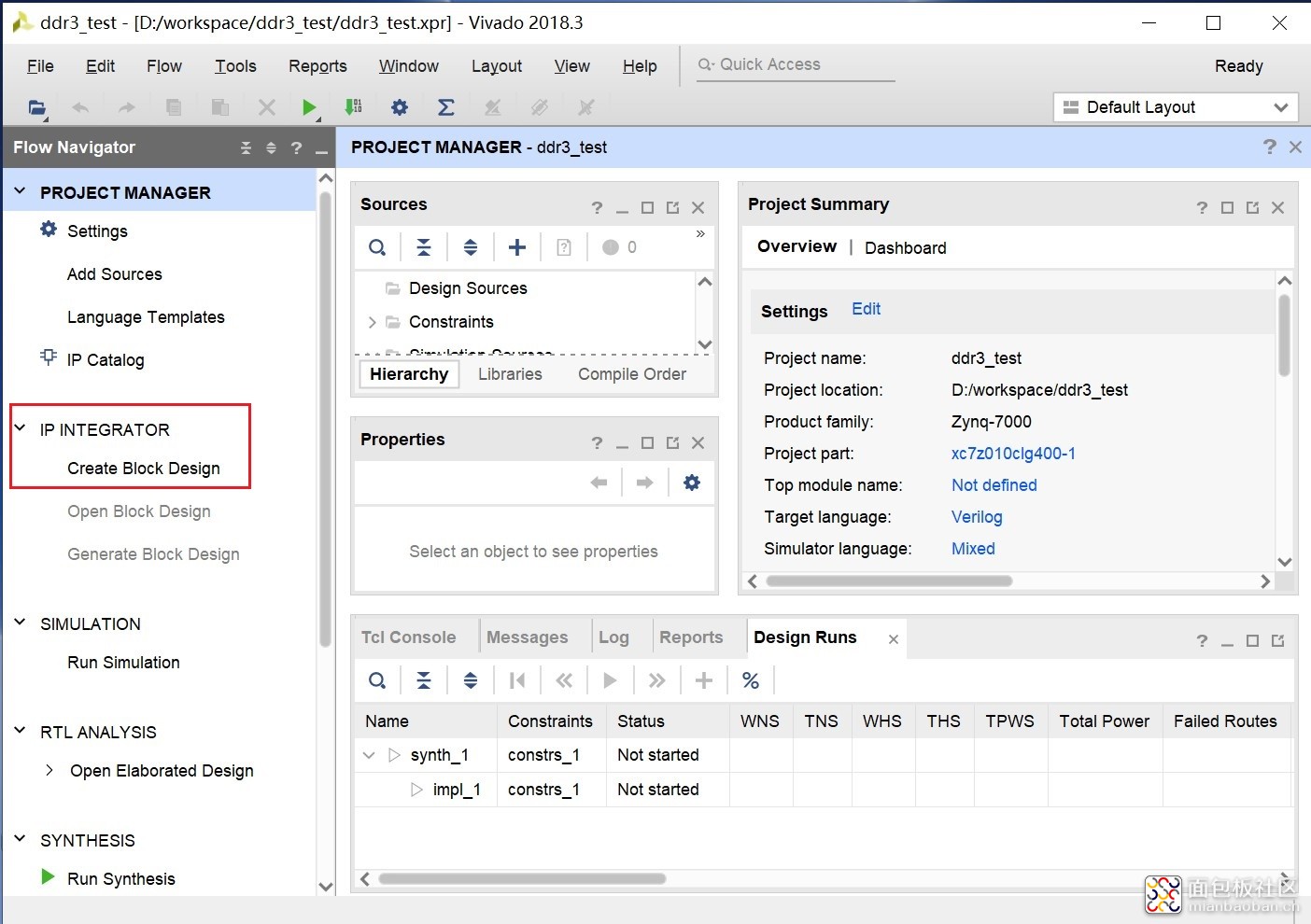

6、在工程左侧IP INTEGRATOR下点击Create Block Design新建Block Design,如下图示:

7、在弹出的Create Block Design对话框直接按OK采用默认值,如下图示:

8、在Diagram对话框直接点击加号图标来添加IP按OK,如下图示:

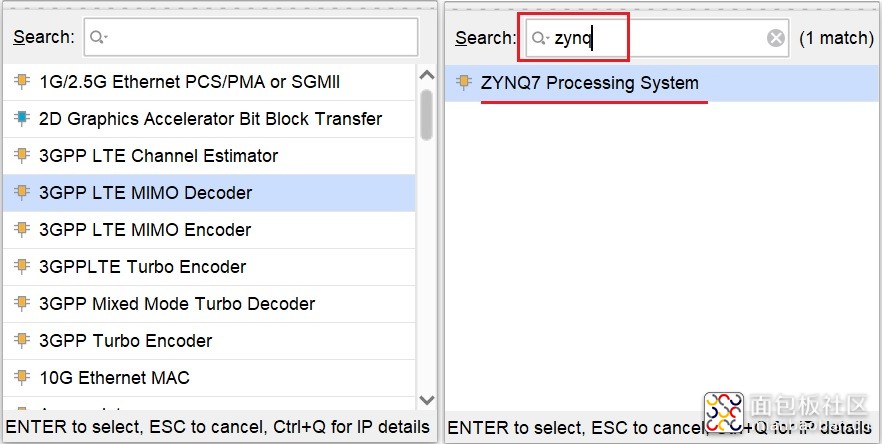

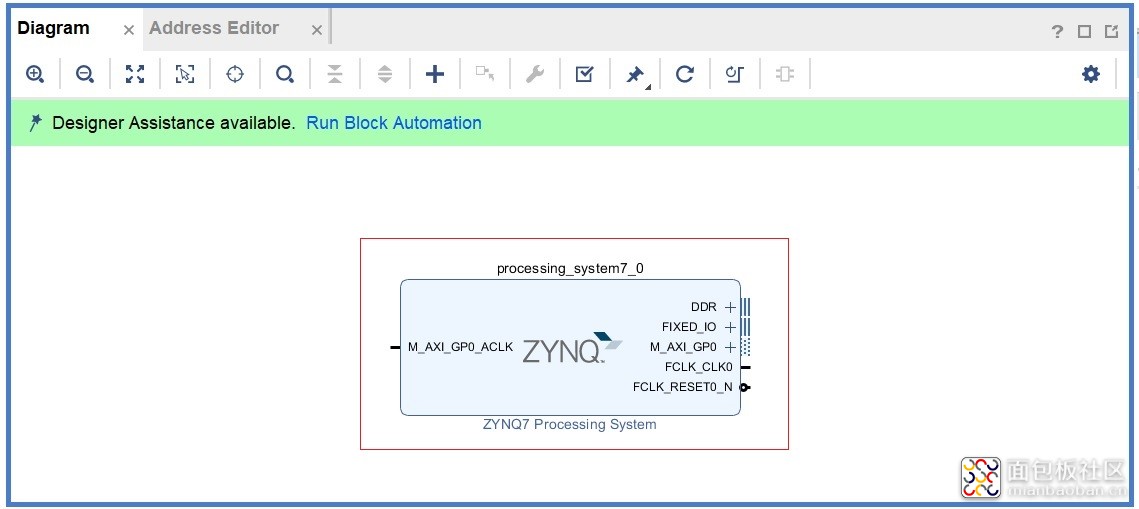

9、在弹出的IP选择对话框在Search栏输入zynq,然后双击找到的ZYNQ7 Processing Syetem添加ZYNQ PS硬核IP,如下图示:

10、先点击上图中ZYNQ7Processing System(红框处)选中IP核,再双击进入IP设置界面,如下图示:

11、点击上图左侧的PeripheralI/O Pins对外设进行配置,这里只选择UART1外设,用到MIO48和MIO49引脚,如下图示:

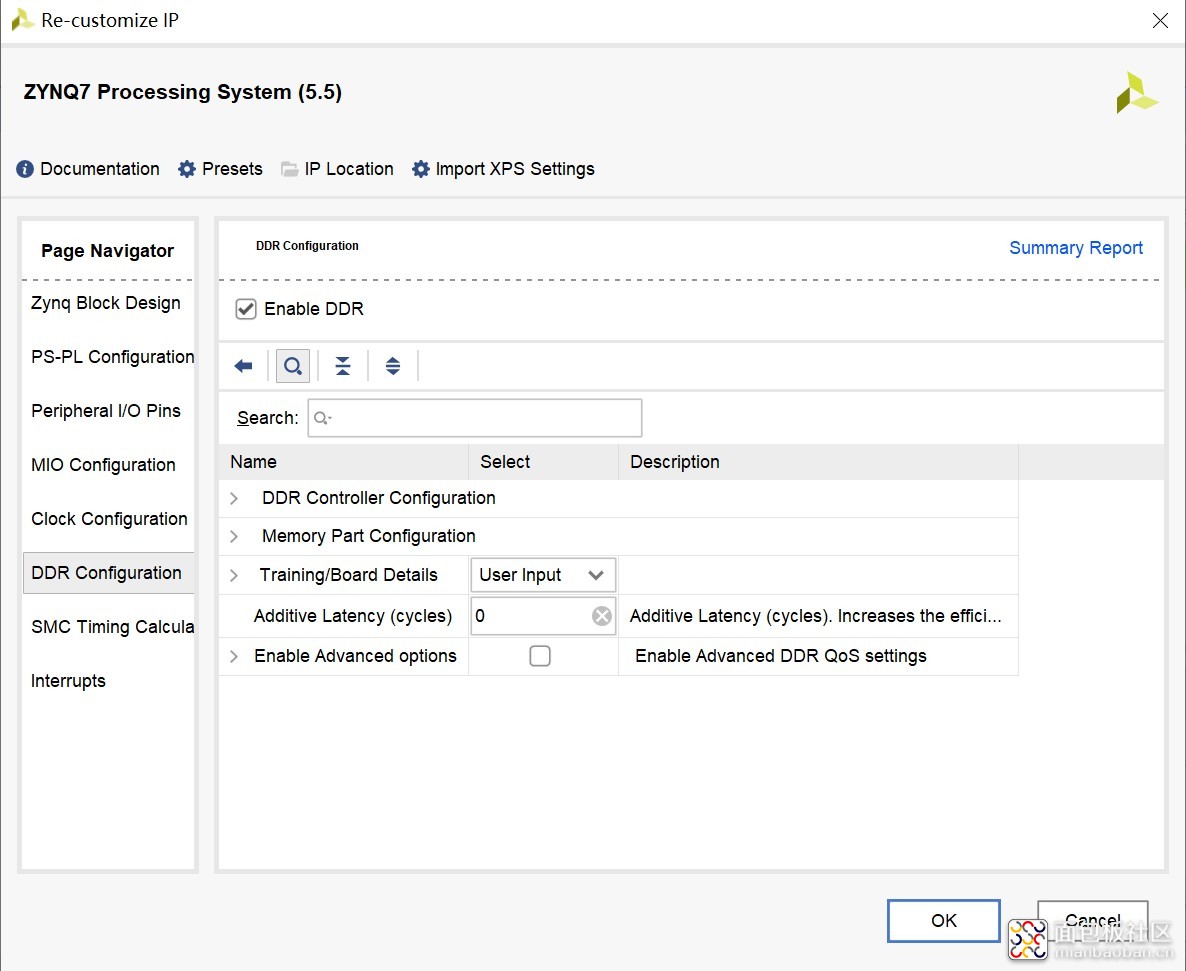

12、点击上图左侧的DDRConfiguration对DDR进行配置,配置参数有点多,具体参看下面的截图,参数没有截图的地方用默认值,如下图示:

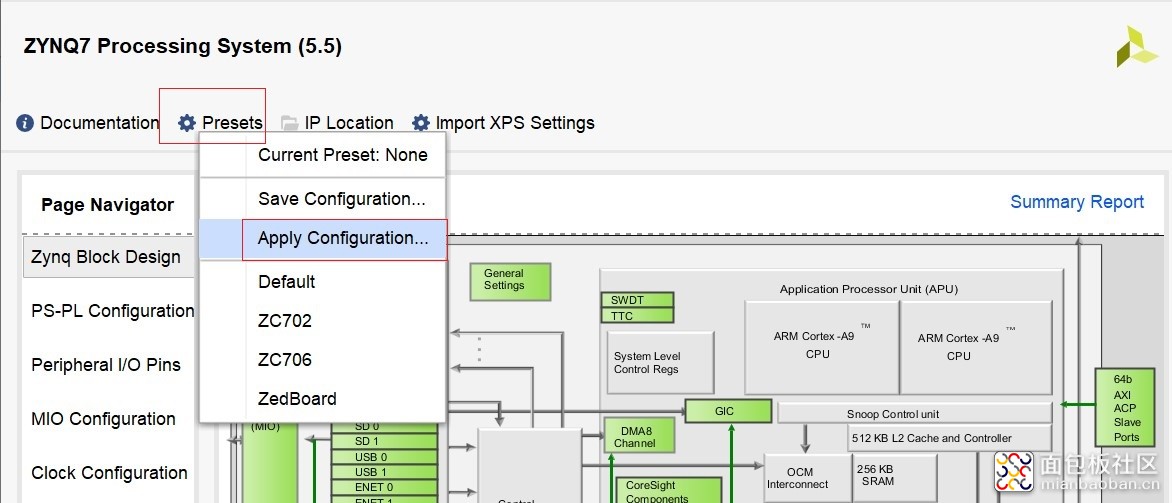

以上IP设置工作比较繁琐又容易出错,XILINX提供了一个用.tcl脚本的方法来设置,先编好.tcl脚本文件,然后选择Presets-->ApplyConfigures...选择Preset Tcl Files就可以,如下图示:

米尔科技提供的DEMO工程都带有一个.tcl脚本配置文件,直接导入配置文件比较方便。

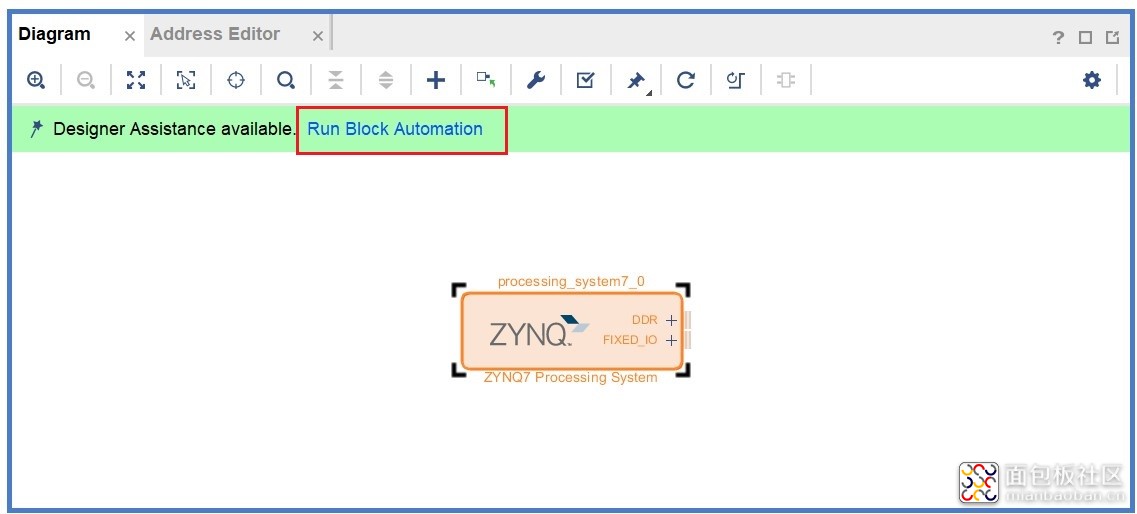

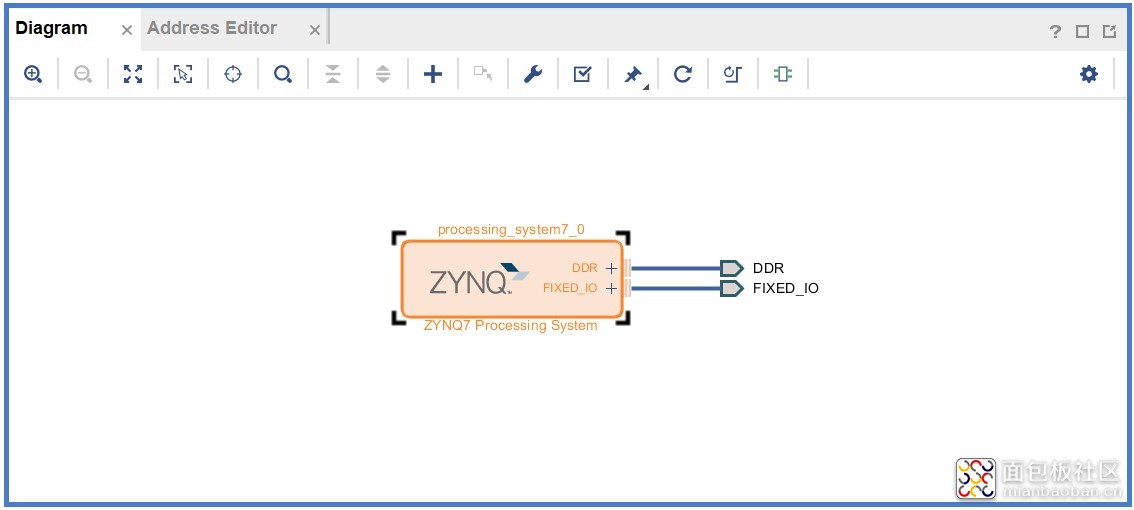

13、PS IP核的其它部分我们不进行配置用默认值,点OK回到Block Diagram界面,点上方的Run Block Automation进行自动连线, 如下图示:

在弹出界面点OK后自动连线完成,如下图示:

14、右击design_1,在右键弹出菜单选择Create HDL Wrapper,然后在弹出对话框用默认的不用修改,点OK就可以,如下图示:

15、右击design_1,在右键弹出菜单选择-->Generate OuputProducts…,然后在弹出对话框点Generate等待完成就可以,如下图示:

16、由于本次测试没有用到PL部分,所以不用生成bitstream,在vivado主界面选择File->Export->ExportHadfware,如下图示,不用勾选Include bitstream, 直接点OK。

17、在vivado主界面选择点击菜单栏上的File -->Launch SDK -->OK 启动 SDK,直接点OK,如下图示:

18、在SDK软件主界面选择点击菜单栏上的File -->New -->Application Project 新建工程,如下图示:

19、在New Project界面输入工程名为ddr3_test,然后点Next选择MemoryTests,最后点Finish完成,如下图示:

新建好工程后软件会自动编译一次,当然也可在软件左侧工程浏览窗口选择一个工程后点右键选择编译工程,如下图示:

20、连接好串口线到电脑,打开一个串口终端,波特率为115200bps,数据为8比特,无校验,停止位为1比特,再连接下载器到开发板的JTAG接口(特别注意方向,因为XILINX下载器有一排针是接地的, 可以先连上过再用万用表检查两排针是否短接情况,两排针都有短接说明接反了,需要换个方向连接,一定要保证方向正确,否则容易损坏硬件),给开发板上电,可以通过Target Connections了解是否连接好硬件,如下图所示:

可能有些童鞋会遇到不能识别硬件的情况,一般是驱动没有安装好,如digilent下载器 JTAG驱动在Vivado安装目录如C:\Xilinx\Vivado\2018.3\data\xicom\cable_drivers\nt64\digilent\,安装完驱动电脑要重新启动一次才可以识别。

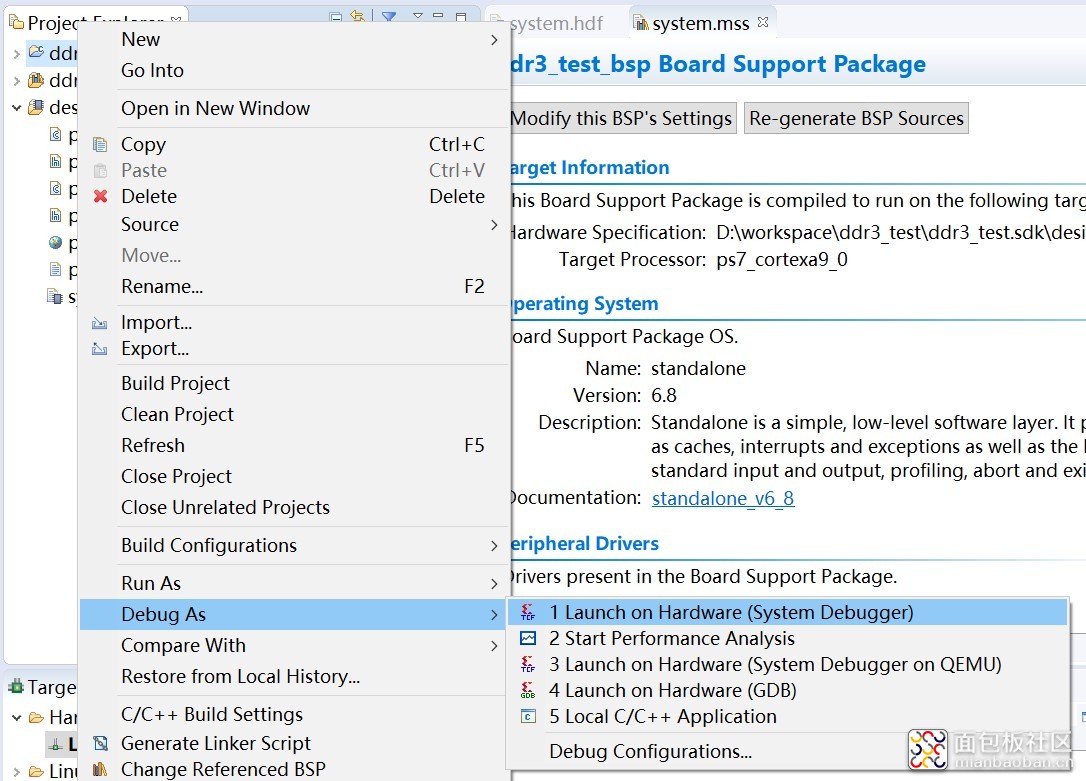

21、在软件左侧工程浏览窗口选择一个工程后点右键选择调试(Debug As)或者运行(Run As)工程,如下图示:

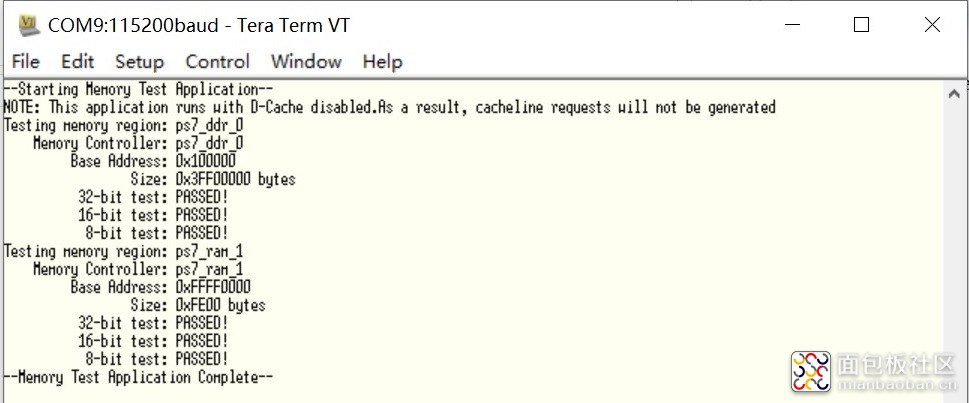

22、可以在串口上看到DDR3测试的打印结果,如下图示:

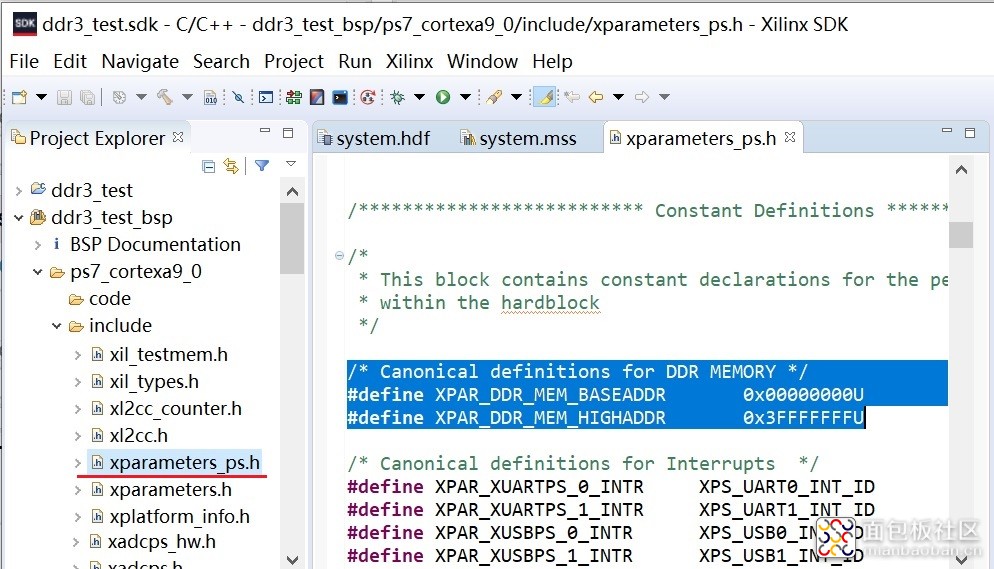

我们可以进一步了解下ddr3_test_bsp -->ps7_cortexa9_0 -->include路径,打开该路径下的xparameters_ps.h这个头文件,这个头文件是cortexA9可以直接控制的外设地址的宏定义,在里面可以找到DDR3的访问地址,具体如下代码:

/* Canonical definitions for DDR MEMORY *

/#define XPAR_DDR_MEM_BASEADDR 0x00000000U

#define XPAR_DDR_MEM_HIGHADDR 0x3FFFFFFFU操作截图如下图示:

在ddr3_test_bsp -->ps7_cortexa9_0 -->include路径下有个xil_io.h头文件,这个头文件里我们可以看cortexA9可以直接访问内存地址空间的读写函数代码,如下所示:

//读函数

staticINLINE u8 Xil_In8(UINTPTR Addr);

staticINLINE u16 Xil_In16(UINTPTR Addr);

staticINLINE u32 Xil_In32(UINTPTR Addr);

staticINLINE u64 Xil_In64(UINTPTR Addr);

//写函数

staticINLINE void Xil_Out8(UINTPTR Addr, u8 Value)

staticINLINE void Xil_Out16(UINTPTR Addr, u16 Value)

staticINLINE void Xil_Out32(UINTPTR Addr, u32 Value)

staticINLINE void Xil_Out64(UINTPTR Addr, u64 Value)

由于我们新建的工程已经包含Memory测试代码,以上只是了解下,如果是自己写代码可以直接用到,当然也可以通过调试代码的方式了解到Memory测试工程访问DDR3的方法。 至此,以上我们Step by Step详细描述了完成一个DDR3测试DEMO的步骤,如有疑问欢迎留言交流。

/2

/2