数字频率计的设计,其功能是实现信号的频率、周期、占空比以及脉宽等指标的测量。本设计用到了数字系统设计理论、单片机理论、电子技术等方面的知识。硬件主要使用Lattice ISP1032芯片、AT89C51芯片、LED显示器以及其他必要的元件;软件使用了VHDL 语言、MCS-51单片机语言以及MUX+PLUS II设计平台。

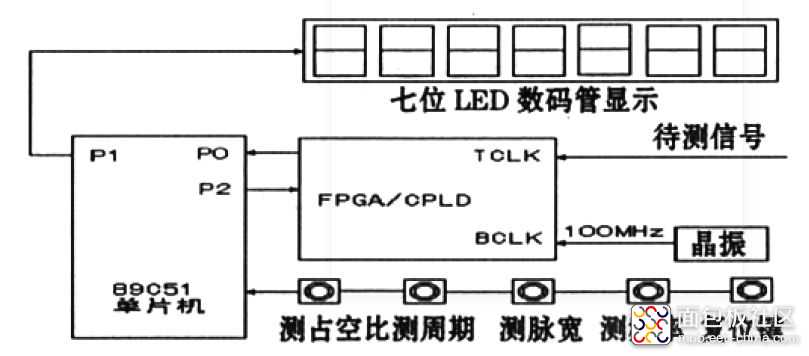

数字频率计的主系统主要有以下五个部分组成,如下图所示。

1)信号整形电路。用于对待测信号进行整形,以便作为PLD 器件的输入信号。本系统采用史密特触发器实现。

2)测频电路。测频核心电路模块,由FPGA等PLD器件担任。本系统采用Lattice ISP1032实现。

3)单片机电路模块。 用于控制测频操作和读取测频数据,并做出相应处理。本系统采用AT89C51芯片实现。

4)键盘模块。 用5个键执行测试控制,一个是复位键,其余是命令键。

5)数码显示模块。用7个LED数码管显示测试结果,最高可表示百万分之一的精度。

/5

/5