镜像恒流源是模拟集成电路中普遍存在的一种标准部件,它的受控电流与输入参考电流相等,即输入输出电流传输比等于1。其特点是输出电流是对输入电流按一定比例的“复制”,用来产生偏置电流和作为有源负载。

电流镜是模拟集成电路设计中基本的电路单元之一,在电流拷贝,运放偏置等电路中极为常见,其决定着电流拷贝的精准性以及运放的增益,匹配等特性。共源共栅电流镜得益于其优越的输出阻抗,在高精度的模拟电路中被广泛使用。

本文简单复习并介绍了三种常见的共源共栅电流镜,结合笔者的设计经验给出了一些设计考虑,希望可以对读者有所帮助。

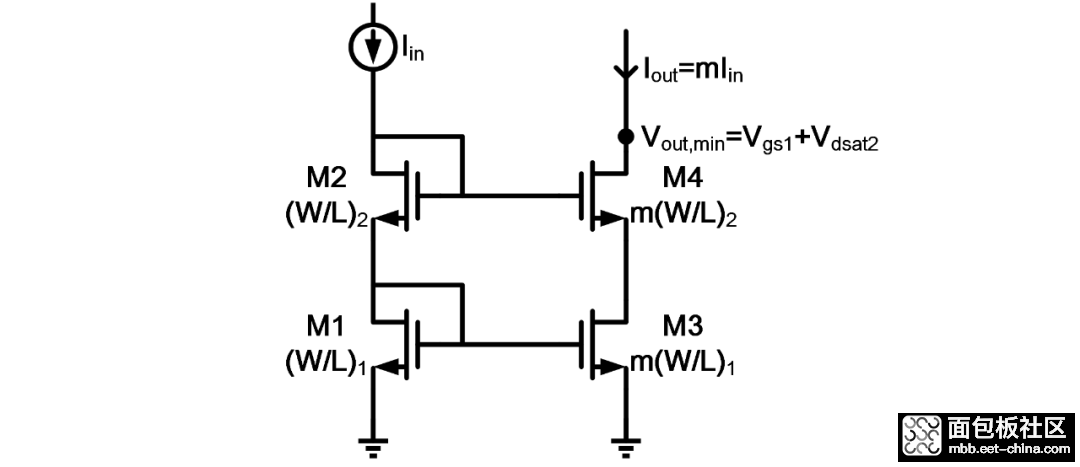

上图所示为简单的共源共栅电流镜,对该电路而言,只需要保证M1和M3,M2和M4这两对MOS管成比例的设计,同时输出电压大于Vgs1+Vdsat2的要求,即可使所有的MOS管都工作在饱和区,以实现精准的电流拷贝和较大的输出阻抗。

在设计时,我们常常将M1和M3设计得具有较大的沟长L和较大的过驱动电压,这是因为电流拷贝主要由M1和M3决定,因此较大的沟长L可以保证M1和M3输出阻抗更大,因而更少地受到漏端电压的影响,电流拷贝更为精准。而较大的过驱动电压可以保证他们受失配的影响更小。而作为减弱输出电压影响功能的M2和M4,出于面积和输出电压裕度的考虑,要求变得宽松了很多,事实上M2和M4在设计时甚至可以采用工艺允许的最小沟长。这一点在所有的共源共栅中都是适用的。

该电路的最大缺点即为其“吃掉”了很大的输出电压裕度,相比低压共源共栅电流镜,它需要的输出电压“高”一个Vth,对于在意输出电压范围的应用,如供电电压很低,或为作为共源共栅运放的输出级等,该电路显得“浪费”,因此不那么适用。而对一个不在意输出电压范围的电路,比如芯片中各种电流的简单拷贝,其电路简单,设计方便,需要考虑的因素没有低压共源共栅电流镜多,因此更为适用。

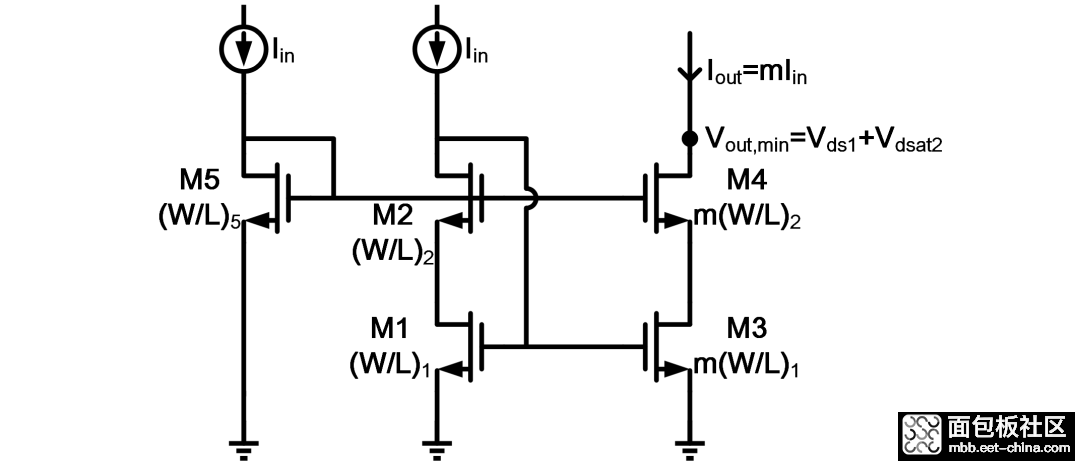

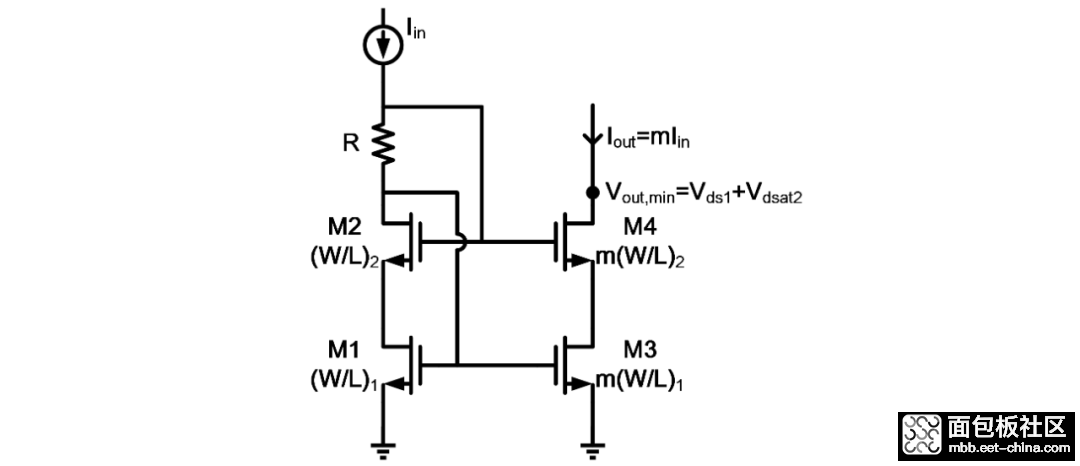

为了解决简单共源共栅电流镜输出电压范围大的问题,低压共源共栅电流镜应运而生。图2和图3给出了日常设计中两种常用的低压共源共栅电流镜电路,两者区别为产生M2(M4)的栅极偏置电压电路的不同。相同的是,为了使所有晶体管工作在饱和区,电路需要满足式(1):

在图2中,Vg2即为M5的栅源电压Vgs5,通过另外一路电流加上合理选择M5的尺寸,以使得Vg2满足上式的要求。而在图3中,Vg2为Vgs1+IinR,通过选择R的值即可确定Vg2。

根据式(1)可知,Vg2被限定在一个范围内,因此相比简单的共源共栅电流镜,低压共源共栅电流镜受到了额外的约束,在这种约束下,会出现下面两种情况:

- 情况1:Vg2如果设置过低,则容易使得M1进入线性区,因为在电流镜中,M1和M3决定电流拷贝,因此工作在线性区会使得该电流镜直接不正常工作;

- 情况2:如果Vg2设置过高,则M2进入线性区,此时M4是否进入线性区取决于M4的漏端电压。但此时,M1和M3仍然工作在饱和区,电流拷贝仍然正常。如果M4的漏端电压足够到M4工作在饱和区,那么M4仍然可以起到减弱输出电压对M3漏端电压影响的作用,但是因为M1+M2与M3+M4不是完全镜像,因此电流拷贝的精准性不如完全正常工作的电流镜。这种情况,如果不要求电流拷贝准确,只单纯想要高输出阻抗,比如作为运放输出级,那么该目标仍然可以实现。因此,如果在设计运放偏置时,由于电路的限制,必须选择Vg2在整个温度,工艺角范围内高一些或是低一些,高一些这个选择可能影响会更小。这也是笔者在电路设计时常常遇到的问题,该问题尤其在Vgs1较低时更容易出现,因为该情况会使得留给Vg2的可选范围很小,尤其加上温度和工艺角的考虑。

图2和图3相比,图2电流需要多一路电流进行偏置,而图3电路需要多使用一个电阻,前者带来额外的功耗和电路复杂度,后者带来更大的面积(尤其在低功耗电路中),设计时可以根据需求进行选择。

相比简单共源共栅电流镜,低压共源共栅电流镜多了一个阈值电压的输出电压裕度,因此更适用于低供电电压,运放输出级等场景。

本文简单介绍了三种常见的共源共栅电流镜电路,结合笔者的设计经验提出了一些个人设计见解,希望读者多多指正。

转载自臣扬,仅供学习交流使用,如有侵权,请联系删除。

/2

/2