反正我是有的,而且在前段时间,读了TI的一篇应用文档后,才算明白了。

3V3TTL和3V3CMOS接口为啥能兼容呢?

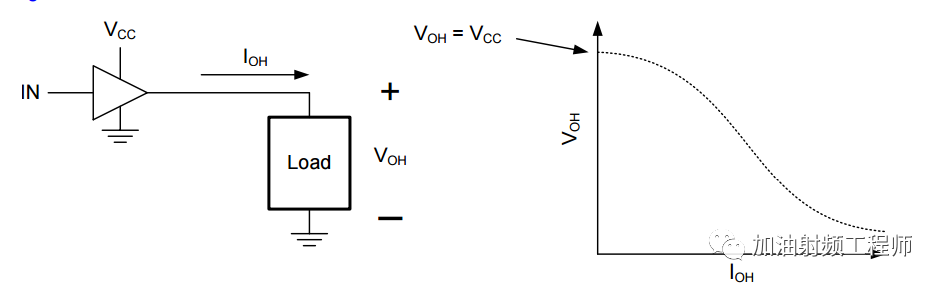

手册上一般给出Voh和Vol的门限电平,那实际输出时,高电平比Voh高多少,低电平又比Vol低多少呢?

如果芯片每路的驱动能有20mA,那10路就有200mA,我找LDO时,要不要把这余量考虑在内?

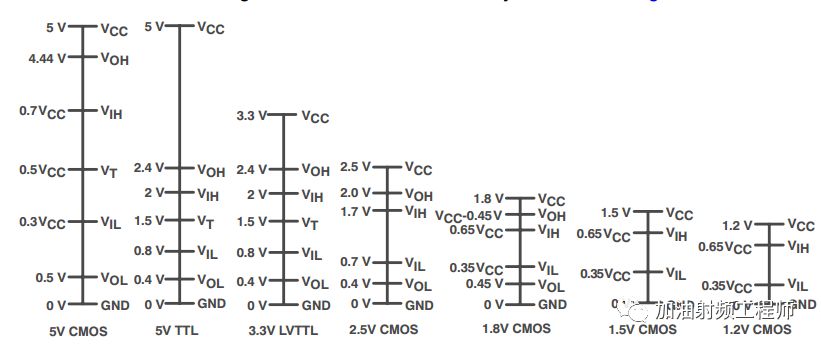

上图摘自TI的文档。不过,没有3V3CMOS的,只好自己去找相关定义了。

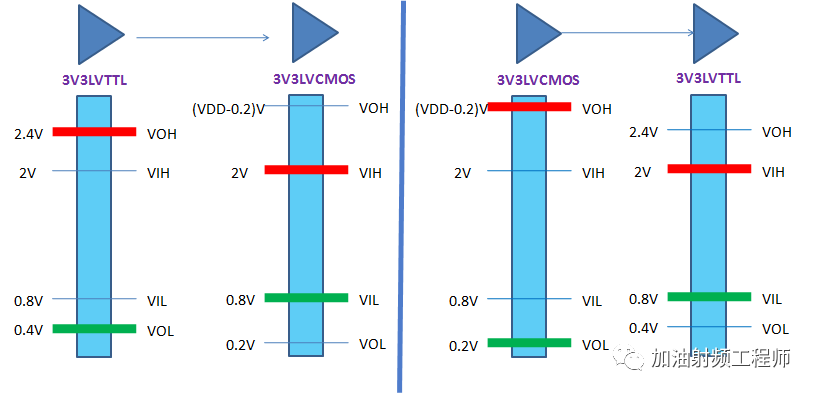

首先看3V3TTL和3V3CMOS兼容的问题,一直都说是能兼容的,可是疑问一直在我心中,为啥说他俩能兼容呢。现在总算明白了。

为了成功连接两个器件,必须符合以下要求:

1. 驱动器的 VOH 必须高于接收器的 VIH。

2. 驱动器的 VOL 必须低于接收器的 VIL。

3. 驱动器的输出电压不得超过接收器的 I/O 电压容差。

由于都是3.3V的供电,一般情况下,第三点满足。第二点和第三点见下图,此图一出,一目了然。分为两种情况,一种3V3TTL为输出,3V3CMOS输入,另一种情况是调换一下位置。

关于第二个问题,文档中提到,如果需驱动的电阻不是过小时,输出的高电平能到电源电压,输出的低电平能接近0V。

关于第三个问题,一般情况下,被驱动的阻值都是很大的,极端情况下,才会达到20mA的驱动电流。所以,一般情形下,驱动电路的工作电流还是很小的,基本不用考虑。

文献:

【1】JEDEC STANDARD,InterfaceStandard for Nominal 3 V/3.3 V SupplyDigital Integrated Circuits

【2】slva700,Introduction to Logic

本文由编辑推荐,原出处:https://www.eet-china.com/mp/a132899.html

/5

/5