- 引言

- 一、串并转换器的Verilog代码实现

- 二、串并转换器的 RTL 电路实现

引言

设计的思想是这样的:有一组数据以 N MHz 的速率从 FPGA 的一个 I/O 口传入,要实现在 FPGA 的另一端 4 个 I/O 口以 N/4 MHz 的速率把传入的速率吐出,也就是说每隔 4 个主时钟周期要从 4 个输出口输出从输入口输入的 4 个数据。

数据传输按照传输方式分为串行传输和并行传输,串行传输就是每一个时钟传输一个比特(一个逻辑数据:即 0 或者 1),仅有一根线,而用通俗的比喻来讲,就是你的心脏每跳动一次,就发出一个数据。至于并行传输,就是多个串行传输的结合,每一个时钟传输 N 个比特(并行 N 个),有 N 根线。

一、串并转换器的 Verilog 代码实现

Plaintext module Serial2Pal( input Clk, input din, input ena, output reg [3:0] dout = 4'b0000 ); always @ (posedge Clk) if(ena) dout <= {dout[2:0],din}; else dout <= dout; endmodule |

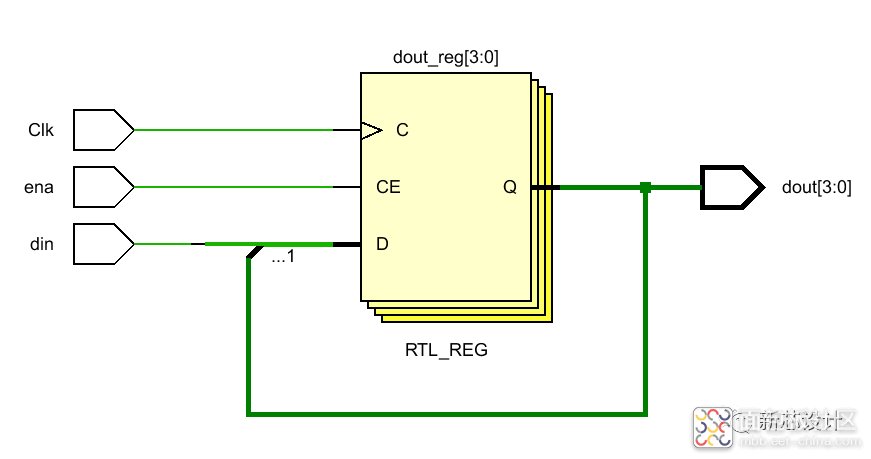

二、串并转换器的 RTL 电路实现

串并转换器的 Verilog 电路图

/5

/5