Chiplet 俗称“芯粒”或“小芯片组”,通过将原来集成于同一 SoC 中的各个元件分拆,独立 为多个具特定功能的 Chiplet,分开制造后再通过先进封装技术将彼此互联,最终集成封装 为一个系统芯片。Chiplet 可以将一颗大芯片拆解设计成几颗与之有相同制程的小芯片,也 可以将其拆解设计成几颗拥有不同制程的小芯片。Chiplet 是一种硅片级别的 IP 整合重用技 术,其模块化的集成方式可以有效提高芯片的研发速度,降低研发成本和芯片研制门槛。 传统的 SoC 是将多个负责不同类型计算任务的计算单元,通过光刻的形式制作到同一块晶圆 上,其追求的是高度的集成化,利用先进制程对于所有的单元进行全面的提升。而 Chiplet 是在设计系统芯片时,先按照不同的计算单元或功能单元进行分解;然后针对每个单元选择 最适合的半导体制程工艺分别进行制造;再通过先进封装技术将各个单元彼此互联;最终集 成封装为一个系统级芯片组。

摩尔定律正在逐步放缓。随着工艺制程节点继续向着更小的 5nm、3nm 甚至埃米级别推进,半导体工艺制程已经越来越逼近物理极限,不仅推进的难度越来越高,所需要付出的代价也越 来越大。研究机构 IBS 统计对比 16nm 至 3nm 的单位数量的晶体管成本指出,随着制程工艺 的推进,单位数量的晶体管成本的下降幅度在急剧降低。比如从 16nm 到 10nm,每 10 亿颗晶 体管的成本降低了 23.5%,而从 5nm 到 3nm 成本仅下降了 4%。随着先进制程的持续推进,单 位晶体管所需要付出的成本降低的速度正在持续放缓,即意味着摩尔定律正在放缓。 Chiplet 诞生背景是在摩尔定律放缓,性价比逐步凸显。摩尔定律由戈登·摩尔(Gordon Moore) 提出,其内容为“当价格不变时,集成电路上可容纳的晶体管的数目,约每隔 18-24 个月便 会增加一倍。”在集成电路过去几十年的发展过程中,受摩尔定律的指引,在晶体管的尺寸不 断微缩以及处理器性能不断增强的同时,半导体制程工艺的成本可以维持不变,甚至下降。 Chiplet 能够通过多个裸片片间集成,突破了单芯片 SoC 的诸多瓶颈,带来一系列优越特性, 从而延续摩尔定律。

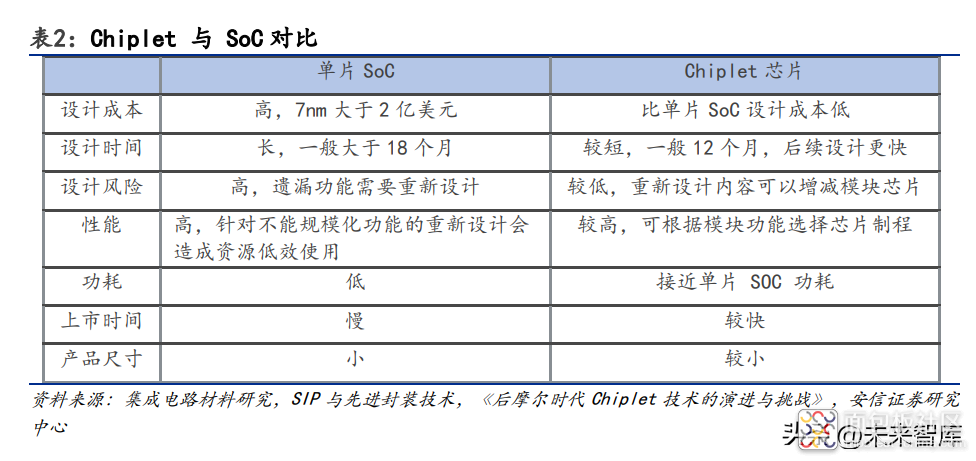

Chiplet 在设计成本、良率、制造成本、设计灵活性等方面优势明显

与传统 SoC 相比,Chiplet 在设计成本、良率、制造成本、设计灵活性等方面优势明显。

1. Chiplet 能显著提升良率。在高性能计算、AI 等方面的巨大运算需求下,芯片性能快速 提升,芯片中的晶体管数量也在快速增加,导致芯片面积不断变大。对于晶圆制造工艺而言, 芯片面积越大,工艺的良率越低。由于每片 wafer 上都有一定概率的失效点,而对于晶圆工 艺来说,在同等技术条件下难以降低失效点的数量,因此被制造的芯片面积较大,失效点落 在单个芯片上的概率就越大,所以良率会下降。通过运用 Chiplet 的手段,可以将大芯片拆 解分割成几颗小芯片,单个芯片面积变小,失效点落在单个小芯片上的概率将大大降低,从 而提高了制造良率。

2. Chiplet 能降低芯片制造成本。Chiplet 的核心思想是先分后合,先将单芯片中的功能块 拆分出来,再通过先进封装模块集成为单芯片。将 SoC 进行 Chiplet 化之后,不同的芯粒可 以根据需要来选择合适的工艺制程分开制造,然后再通过先进封装技术进行组装,不需要全 部都采用先进的制程在一块晶圆上进行一体化制造,这样可以极大地降低芯片的制造成本。

3. Chiplet 能提高芯片设计的灵活度,显著降低设计成本。由于 Chiplet 芯粒可以独立设计 和组装,因此制造商可以根据自己的需要来选择不同类型、不同规格和不同供应商的芯粒进 行组合,很大程度上提高了芯片设计的灵活性和可定制化程度;并且制造商可以依赖于预定 好的芯片工具箱来设计新产品,缩短芯片的上市时间。同时 The Linley Group 在《Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small》中提出,Chiplet 技术可以将 大型 7nm 设计的成本降低高达 25%;在 5nm 及以下的情况下,节省的成本更大。

Chiplet 方案目前在互联与封装两块还存在一定的难点。Chiplet 的关键是让芯粒之间高速 互联,因此芯片设计公司在设计芯粒之间的互联接口时,需要保证高数据吞吐量与低数据延 迟和误码率,同时还要考虑能效和连接距离。Chiplet 方案对封装工艺也有更高的要求,主 要由于第一封装体内总热功耗将显著提升;第二芯片采用 2.5D/3D 堆叠,增加了垂直路径热 阻;第三更加复杂的 SiP,跨尺度与多物理场情况下热管理设计复杂。以上要求都给 Chiplet 技术的发展增加了难点。

来源:(报告出品方/作者:安信证券,马良、郭旺)

/3

/3