高边顾名思义就是用在电源的正极,用在电源的负极叫低边 ,高边分为集成MOS的和外置MOS的产品,集成MOS的又可以分为合封的和采用内置LDMOS, 内置BCD的treach MOSFET或者半超结结构的等,目前国内的高边还不很全,内置的MOS基本采用LDMOS或者合封的方式,目前华虹和SMIC正在积极的开发内置Trench的MOS的产品。

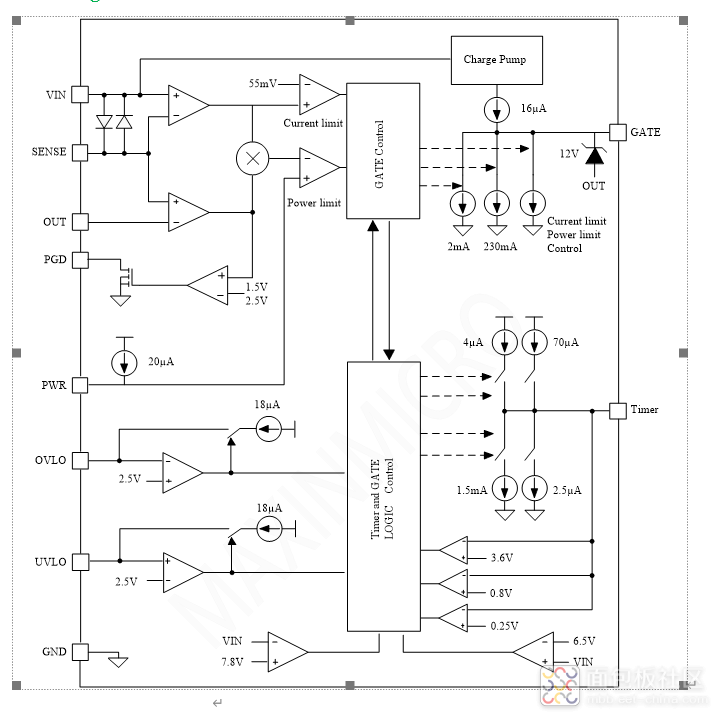

无锡明芯微电子于几年前发布了单纯的高边开关MX5069D,MX5069MS和MX5069HD,这几款产品没有过流保护,功率限制和重启周期可调的功能,无锡明芯微于近期升级了产品设计,发布了LMX系列产品,LMX5069系列产品新增了功率限制,过流保护,软起动通过Timer可调等功能,并且在耐压和功耗上做了优化,工作和静态功耗都比国外同类产品减少一半,电压增加到90v,最大耐压108V。LMX5069是对之前发布的产品的替代和升级,推荐客户用LMX5069做新产品设计。具体的LMX5069的结构如下图。

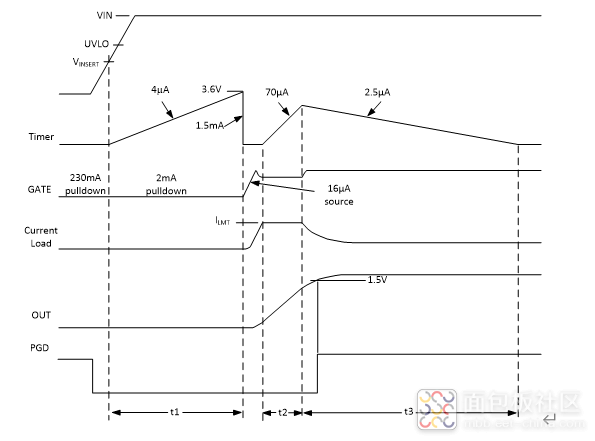

LMX5069的开启时序图

LMX5069的 VIN 工作范围为 9V 至 80V,瞬态能力可达 100V。当 VIN 最初增加时,外部 NMOSFET 在 GATE 引脚上保持 230mA 下拉电流。GATE 引脚上的强下拉电流可防止 MOSFET 的栅极到漏极的电容被充电。此外,Timer 引脚最初保持在地。当 VIN 电压达到 VINSERT 阈值时,插入时间开始。在插入时间内,Timer 引脚上的电容器由 4μA 电流源充电,而 Q1 由 GATE 引脚上的 2mA 下拉电流保持,而与 VIN 电压无关。插入时间延迟允许在 Q1 使能之前建立 VIN 的振铃和瞬态。 当 Timer 引脚电压达到 3.6V 时,插入时间结束。电容器由内部 1.5mA 下拉电流快速放电。在插入时间之后,当 VIN 达到 VINEN 阈值时,LMX5069 控制电路使能。当 VIN 超过 UVLO 阈值时,GATE 引脚接通 Q1。如果 VIN 在插入时间结束时高于 UVLO 阈值,则 Q1 在该时间开启。GATE 引脚电荷泵提供 16μA 电流,以对 Q1 的栅极电容进行充电。Q1 的最大栅源电压受内部 12V 齐纳二极管的限制。随着 OUT 引脚上的电压增加,LMX5069 会监控 MOSFET 的漏极电流和功率耗散。在浪涌电流限制和功率限制电路主动控制输送到负载的电流。在浪涌限制间隔期间,一个内部 70μA 故障定时器电流源为定时器电容器充电。如果 Q1 的功耗和输入电流在 Timer 引脚达到 3.6V 之前降低到各自的限制阈值以下,则电流 70μA 源关闭,电容器由内部 2.5μA 电流吸收放电。当 OUT 引脚上的电压增加到输入电压的 1.5V 以内,并且 PGD 引脚切换为高电平时,浪涌限制间隔完成。 浪涌电流限制或功率限制停止之前,定时器引脚电压 3.6V,宣布故障,Q1 关闭。 电荷泵提供高于输出电压 (OUT 引脚) 的内部偏置电压,以增强 N 沟道 MOSFET 的栅极。栅源电压由内部 12V 齐纳二极管限制。在正常工作条件下,Q1 的栅极由一个内部 16μA 电流源保持充电,比 OUT 高约 12V。当系统电压最初施加时,GATE 引脚由 230mA 下拉电流保持为低电平。这有助于防止 MOSFET 在施加的系统电压增加时通过其米勒电容器意外导通。在插入期间,GATE 引脚由 2mA 下拉电流保持为低电平。这将使 MOSFET 保持关断状态,直到 t1 结束,而不管 VIN 或 UVLO 的电压如何。在插入时间之后,在上图 Q1 的栅极电压被调制,以防止电流或功率耗散水平超过编程水平。在电流或功率限制模式下,定时器电容器正在充电。如果电流和功率限制在 Timer 引脚达到 3.6V 之前停止,则 Timer 引脚电容器放电,电路进入正常工作状态。

如果浪涌限制条件持续存在,使得 Timer 引脚在 t2 期间达到 3.6V,则 GATE 引脚被 2mAPulldown 电流拉低。然后 GATE 引脚保持低电平,直到 restart 序列结束。如果系统输入电压降至 UVLO 阈值以下或高于 OVLO 阈值,则 GATE 引脚被 2mA 下拉电流拉低以关闭 MOSFET

/3

/3