PLC与PLD对于大多数控制行业的朋友们与单片机爱好者,都不是陌生的名词。可是您了解它们的“一字之差”吗?如果您对此感兴趣,就请看看小编今天介绍的内容。

可编程控制器(PLC)

可编程控制器(PLC)是计算机家族中的一员,是为工业控制应用而设计制造的。早期的可编程控制器称作可编程逻辑控制器,简称PLC,它主要用来代替继电器实现逻辑控制。随着技术的发展,这种装置的功能已经大大超过了逻辑控制的范围,因此,今天这种装置称作可编程控制器,简称PC。但是为了避免与个人计算机的简称混淆,所以将可编程控制器简称PLC(Programmable Logic Controller)。

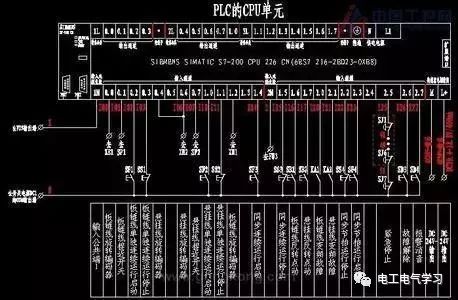

某型号PLC的内部电路

PLC的主要特点高可靠性

丰富的I/O接口模块

采用模块化结构

编程简单易学

安装简单,维修方便

PLC的功能逻辑控制

定时控制

计数控制

步进(顺序)控制

PID控制

数据控制:PLC具有数据处理能力。

通信和联网

其它:PLC还有许多特殊功能模块,适用于各种特殊控制的要求,如:定位控制模块,CRT模块。

某型号PLC控制柜

可编程逻辑器件PLD

PLD是可编程逻辑器件(ProgramableLogicDevice)的简称,FPGA是现场可编程门阵列(FieldProgramableGateArray)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。

PLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。PLD能做什么呢?可以毫不夸张的讲,PLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用PLD来实现。

PLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。在PCB完成以后,还可以利用PLD的在线修改能力,随时修改设计而不必改动硬件电路。使用PLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。

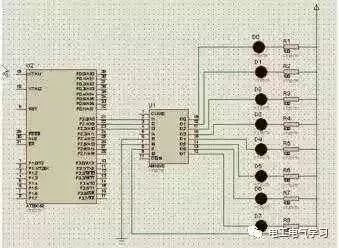

某型号的PLD内部电路

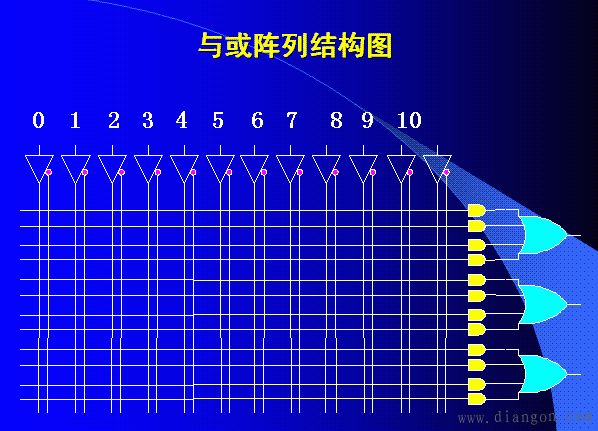

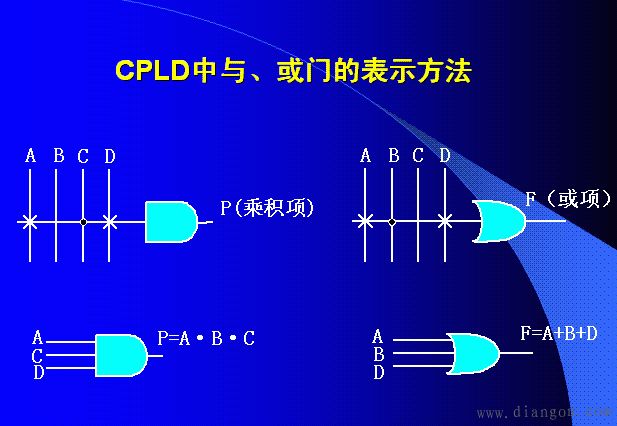

典型的PLD由一个“与”门和一个“或”门阵列组成,而任意一个组合逻辑都可以用“与一或”表达式来描述,所以,PLD能以乘积和的形式完成大量的组合逻辑功能.这一阶段的产品主要有PAL(可编程阵列逻辑)和GAL(通用阵列逻辑)。

对于可编程逻辑器件,设计人员可利用价格低廉的软件工具快速开发、仿真和测试其设计。然后,可快速将设计编程到器件中,并立即在实际运行的电路中对设计进行测试。原型中使用的PLD器件与正式生产最终设备(如网络路由器、DSL调制解调器、DVD播放器、或汽车导航系统)时所使用的PLD完全相同。这样就没有了NRE成本,最终的设计也比采用定制固定逻辑器件时完成得更快。

采用PLD的另一个关键优点是在设计阶段中客户可根据需要修改电路,直到对设计工作感到满意为止。这是因为PLD基于可重写的存储器技术--要改变设计,只需要简单地对器件进行重新编程。一旦设计完成,客户可立即投入生产,只需要利用最终软件设计文件简单地编程所需要数量的PLD就可以了。

某型号PLD外观

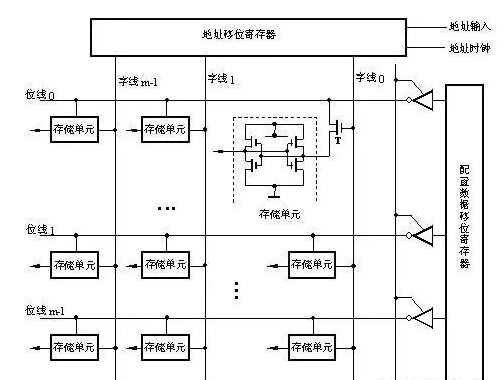

下面以FPGA为例进行介绍PLD的编程原理。

编程数据存储单元以阵列形式分布在FPGA中,编程数据存储单元阵列结构如图1所示。存储单元为5管SRAM结构, 只有一根位线。其中T管为本单元控制门,由字线控制。数据以串行方式移入移位寄存器,而地址移位寄存器顺序选中存储单元的一根字线,当某列字线为高电平时, 该列存储单元的T管导通,从而与位线接通,在写信号控制下将数据移位寄存器中一个字的数据通过各列位线写入该列存储单元。

编程数据按照一定的数据结构形式组成数据流装入FPGA中,编程数据流由开发软件自动生成。开发软件将设计转化成网表文件,它自动对逻辑电路分区、布局和布线和校验FPGA的设计,然后按PROM格式产生编程数据流并形成编程数据文件,最后还可将编程数据文件存入PROM中。

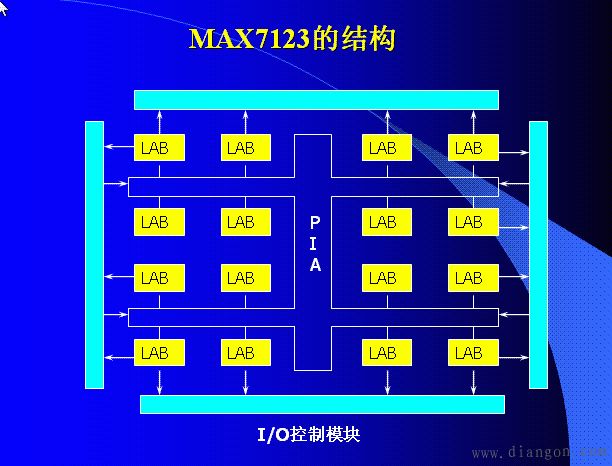

现在一般把所有超过某一集成度(如1000门以上)的PLD器件都称为CPLD。 CPLD由可编程逻辑的功能块围绕一个可编程互连矩阵构成。由固定长度的金属线实现逻辑单元之间的互连,并增加了I/O控制模块的数量和功能。可以把CPLD的基本结构看成由可编程逻辑阵列(LAB)、可编程I/O控制模块和可编程内部连线(PIA)等三部分组成。

MAX7123结构

1.可编程逻辑阵列(LAB)

可编程逻辑阵列又若干个可编程逻辑宏单元(Logic Macro Cell,LMC)组成, LMC内部主要包括与阵列、或阵列、可编程触发器和多路选择器等电路,能独立地配置为时序或组合工作方式。

与或阵列结构图

CPLD中与、或门的表示方法

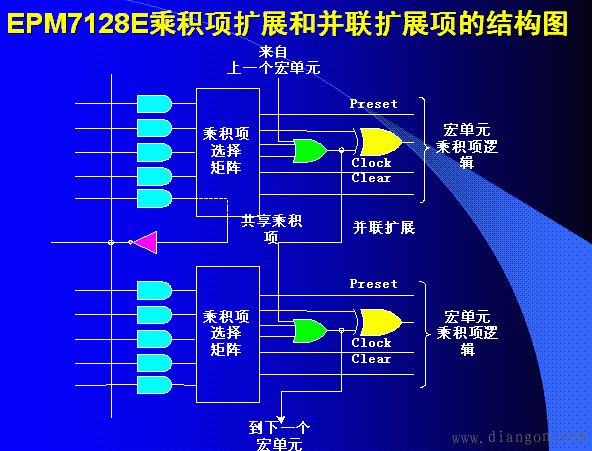

(1)乘积项共享结构

在CPLD的宏单元中,如果输出表达式的与项较多,对应的或门输入端不够用时,可以借助可编程开关将同一单元(或其他单元)中的其他或门与之联合起来使用,或者在每个宏单元中提供未使用的乘积项给其他宏单元使用。

EPM7128E乘积项扩展和并联扩展项的结构图

(2)多触发器结构

早期可编程器件的每个输出宏单元(OLMC)只有一个触发器,而CPLD的宏单元内通常含两个或两个以上的触发器,其中只有一个触发器与输出端相连,其余触发器的输出不与输出端相连,但可以通过相应的缓冲电路反馈到与阵列,从而与其他触发器一起构成较复杂的时序电路。这些不与输出端相连的内部触发器就称为“隐埋”触发器。这种结构可以不增加引脚数目,而增加其内部资源。

(3)异步时钟

早期可编程器件只能实现同步时序电路,在CPLD器件中各触发器的时钟可以异步工作,有些器件中触发器的时钟还可以通过数据选择器或时钟网络进行选择。此外,OLMC内触发器的异步清零和异步置位也可以用乘积项进行控制,因而使用更加灵活

2.可编程I/O单元(IOC)

CPLD的I/O单元(Input/Output Cell,IOC),是内部信号到I/O引脚的接口部分。根据器件和功能的不同,各种器件的结构也不相同。由于阵列型器件通常只有少数几个专用输入端,大部分端口均为I/O端,而且系统的输入信号通常需要锁存。因此I/O常作为一个独立单元来处理.3.可编程内部连线(PIA)

可编程内部连线的作用是在各逻辑宏单元之间以及逻辑宏单元和I/O单元之间提供互连网络。各逻辑宏单元通过可编程连线阵列接收来自输入端的信号,并将宏单元的信号送目的地。这种互连机制有很大的灵活性,它允许在不影响引脚分配的情况下改变内部的设计。

总 结

二者最大的区别就是控制逻辑,PLC为固定逻辑器件(通过改变软件实现功能),而PLD为可变逻辑器件(通过改变内部电路结构实现功能)。另外,PLC一般用于弱点驱动强电的场合(自动化专业的朋友们一定很了解),例如大型机床的控制、机械手的控制。而PLD主要用于仿真电路等集成电路前期设计工作,与弱点类控制。

/5

/5