作者:Rachel Courtland

5 年前,英特尔向全球隆重推介了全球目前正在使用的高性能晶体管——鳍式场效晶体管(FinFET)。这个名字系因其外形而确定:该款晶体管的电流通道沿垂直于晶体管表面的方向笔直树立,酷似鱼鳍,而控制晶体管的栅极则覆盖于侧面。在现代微处理器中,当关闭电流时,还是很容易有电流悄悄流过,而这样的设计方案则实现了更严格的电流控制。

但在FinFET于2011年成为市场热点之前,工程师和设备物理学家曾探寻是否存在可能性,将晶体管的尺寸设计成为符合其逻辑允许的尺寸,并使用可充分包裹载流通道的环栅。转至环栅结构设计,从理论上来讲可以帮助芯片公司生产尺寸更小的晶体管,不会泄漏太多电流,并会提高运行速度或改善能源消耗程度。

目前,来自纳电子学研究所微电子研究中心(Imec,总部位于比利时勒芬)的汉斯•默滕斯(Hans Mertens)及其同事使用8纳米宽的密集型纳米线堆栈在传统硅表面上成功安装了环栅式晶体管。尽管仍然存在若干工程问题,但是在未来的几年内,我们可以看到利用该基础方法所实现的改进,或许我们还会看到该类产品进入批量生产阶段。

将使用半导体材料制造的纳米线沿以下方向之一调整位置,即可制造环栅式设备:侧面,如当前晶体管通路的排列方式;或沿垂直方向,如此一来,纳米线即可立于终端之上,垂直于芯片平面。

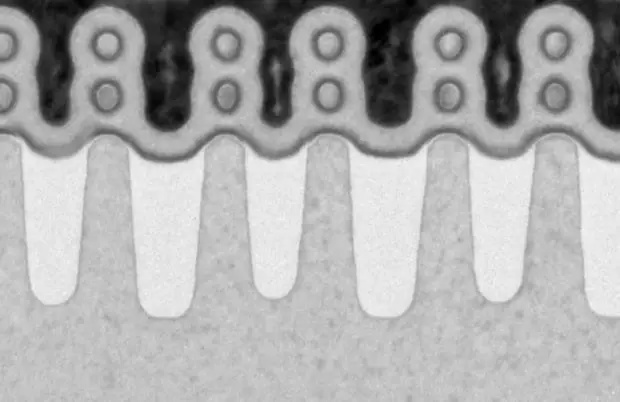

在6月份于檀香山举办的技术与电路座谈会上,Imec团队正式向外界公布了研究成果。该团队选择使用侧面设计。首先,该团队使用硅锗混合材料增设多个分层;随后,将平行槽移除,保留包含多个替代层的“鱼鳍”,有些类似于具有多种沉积岩结构的岩石柱。在该步骤之后,团队移除了剩余硅锗,只在每一鳍中留下两根硅纳米线。

为了成功制造晶体管,团队在每一根纳米线的四周添加了绝缘材料和金属栅极,从而形成栅极结构。对于处于垂直状态的两根纳米线,源极和漏极区域——电流产生区域和流动区域——相互连接,成为同一晶体管的共同组成部分。将纳米线进行堆栈处理能够增加特定面积的电流流量,也就可以提高通过晶体管特定面积的电流。

Imec逻辑程序管理经理纳塔• 赫利古奇(Naoto Horiguchia) 表示:“ 这种方法的最大优势在于,该类晶体管的制造方式与现有高性能芯片中的FinFET的极为接近。这是FinFET向下一代产品的自然演变。”

IBM托马斯沃森研究中心(位于纽约约克敦海茨)的迈克尔• 圭劳恩(MichaelGuillorn)表示,Imec推出的产品是首款规模如此之小的堆栈式纳米线元件。圭劳恩自2009年起便参与实施IBM的环栅设备研究项目。

IBM在去年的超大规模集成电路活动中宣布了他们的研究成果。该研究对按照高级芯片制造水平所制造的单层水平纳米线的性能极限进行了探索。圭劳恩表示,考虑到电阻会随通道宽度的减小而升高,业界普遍担忧纳米线会对电流造成严重的阻碍。但根据IBM集团的研究成果,事实并非如此;同时,上述研究成果也表明,带状的纳米线结构——宽且平(而非正方形或圆形),而且具有十字交叉结构——更有助于提高产品性能。

当然,仍有许多问题需要处理解决。默滕斯表示,需要注意的一点就是将包裹纳米线通道的栅极与源极和漏极区域更好地进行隔离。因为在小型设备中,源极和漏极区域距离栅极过近,可能会通过电容耦合出现能量交换问题。

圭劳恩表示,研究人员正在“逐项勾除”业界认为纳米线不合适的“理由”;他进一步表示,假设工程师能够解决与制造和性能有关的所有缺陷,那么在未来的3到6年内,我们可能会看到芯片制造商批量生产上述元件。具体生产时间取决于公司觉得还能推广FinFET多久,按照何种计划和节奏推出下一代芯片以及他们对于该潜在技术拥有何种野心。圭劳恩表示:“尽早采用环栅技术,能够帮助半导体公司在市场竞争中有效实现差异化。”

/5

/5