The advantage of the latency 0 FIFO is that the read data is available before pop is issued. A couple of examples are given below to demonstrate the ways to use it.

1.1 Pass-thru FIFOPurpose: To store information not used in the current processing stage, and marry them with the result of this stage later.

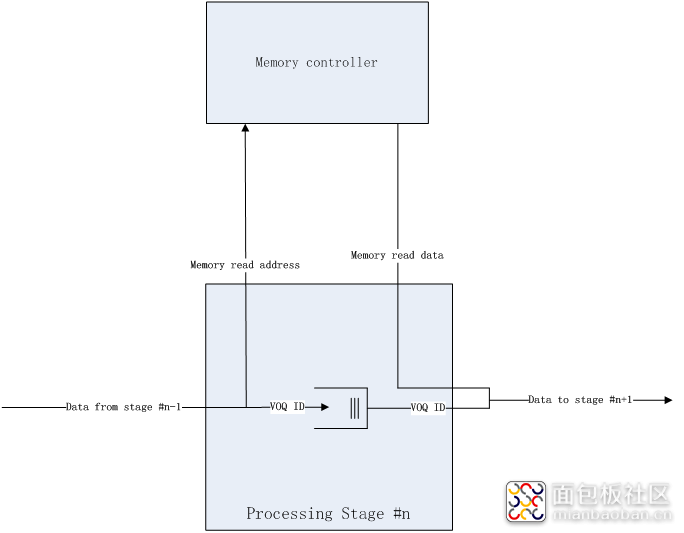

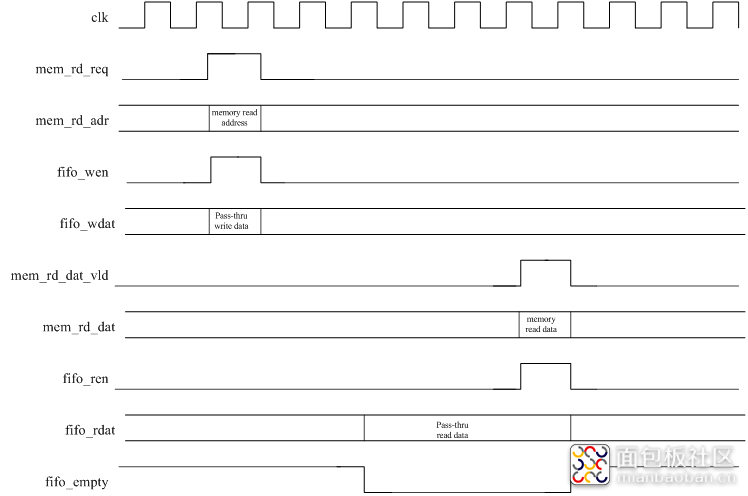

Example: The processing stage is a memory lookup stage. The memory has variable read latency. Part of the data from the previous stage is the memory read address. The other part is the VOQ ID the read data is destined to. The memory read address is sent to the memory controller along with the read request. The VOQ ID is stored in the pass-thru FIFO. When the read data comes back from the memory controller, the VOQ ID is popped from the pass-thru FIFO and married with the memory read data for the next processing stage.

Figure 1 Pass-thru FIFO Usage Example Diagram

Figure 2 Pass-thru FIFO Usage Example Timing Diagram

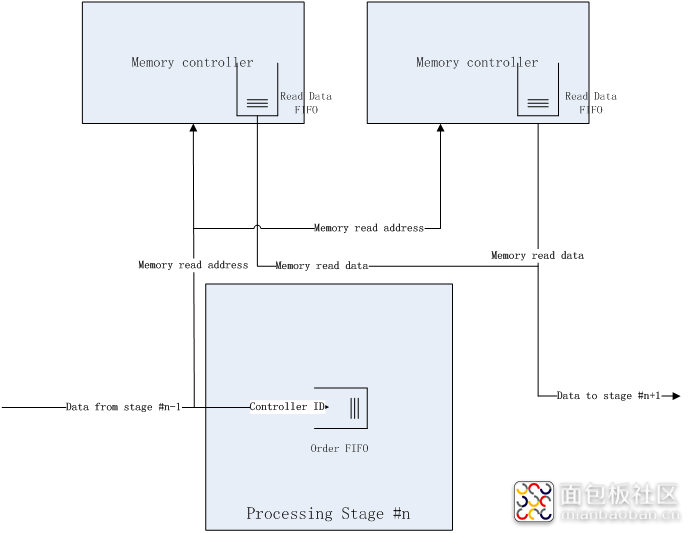

Purpose: When interfacing to multiple memory controllers, read data may come back out of order. Latency 0 FIFO can be used to re-order the data back to its original order.

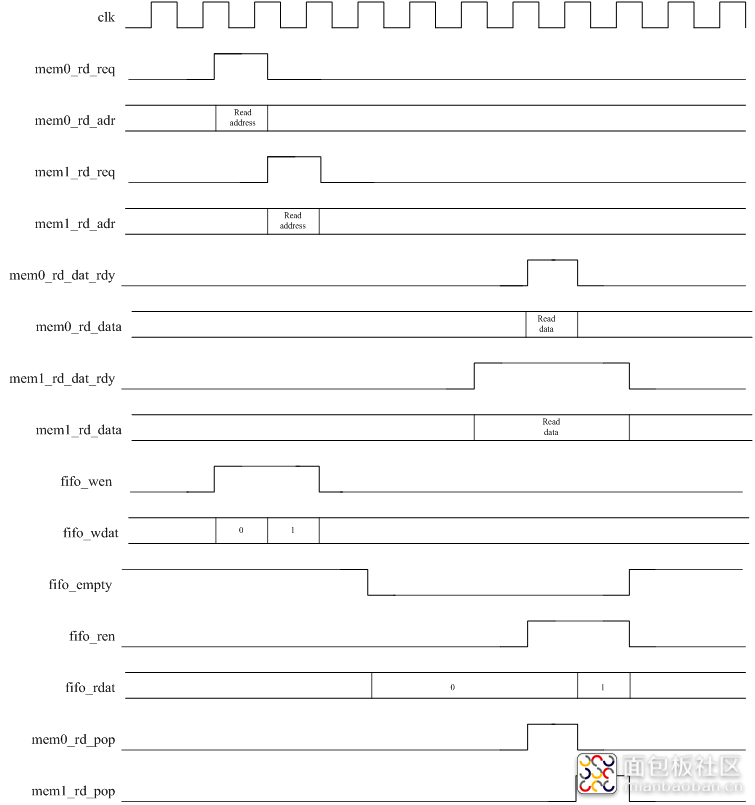

Example: There are two memory controllers. Read data is stored in the read data FIFO in the controllers. An order FIFO is used to store the order of the read requests. The content of the order FIFO is used to decide which controller it should expect the data from.

Figure 3 Re-ordering FIFO Usage Example Diagram

Figure 4 Re-ordering FIFO Usage Example Timing Diagram

/5

/5