什么是运算放大器?

许多教材和参考指南将运算放大器(运放)定义为可以执行各种功能或操作(如放大、加法和减法)的专用集成电路(IC)。虽然我同意这个定义,但仍需注重芯片的输入引脚的电压。

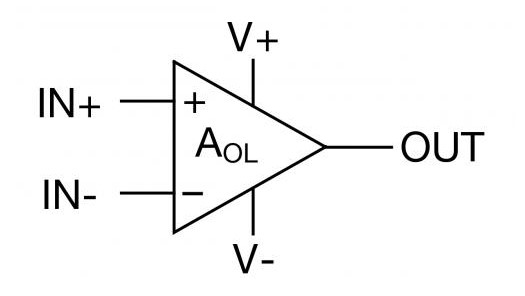

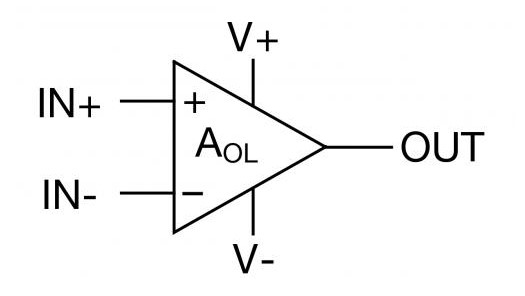

图 1 描述了运算放大器的标准示意图符号。有两个输入端(IN+, IN-)、一个输出端(OUT)和两个电源端(V+, V-)。这些端的名称可能因制造商而异,甚至单个制造商也可能使用不同的名称,但它们仍然是相同的五个端。

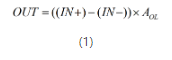

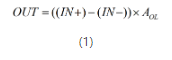

等式 1 表示运算放大器的传递函数:

在等式 1 中,AOL 被称为“开环增益”。在现代运算放大器中,它通常是一个非常大的值(120 dB 或 1,000,000 V/V)。例如,如果 IN+和 IN- 之间的电压差仅为 1mV,运算放大器将尝试输出 1000V!在这种配置中,运算放大器不在线性区域内工作,因为输出不能使输入彼此相等(记住,理想情况下 In+等于 In-)。因此,运算放大器需要一种方法来控制开环增益,即通过负反馈来实现。

在等式 1 中,AOL 被称为“开环增益”。在现代运算放大器中,它通常是一个非常大的值(120 dB 或 1,000,000 V/V)。例如,如果 IN+和 IN- 之间的电压差仅为 1mV,运算放大器将尝试输出 1000V!在这种配置中,运算放大器不在线性区域内工作,因为输出不能使输入彼此相等(记住,理想情况下 In+等于 In-)。因此,运算放大器需要一种方法来控制开环增益,即通过负反馈来实现。

图 3 比较了开环运算放大器和负反馈运算放大器。这些 TINA-TI™软件仿真电路采用的运放是近乎理想的运放,加了电源来限制输出电压。注意,对于左侧的开环配置,输出几乎等于正电源(V+)。这是因为输入引脚之间有一个很小的差异(100mV)。这种小电压被开环增益放大,开环增益会强制输出到其中一个电源电压。在图 3 右侧的负反馈或闭环电路中,运算放大器输出上的分压器需要 200 mV 的输出电压,以便使反相和同相输入相等。

输入电压的放大称为增益。它是反馈回路中电阻值的函数。等式 2 描述了图 3 中右边电路的增益方程,这就是所谓的同相放大器。您将看到计算出的输出电压与仿真相符。如果您想要了解有关此电路(以及其他常见的运算放大器电路,如缓冲器、同相放大器和差分放大器)的更多信息,您可以下载电子书“模拟工程师电路指南:放大器”。”

由于这个限制,在图 5 中可以看到,随着输出接近电源,输入引脚之间的电压差 Vdiff 增加。只有当输入几乎相等时,运算放大器才在线性区域工作。

当输入电压相等时,运算放大器通常在线性范围内工作,而运算放大器正是在线性范围内准确地执行上述功能。然而,运算放大器只能改变一个条件来使输入电压相等,即输出电压。因此,运算放大器的输出通常以某种方式连接到输入,这种通常被称为电压反馈。

在本文中,将解释一个通用电压反馈运算放大器的基本操作。

图 1 描述了运算放大器的标准示意图符号。有两个输入端(IN+, IN-)、一个输出端(OUT)和两个电源端(V+, V-)。这些端的名称可能因制造商而异,甚至单个制造商也可能使用不同的名称,但它们仍然是相同的五个端。

例如,您可能会看到 Vcc 或 Vdd 而不是 V+。又或者,您可能会看到 Vee 或 Vss 而不是 V-。电源端子的其他标签会有所不同,因为它们指的是器件内部的晶体管类型。例如,当在运算放大器内部使用双极结型晶体管(BJT)时,电源对应于 BJT 的集电极和发射极:Vcc 和 Vee。在运算放大器内部使用场效应晶体管(FET)时,电源标签与 FET 的漏极和源极相对应:Vdd 和 Vss。如今,许多运算放大器同时包含 BJT 和 FET,因此 V+和 V- 是常见的标签,与器件内部的晶体管无关。简言之,不要太在意引脚标签,只要理解它们的作用即可。

图 1:通用型运算放大器示意图符号

等式 1 表示运算放大器的传递函数:

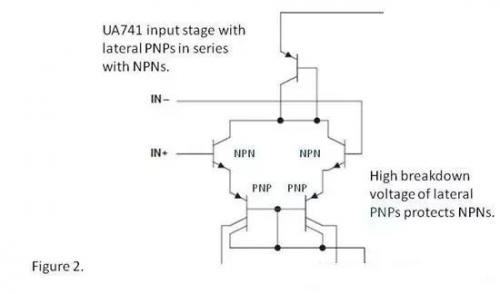

图 2 描述了作为反馈控制系统一部分的运算放大器。您会注意到输出 OUT 通过一个标记为ß的块反馈到负输入 IN-。ß被称为反馈因子,通常使用电阻来降低输出电压。

图 2:负反馈运算放大器

图 3 比较了开环运算放大器和负反馈运算放大器。这些 TINA-TI™软件仿真电路采用的运放是近乎理想的运放,加了电源来限制输出电压。注意,对于左侧的开环配置,输出几乎等于正电源(V+)。这是因为输入引脚之间有一个很小的差异(100mV)。这种小电压被开环增益放大,开环增益会强制输出到其中一个电源电压。在图 3 右侧的负反馈或闭环电路中,运算放大器输出上的分压器需要 200 mV 的输出电压,以便使反相和同相输入相等。

图 3:开环(左)与负反馈(右)

输入电压的放大称为增益。它是反馈回路中电阻值的函数。等式 2 描述了图 3 中右边电路的增益方程,这就是所谓的同相放大器。您将看到计算出的输出电压与仿真相符。如果您想要了解有关此电路(以及其他常见的运算放大器电路,如缓冲器、同相放大器和差分放大器)的更多信息,您可以下载电子书“模拟工程师电路指南:放大器”。”

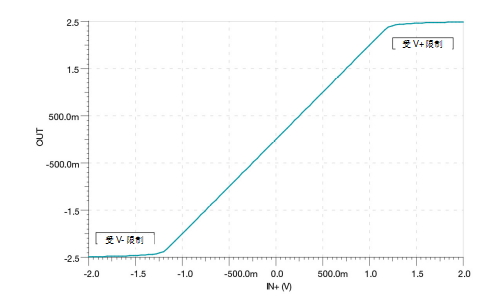

运算放大器的输出受到电源电压的限制。图 4 是图 3 中同相放大器的输出电压与输入电压的关系图。注意当输出接近正负电源时,输出由于饱和受限。

图 4:同相放大器电路的输出与输入电压

由于这个限制,在图 5 中可以看到,随着输出接近电源,输入引脚之间的电压差 Vdiff 增加。只有当输入几乎相等时,运算放大器才在线性区域工作。

图 5:同相放大器电路的 Vdiff 和 IN+

运算放大器的常见指标及重要特性

▶ 输入失调电压(Offset Voltage,VOS)

定义:在运放开环使用时, 加载在两个输入端之间的直流电压使得放大器直流输出电压为 0。优劣范围:1µV 以下,属于极优秀的。100µV 以下的属于较好的。最大的有几十mV。

对策:

1、选择 VOS远小于被测直流量的放大器,

2、过运放的调零措施消除这个影响

3、如果你仅关心被测信号中的交变成分,你可以在输入端和输出端增加交流耦合电路,将其消除。

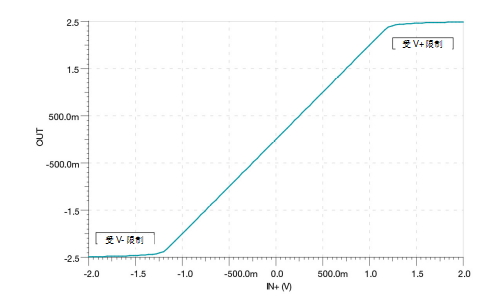

如果 IB1=IB2,那么选择 R1=R2//RF,可以使电流形成的失调电压会消失。但实际中IB1=IB2很难满足

▶ 失调电压漂移(Offset Voltage Drift)

定义:当温度变化(µV/°C)、时间持续(µV/MO)、供电电压(µV/V)等自变量变化时, 输入失调电压会发生变化。

后果:很严重。因为它不能被调零端调零,即便调零完成,它还会带来新的失调。

对策:第一, 就是选择高稳定性,也就是上述漂移系数较小的运放。第二,有些运放具有自归零技术,它能不断地测量失调并在处理信号过程中把当前失调电压减掉。

▶ 输入偏置电流(Input bias current, IB)

定义:当输出维持在规定的电平时,两个输入端流进电流的平均值。Ib=(Ib1+Ib2)/2

优劣范围:60fA~100µA。

后果:第一,当用放大器接成跨阻放大测量外部微小电流时,过大的输入偏置电流会分掉被测电流,使测量失准。第二,当放大器输入端通过一个电阻接地时,这个电流将在电阻上产生不期望的输入电压。

对策:为避免输入偏置电流对放大电路的影响,最主要的措施是选择 IB较小的放大器。

▶ 输入失调电流(Input offset current, IOS)

定义:当输出维持在规定的电平时,两个输入端流进电流的差值。

优劣范围:20fA~100µA。Ib=Ib1-Ib2

后果:失调电流的存在,说明两个输入端客观存在的电流有差异,无法用外部电阻实现匹配抵消偏置电流的影响。

▶ 噪声指标(Noise)

运放常见的噪声根源有两类,一类为 1/f 噪声,其电能力密度曲线随着频率的上升而下降; 一类为白噪声,或者叫平坦噪声,其电能力密度曲线是一条直线,与频率无关。

如何根据datasheet估算运放的噪声?

如何计算电阻的噪声??

噪声的有效值和峰峰值关系:噪声峰峰值为噪声有效值的 6.6 倍。

▶ 输入电压范围(Input Voltage Range)

定义:保证运算放大器正常工作的最大输入电压范围。也称为共模输入电压范围。

当运放最大输入电压范围与电源范围比较接近时,比如相差 0.1V 甚至相等、超过,都可以叫“输入轨至轨”,表示为 Rail-to-rail input,或 RRI。

理解:运放的两个输入端,任何一个的输入电压超过此范围,都将引起运放的失效。注意,超出此范围并不代表运放会被烧毁,但绝对参数中出现的此值是坚决不能超过的。

▶ 输出电压范围(VOH/VOL 或者 Swing from rail)

定义:在给定电源电压和负载情况下,输出能够达到的最大电压范围。当运放的输出范围已经接近于电源电压范围时,就自称“输出轨至轨”,表示为 Rail-to-rail output,或 RRO。

理解:在没有额外的储能元件情况下,运放的输出电压不可能超过电源电压范围,随着负载的加重,输出最大值与电源电压的差异会越大。

▶ 输出电压范围,或者输出至轨电压有如下特点:

1) 正至轨电压与负至轨电压的绝对值可能不一致,但一般情况下数量级相同;

2) 至轨电压与负载密切相关,负载越重(阻抗小) 至轨电压越大;

3) 至轨电压与信号频率相关,频率越高,至轨电压越大,甚至会突然大幅度下降;

4) 至轨电压在 20mV 以内,属于非常优秀。

5) RRIO(输入输出均轨至轨)

运算放大器的好坏判别方法

运算放大器好坏的判别对相当多的电子维修者有一定的难度,不只文化程度的关系(手下有许多本科生,不教的话肯定不会,教了也要好久才领会,还有个专门跟导师学变频控制的研究生,居然也是如此!),在此与大家共同探讨一下,希望对大家有所帮助。

理想运算放大器具有“虚短”和“虚断”的特性,这两个特性对分析线性运用的运放电路十分有用。为了保证线性运用,运放必须在闭环(负反馈)下工作。如果没有负反馈,开环放大下的运放成为一个比较器。如果要判断器件的好坏,先应分清楚器件在电路中是做放大器用还是做比较器用。

根据放大器虚短的原理,就是说如果这个运算放大器工作正常的话,其同向输入端和反向输入端电压必然相等,即使有差别也是 mv 级的,当然在某些高输入阻抗电路中,万用表的内阻会对电压测试有点影响,但一般也不会超过 0.2V,如果有 0.5V 以上的差别,则放大器必坏无疑!(我是用的 FLUKE179 万用表)

如果器件是做比较器用,则允许同向输入端和反向输入端不等,

同向电压>反向电压,则输出电压接近正的最大值;

同向电压<反向电压,则输出电压接近 0V 或负的最大值(视乎双电源或单电源)。

如果检测到电压不符合这个规则,则器件必坏无疑!

这样你不必使用代换法,不必拆下电路板上的芯片就可以判断运算放大器的好坏了。

运算放大器好坏的判别对相当多的电子维修者有一定的难度,不只文化程度的关系(手下有许多本科生,不教的话肯定不会,教了也要好久才领会,还有个专门跟导师学变频控制的研究生,居然也是如此!),在此与大家共同探讨一下,希望对大家有所帮助。

理想运算放大器具有“虚短”和“虚断”的特性,这两个特性对分析线性运用的运放电路十分有用。为了保证线性运用,运放必须在闭环(负反馈)下工作。如果没有负反馈,开环放大下的运放成为一个比较器。如果要判断器件的好坏,先应分清楚器件在电路中是做放大器用还是做比较器用。

根据放大器虚短的原理,就是说如果这个运算放大器工作正常的话,其同向输入端和反向输入端电压必然相等,即使有差别也是 mv 级的,当然在某些高输入阻抗电路中,万用表的内阻会对电压测试有点影响,但一般也不会超过 0.2V,如果有 0.5V 以上的差别,则放大器必坏无疑!(我是用的 FLUKE179 万用表)

如果器件是做比较器用,则允许同向输入端和反向输入端不等,

同向电压>反向电压,则输出电压接近正的最大值;

同向电压<反向电压,则输出电压接近 0V 或负的最大值(视乎双电源或单电源)。

如果检测到电压不符合这个规则,则器件必坏无疑!

这样你不必使用代换法,不必拆下电路板上的芯片就可以判断运算放大器的好坏了。

哪些时候运算放大器代替不了比较器?

许多人偶尔会把运算放大器当比较器使用。一般而言,当您只需要一个简单的比较器,并且您在四运算放大器封装中还有一个“多余”运算放大器时,这种做法是可行的。稳定运算放大器运行所需的相位补偿意味着把运算放大器用作比较器时其速度会非常的低,但是如果对速度要求不高,则运算放大器可以满足需求。偶尔会有人问到我们运算放大器的这种使用方法。这种方法有时有效,有时却不如人们预期的那样效果好。为什么会出现这种情况呢?

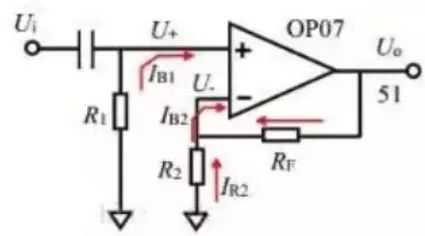

许多运算放大器都在输入端之间有电压钳位,其大多数一般都使用背靠背二极管(有时使用两个或者更多的串联二极管)来实施。这些二极管保护输入晶体管免受其基极结点反向击穿的损害。差动输入为约 6V 时便会出现许多 IC 工艺击穿,这会极大地改变或者损坏晶体管。下图显示了 NPN 输入级,D1 和 D2 提供了这种保护功能。

问题是我们(包括其他运算放大器厂商)并没有总是说明这些钳位的存在。即使有所说明,我们可能也不会做详细的解释或者阐述。也许我们应该说:“用作比较器时,请小心谨慎!”产品说明书的作者们通常也只是假设您肯定会把运算放大器当作运算放大器用。最近,我们在美国亚利桑那州图森产品部召开了一个会议。会议决定,我们以后将会更加清楚地说明这种情况。但是,现在已经生产出来的运算放大器怎么办呢?下列指导建议可能会对您有所帮助:

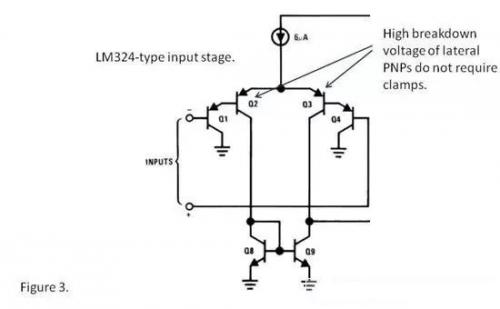

一般而言,双极 NPN 晶体管运算放大器都有输入钳位,例如:OP07、OPA227 和 OPA277 等。uA741 是一个例外,它具有 NPN 输入晶体管,并且有一些为 NPN 提供固有保护的附加串联横向 PNP。

使用横向 PNP 输入晶体管的通用运算放大器一般没有输入钳位,例如:LM324、LM358、 OPA234、OPA2251 和 OPA244。这些运算放大器一般为“单电源”类型,其意味着它们拥有一个扩展至负电源端(或者稍低)的共模范围。输入偏置电流为一个负数时,表示输入偏置电流自输入引脚流出。这时,我们通常可以认定它们为这类运算放大器。但是,需要注意的是,使用 PNP 输入的高速运算放大器一般有输入钳位,而这些 PNP 是一些具有更低击穿电压的垂直 PNP。

大多数低压 CMOS 运算放大器都没有钳位。自动归零或者斩波器类型是一个特例,其可能具有类似钳位的行为表现。

底线是……如果您考虑把运算放大器用作比较器,请一定小心谨慎。仔细阅读产品说明书,不要漏掉一点信息,包括应用部分的一些注解内容。在电路试验板或者样机中验证其表现,查看一个输入电压对另一个输入电压的影响。不要依赖 SPICE 宏模型。一些宏模型可能并不包括对钳位建模的一些额外组件。另外,当您笨手笨脚地把运算放大器从一个轨移动到另一个轨时可能出现其他一些现象,我们可能无法精确地对这些现象建模。

来源:网络

/5

/5

好东西要支持