在1990年代早期,IBM开创了基于处理器的仿真技术,这是他们早期工作的一个分支。基于硬件的仿真引擎。硬件技术由大量布尔处理器组成,这些处理器能够以非常高的速度相互共享数据。软件技术包括在许多处理器之间划分设计,并以正确的时间顺序和最佳方式调度各个布尔运算。

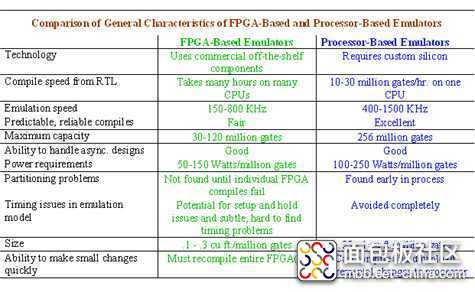

]最初,性能无法与基于FPGA的仿真器匹配,但编译时间不到一小时,消除了困扰基于FPGA的仿真器的时序问题,使新技术对许多使用模型很有吸引力,特别是模拟加速。该技术的后代最终在仿真速度上超越了FPGA系统,同时保留了编译时间的巨大优势?并且没有一百台PC的农场用于编译。

软件技术的进步扩展了基于处理器的仿真器的应用,以处理具有任意数量时钟的异步设计。其他扩展支持设计中所有信号的100%可见性,从仿真运行开始的任何时间对所有信号的可见性,以及逻辑分析器触发事件的动态设置,无需重新编译。在基于FPGA的系统的仿真速度不断降低的同时,新一代基于处理器的系统不仅以惊人的速度提高了仿真速度,而且还证明了其容量可扩展到数亿个门。

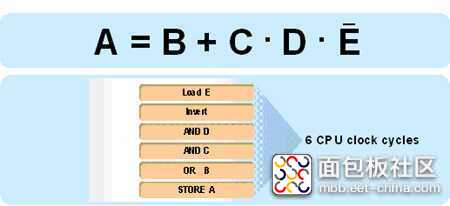

了解处理器的方式基于仿真器的工作原理,简要回顾一下逻辑仿真器的工作原理很有用。回想一下,计算机的ALU(算术逻辑单元)可以对变量执行基本的布尔运算,例如AND,OR,NOT,并且诸如“always @(posedge Clock)Q = D”之类的语言构造构成了a的基础。拖鞋。

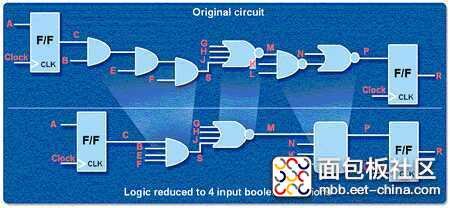

在门(和透明锁存器)的情况下,模拟顺序很重要。信号通过门链示意性地“从左到右”竞争,或者在RTL源代码中“从上到下”。触发器(寄存器)打破门链以进行排序。

一种类型的模拟器,一个分级编译逻辑模拟器,以正确的顺序一次一个地执行布尔方程。 (时间延迟与功能逻辑仿真无关。)如果有两个ALU可用,您可以想象将设计分解为两个独立的逻辑链并将每个链分配给ALU,从而并行化并减少所需的时间,也许是一半。

[基于处理器的仿真器具有数万到数十万个ALU,这些ALU可以有效地进行调度,以正确的顺序执行设计中的所有布尔方程。以下系列图纸说明了这一过程。对于此示例,我们假设模拟器中有一个4输入布尔基元。

将逻辑简化为四输入函数后的布尔方程组是:

IF(时钟上升) C = A

S = C& B& E& F

M = NOT(G + H + J + S)

P = NOT(N + NOT(M& K& L))

IF(时钟上升)R = P

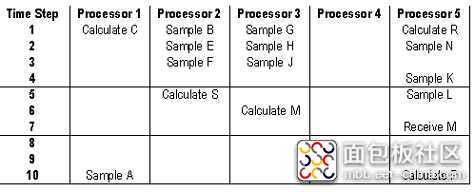

此外,以下排序约束集适用:

必须首先评估触发器

必须在M之前计算S

M必须在P

之前计算

在计算S之前必须对主输入B,E和F进行采样

在计算M之前必须对主输入G,H和J进行采样

在计算P之前必须对主输入K,L和N进行采样

注意:在触发器之后的任何时间都可以对主输入A进行采样

/5

/5