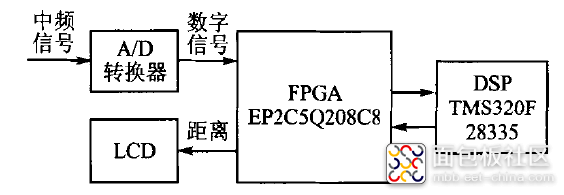

在雷达信号处理系统中,数据的流向如图所示。首先FPGA接收高速并行A/D转换的数字信号,DSP读取FPGA获取的信号序列并进行数字信号处理,得到距离信息,然后DSP将距离信息发送至FPGA,FPGA控制LCD显示屏显示距离信息。

FPGA的设计采用VHDL硬件描述语言,利用内部RAM资源生成FIFO模块,将FPGA的FIFO模块作为DSP的外围设备,DSP根据FIFO的存储状态,通过外部接口XINTF对FIFO模块进行读写操作。

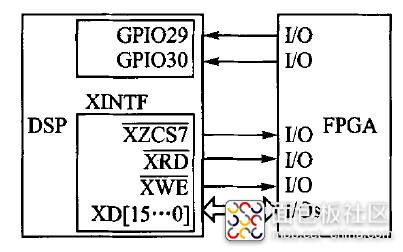

根据设计思想,搭建了DSP和FPGA通信的硬件实验平台,硬件连接示意图如图所示。

TMS320F28335 DSP支持16位和32位XINTF数据总线,在这里使用16位数据总线进行通信,将DSP的数据总线、(读写)使能信号和ZONE7的选通信号XZCS7与FPGA的通用I/O口连接。此外,选用DSP的两个可编程通用输入/输出引脚与FPGA通用I/O口相连,使FIFO的满信号作为DSP的中断输人,空信号作为数据读取完毕状态信号输入DSP。

/5

/5