一、新建Vivado工程

1、创建工程。File-New Project-Create a New Vivado Project-next

填写工程名、工程路径-next

2、Project Type-新建一个 RTL 工程,并且勾选不要添加源文件,单击 NEXT

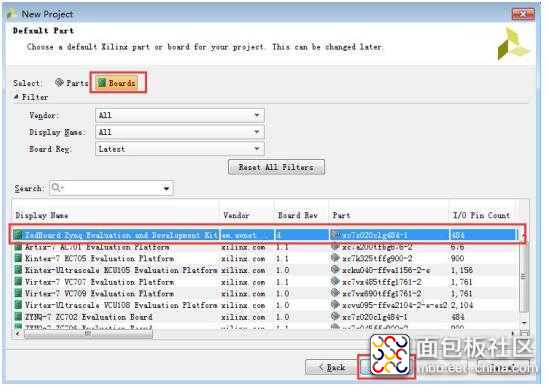

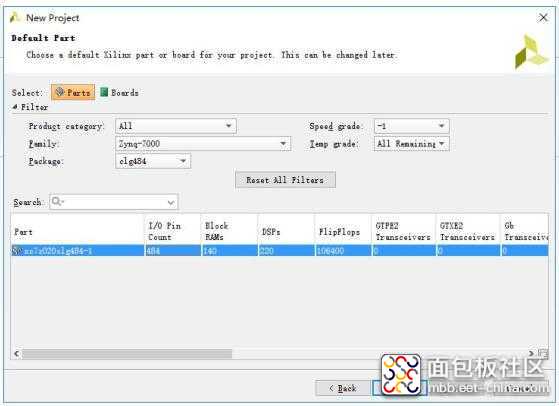

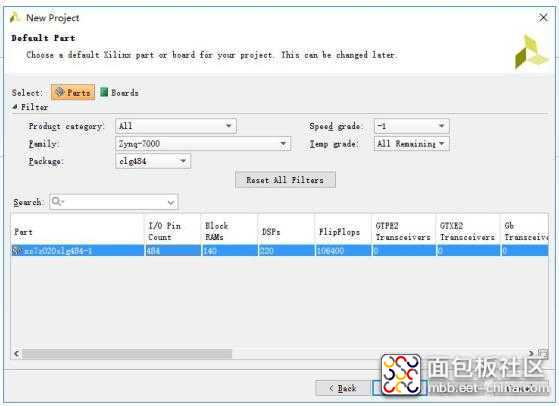

3、指定所用开发板或芯片。用zedboard时选择

4、最后单击 Finish 完成工程的创建

二、创建工程文件

1、打开 VIVADO 软件

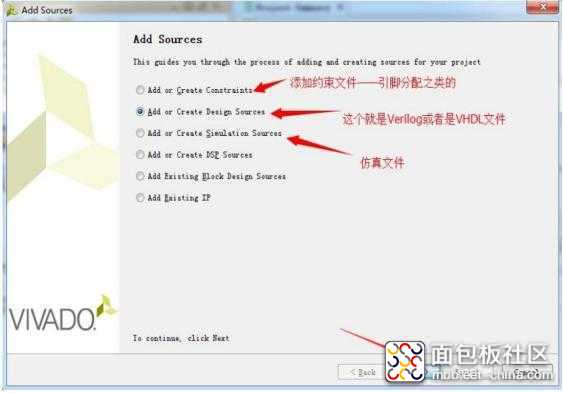

2、单击Add source

选择单击 Add or Create Design Sources 然后单击 NEXT

3、单击 Create File 来创建文件

文件类型选择Verilog,填写文件名

4、完成创建

5、编辑verilog文件

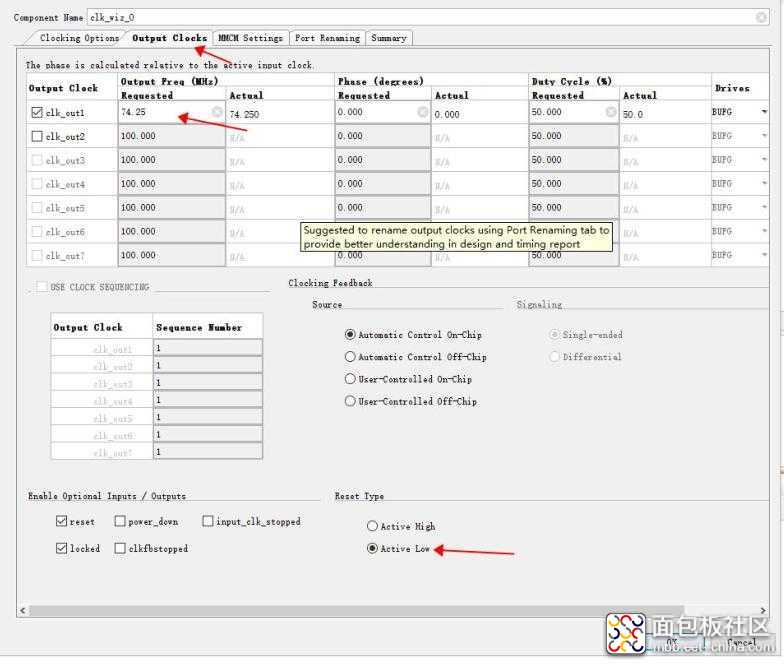

6、单击 ,添加一个时钟管理器,为系统提供时钟。

配置好后单击generate

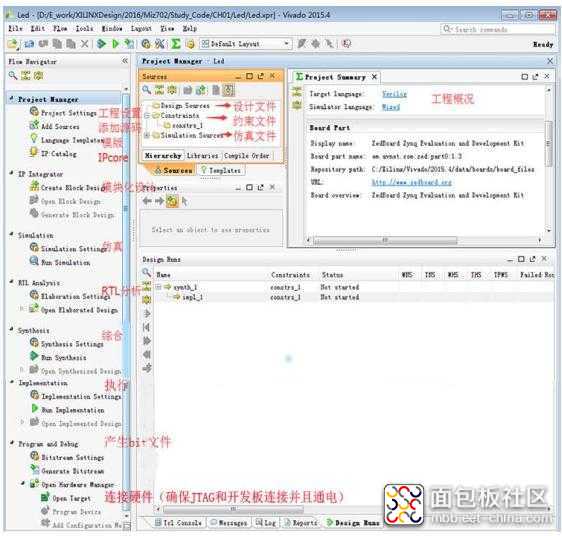

三、约束、综合、实现、生成可执行文件、下载

1、单击 Add Sources。

2、选择 Add or create constraints 然后单击 NEXT。

3、单击 Create File。

填写文件名、单击ok.

4、打开约束文件,添加约束。

5、综合、执行、生成.bit文件

6、下载程序

(1)给开发板通电,并且连接下载器。

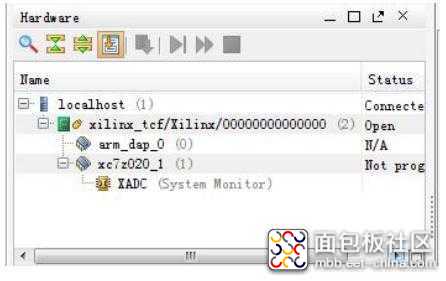

(2)单击 OpenTarget 然后单击 Auto Connect

(3)连接成功后,会显示所连接的器件

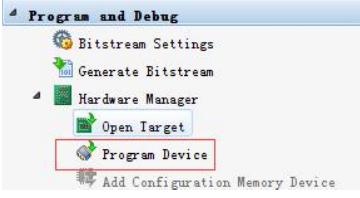

(4)单击 Program Device

(5)弹出的对话框中有我们要下载的 Bit 文件

/5

/5