那么是什么原因导致共模噪声抑制效果不明显呢?

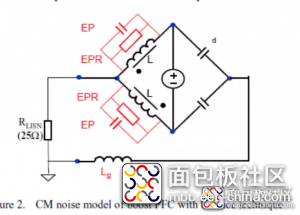

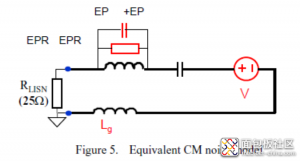

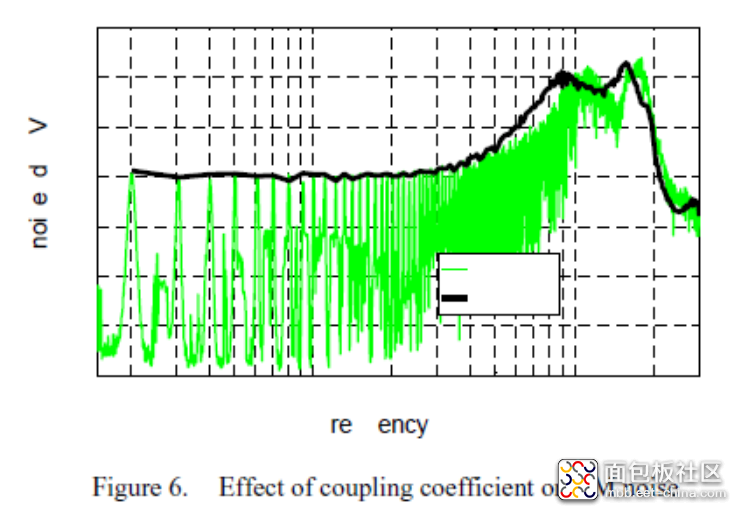

首先考虑电感非全耦合的情况,可以对共模噪声路径进行如下等效:

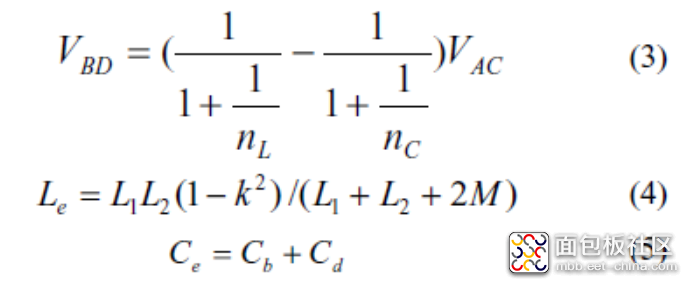

戴维南等效后的参数如下:

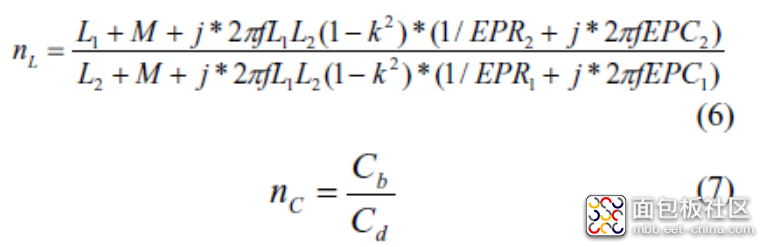

式中k为耦合系数,nL和nc如下:

可见,如果nc=nL,则能达到共模噪声抵消的目的,但因为考虑了共模电感寄生参数的影响,在非全耦合的情况下,无法在全频段保证nc=nL,从共模噪声的角度分析,应尽量保证nc与nL相等。从设计EMI滤波器的角度看,低频段的噪声幅值一般较高,因此一般应保证低频段噪声能够抵消,即满足:

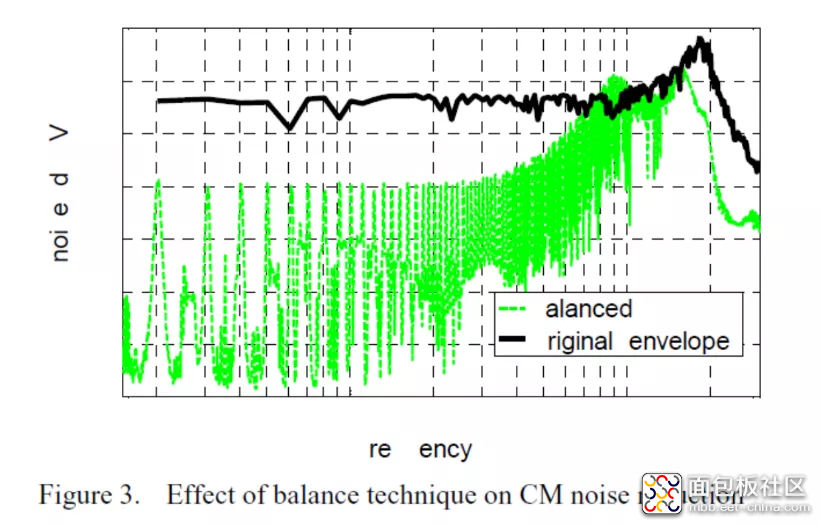

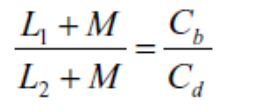

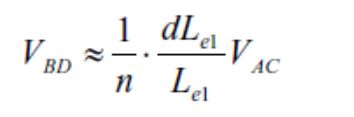

在高频段因为寄生参数以及耦合系数的影响无法保证能供实现共模噪声抵消,但耦合系数的影响有多大,需要考虑。CE的频率范围是150kHz~30MHz,只要在该频段内保证共模噪声得到抑制即可。文章通过对比两种耦合系数的共模抑制效果说明耦合系数在这里并不是关键参数,即耦合系数的变化对共模噪声抑制的效果基本不变。如下图,分别为耦合系数0.8和0.94的共模噪声。

那是什么影响的高频段噪声呢?

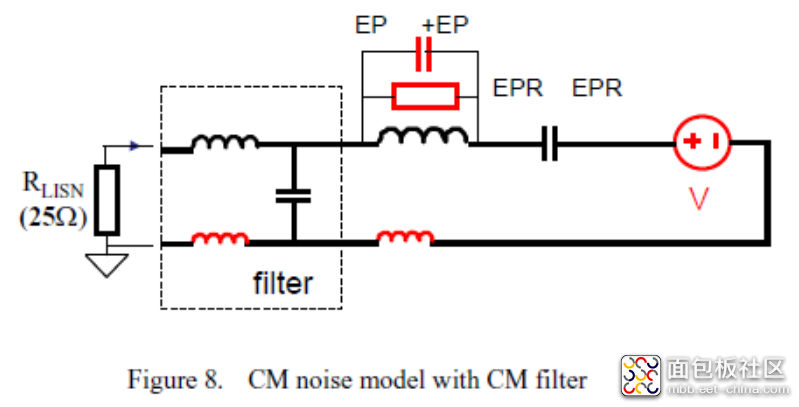

再看上图,如果不考虑EPR和EPC,Lg+Le与Ce在某一频率会发生谐振,那么等效共模噪声源VBD全加在LISN上,势必会导致共模噪声更大。将Le1和Le2分别代表nL的分子和分母,因为实际中肯定会存在偏差使VBD不为0,假设Le1存在偏差dLe1,那么VBD可以表示成下式:

所以为了减小VBD的幅值,可以使用更高的变比n。下图(均实现了低频段的共模噪声抵消)为耦合电感L2的匝数分别为4匝和1匝,可以看出,减小L2的匝数,即增加匝比,使得共模噪声在高频段第一个高点显著减小,并移向更低的频率,实际参数与图中的频率也是对应的,具体参数见论文。

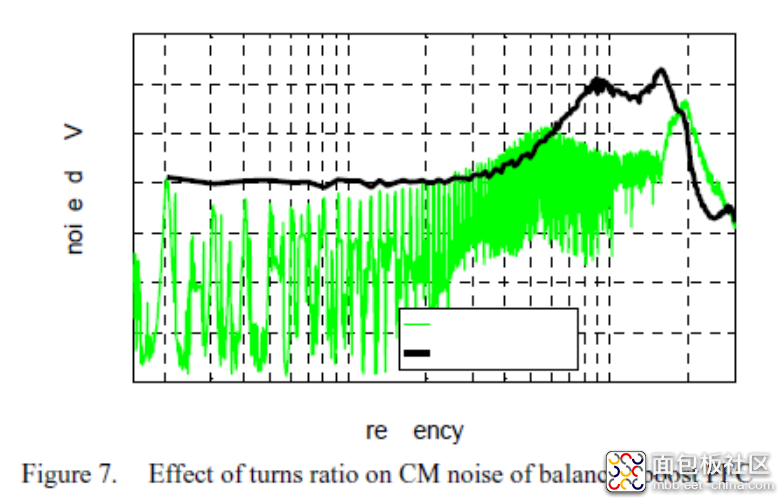

实际中如果加入共模滤波器,上述谐振频率又会发生变化,等效电路如下:

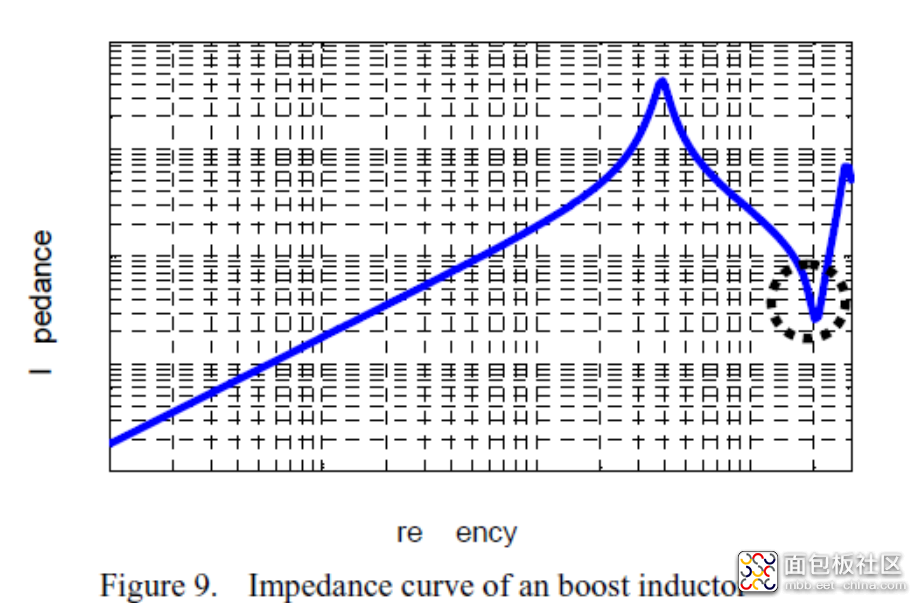

高频段第一个峰值减小了,第二个依然较高,这个噪声是因为在该频率点上,PFC电感达到了其谐振点,电感的阻抗下降明显,电感阻抗随频率变化如下:

因为L2的仅有1匝,所以耦合电感寄生参数主要是L1产生的。有什么办法提高共模电感的谐振频率呢,如果将其提高到30MHz以上将对CE共模噪声影响很小。可行的办法是减小电感匝数,可以通过使用高磁导率的磁芯、使用Ae更大的磁芯,或者通过交错并联降低其中一路的匝数实现。

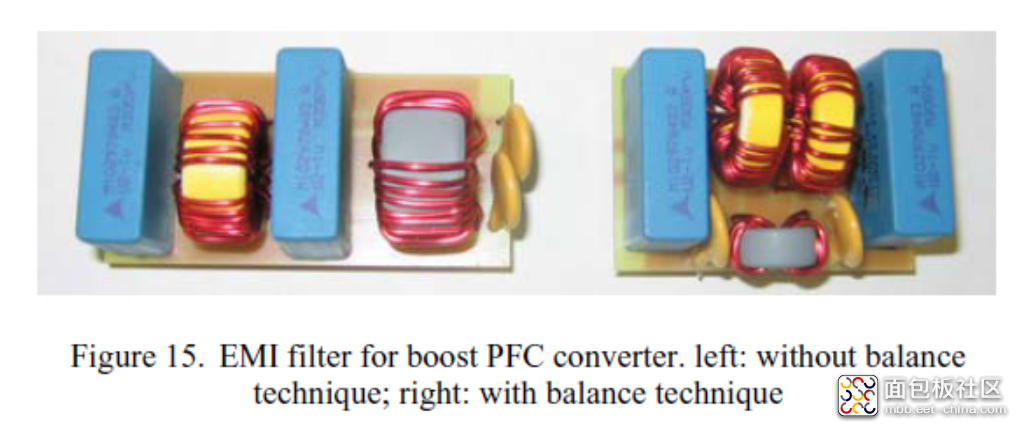

采用平衡技术能够显著减小共模滤波器尺寸,但是共模滤波器尺寸减小,会导致其漏感减小,差模电感较优化前的小很多,所以还应该在加入一个小差模电感,但总的尺寸还是减小的。

内容转载自应用电子笔记,仅供学习交流使用,如有侵权,请联系删除。

/2

/2