目前主流的FPGA仍是基于查找表技术的,已经远远超出了先前版本的基本性能,并且整合了常用功能(如RAM、时钟管理和DSP)的硬核(ASIC型)模块。FPGA芯片主要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

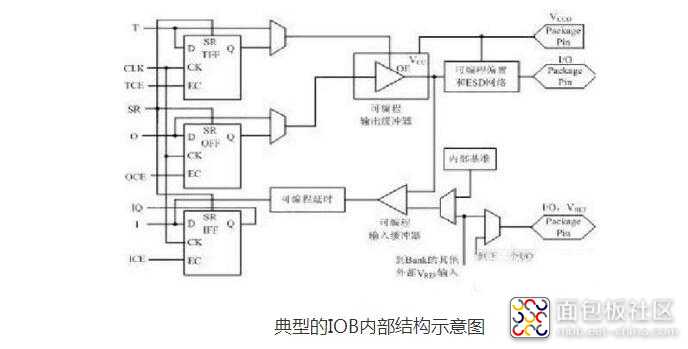

1.可编程输入输出单元(IOB)

可编程输入/输出单元简称I/O单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求。为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。只有相同电气标准的端口才能连接在一起,VCCO电压相同是接口标准的基本条件。

2.可配置逻辑块(CLB)

CLB是FPGA内的基本逻辑单元。CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都包含一个可配置开关矩阵,此矩阵由4或6个输入、一些选型电路(多路复用器等)和触发器组成。开关矩阵是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或RAM。

3.嵌入式块RAM(BRAM)

大多数FPGA都具有内嵌的块RAM,这大大拓展了FPGA的应用范围和灵活性。块RAM可被配置为单端口RAM、双端口RAM、内容地址存储器(CAM)以及FIFO等常用存储结构。CAM存储器在其内部的每个存储单元中都有一个比较逻辑,写入CAM中的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址,因而在路由的地址交换器中有广泛的应用。除了块RAM,还可以将FPGA中的LUT灵活地配置成RAM、ROM和FIFO等结构。在实际应用中,芯片内部块RAM的数量也是选择芯片的一个重要因素。

4.丰富的布线资源

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;第二类是长线资源,用以完成芯片Bank间的高速信号和第二全局时钟信号的布线;第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的结果有密切、直接的关系。

5.底层内嵌功能单元

内嵌功能模块主要指DLL(DelayLockedLoop)、PLL(PhaseLockedLoop)、DSP和CPU等软处理核。现在越来越丰富的内嵌功能单元,使得单片FPGA成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向SOC平台过渡。

DLL和PLL具有类似的功能,可以完成时钟高精度、低抖动的倍频和分频,以及占空比调整和移相等功能。

6.内嵌专用硬核

内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA处理能力强大的硬核(HardCore),等效于ASIC电路。为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用的硬核。例如:为了提高FPGA的乘法速度,主流的FPGA中都集成了专用乘法器;为了适用通信总线与接口标准,很多高端的FPGA内部都集成了串并收发器(SERDES),可以达到数十Gbps的收发速度。

FPGA基础入门到高手相关知识:

1、FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用 的(JTAG)配置方式。

AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列。如EPC S1,EPCS4配置器件专供AS模式,目前只支持 Cyclone系列。使用Altera串行配置器件来完成。Cyclone期间处于主动地位,配置期间处于从属地位。配置数据通过DATA0引脚送入 FPGA。配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。PS则由外部计算机或控制器控制配置过程。通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。 FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

专用配置器件:epc型号的存储器

常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等

对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列。如EPCS1,EPCS4配置器件也是串行配置的。注意,他们只适用于cyclone系列。 除了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升配置了配置速度。当然所外挂的电路也和PS有一些区别。还有处理器配置比如JRUNNER 等等,如果需要再baidu吧,至少不下十种。比如Altera公司的配置方式主要有Passive Serial(PS),Active Serial(AS),Fast Passive Parallel(FPP),Passive Parallel Synchronous(PPS),Passive Parallel Asynchronous(PPA),Passive Serial Asynchronous(PSA),JTAG等七种配置方式,其中Cyclone支持的配置方式有PS,AS,JTAG三种。

2、对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的‘nCONFIG,nSTATUS’应该上拉,要是考虑多种配置模式,可以采用跳线设计。让配置方式在跳线中切换,上拉电阻的阻值可以采用10K。

3、在PS模式下tip:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号。(祥见下图)。一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序。只有在调试完成以后,才把程序烧在配置芯片中, 然后将芯片焊上。或者配置芯片就是可以方便取下焊上的那种。这样出了问题还可以方便地调试。

在AS模式下tip: 用过一块板子用的AS下载,配置芯片一直是焊在板子上的,原来AS方式在用线缆对配置芯片进行下载的时候,会自动禁止对FPGA的配置,而PS方式需要电路上隔离。

4、一般是用jtag配置epc2和flex10k,然后 epc2用ps方式配置flex10k.这样用比较好。(这是我在网上看到的,可以这样用吗?怀疑中)望达人告知。

5、下载电缆,Altera下的下载电缆分为byteblaster和byteblasterMV,以及ByteBlaster II,现在还推出了基于USB-blaster.由于BB基本已经很少有人使用,而USB-Blaster现在又过于昂贵,这里就说一下BBII和 BBMV的区别。

BBII支持多电压供电5.5v,3.3v,2.5v,1.8v;BBII支持三种下载模式:AS,可对Altera的As串行配置芯片(EPCS系列)进行编程 PS,可对FPGA进行配置 JTAG,可对FPGA,CPLD,即Altera配置芯片(EPC系列)编程 而BBMV只支持PS和JTAG

6、一般在做FPGA实验板,(如cyclone系列)的时候,用AS+JTAG方式,这样可以用JTAG方式调试,而最后程序已经调试无误了后,再用 AS模式把程序烧到配置芯片里去,而且这样有一个明显的优点,就是在AS模式不能下载的时候,可以利用Quartus自带的工具生成JTAG模式下可以利用的jic文件来验证配置芯片是否已经损坏。

7、Altera的FPGA可以通过单片机,CPLD等加以配置,主要原理是满足datasheet中的时序即可,这里我就不多说了,有兴趣的朋友可以看看下面几篇文章,应该就能够明白是怎么回事了。

8、配置时,quartus软件操作部分:

(1)assignment--》device--》device&pin options--》选择configuration scheme,configuaration mode,configuration device,注意在不支持远程和本地更新的机器中configuration mode不可选择,而configuration device中会根据不同的配置芯片产生pof文件, 如果选择自动,会选择最小密度的器件和适合设计。

(2)可以定义双口引脚在配置完毕后的作用,在刚才的device&pin option--》dual-purpose pins--》,可以在配置完毕后继续当I/O口使用

(3)在general菜单下也有很多可钩选项,默认情况下一般不做改动,具体用法参见alter a configuration handbook,volume2,sectionII.

(4)关于不同后缀名的文件的适用范围: sof(SRAM Object File)当直接用PS模式下将配置数据下到FPGA里用到,USB BLASTER,MASTERBLASER,BBII,BBMV适用,quartusII会自动生成,所有其他的配置文件都是由sof生成的。 pof(Programmer Object File)也是由quartusII自动生成的,BBII适用,AS模式下将配置数据下到配置芯片中rbf(Raw Binary File)用于微处理器的二进制文件。在PS,FPP,PPS,PPA配置下有用处rpd(Raw Programing Data File)包含bitstream的二进制文件,可用AS模式配置,只能由pof文件生成hex(hexadecimal file)这个就不多说了,单片机里很多ttf(Tabular Text File)适用于FPP,PPS,PPA,和bit-wide PS配置方式sbf(Serial Bitstream File)用PS模式配置Flex 10k和Flex6000的jam(Jam File)专门用于program,verigy,blank-check。

/2

/2