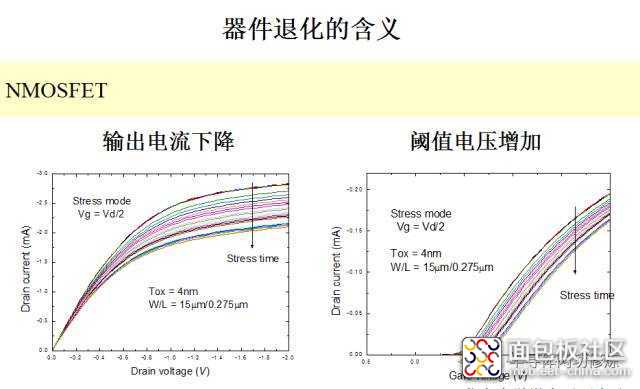

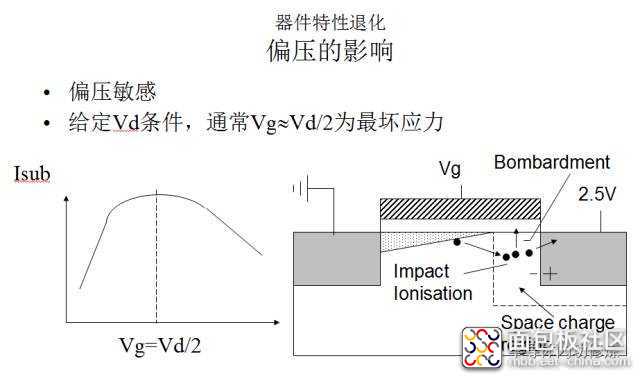

器件退化的含义:也就是随着应力时间的推移,输出电流下降,同时阈值电压增加,至于Vg=Vd/2的含义,简单讲,栅电压时漏电压一半的时候,衬底电流最大,同时漏端因为夹断点推移而出现的空间电荷区的场强最强,从而导致热载流子最严重,所以器件最容易退化。

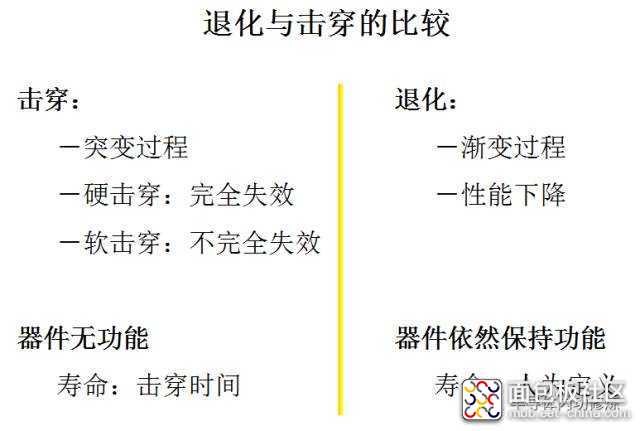

我们来对比一下器件退化与击穿的差异:尽管没有击穿,但是器件也是性能发生了降低,也就是会影响器件的使用寿命。

器件寿命的定义:

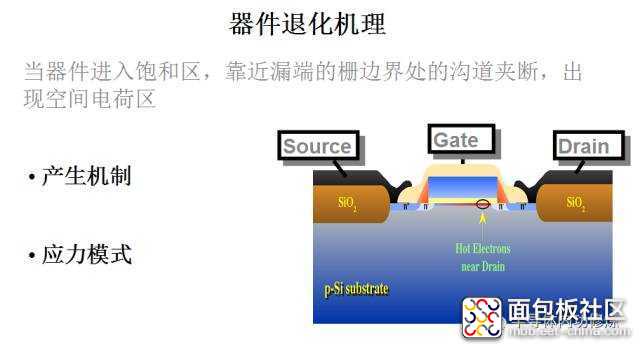

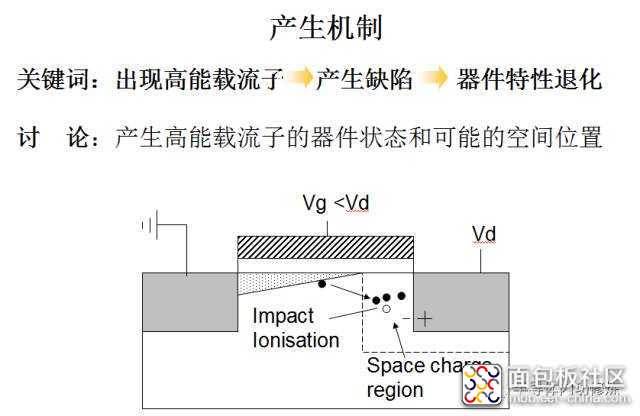

下面我们来介绍器件退化的机理:

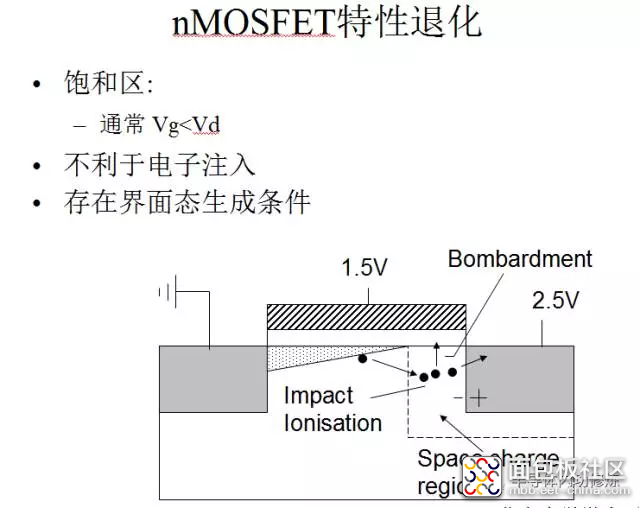

如前所讲,器件出现夹断点时,也就是器件进入饱和工作区时,漏端出现空间电荷区,从而出现热载流子效应。

产生机制:

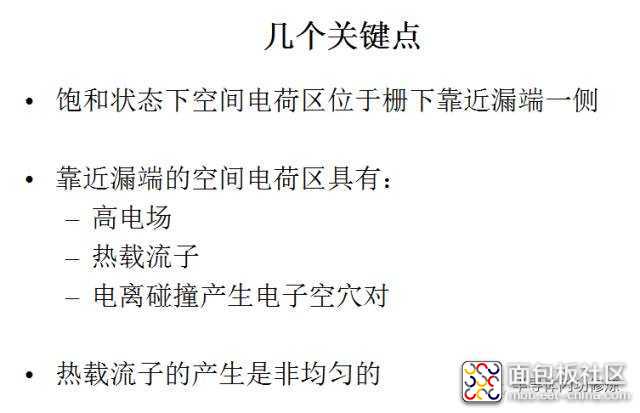

需要注意以下几点:

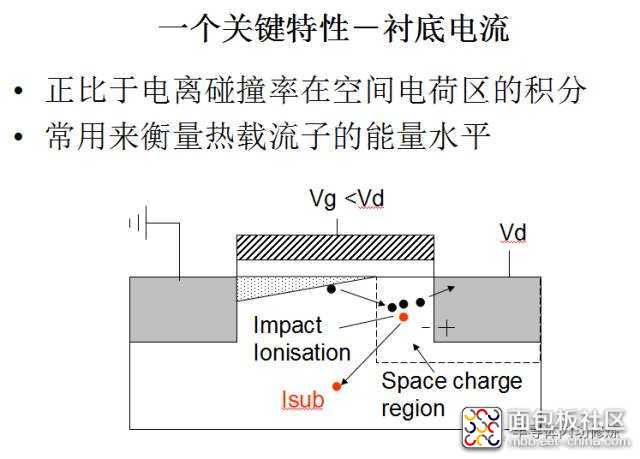

衬底电流:

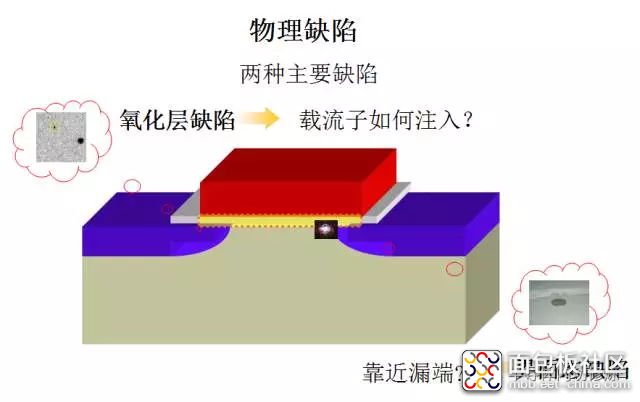

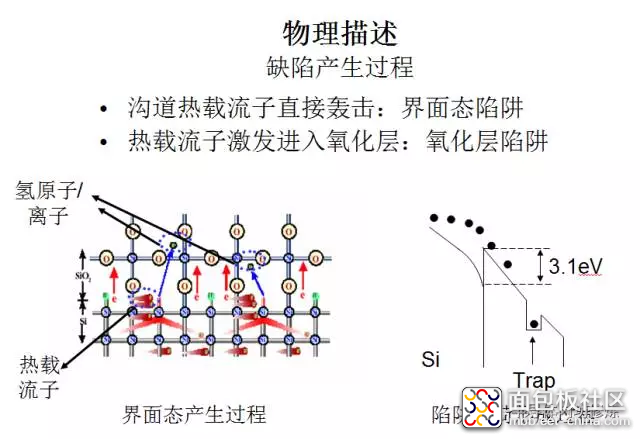

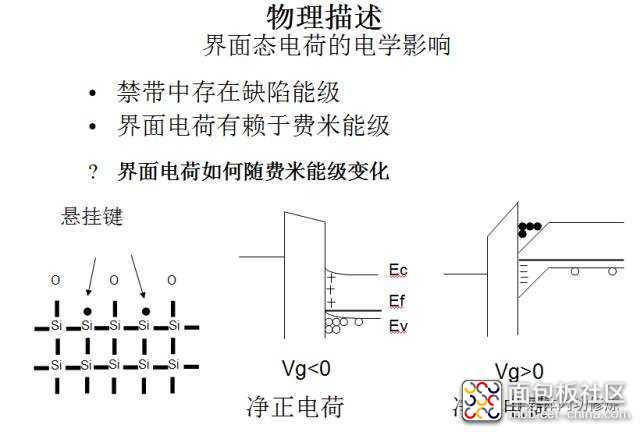

热载流子会产生的2种物理缺陷:氧化层缺陷和界面态缺陷

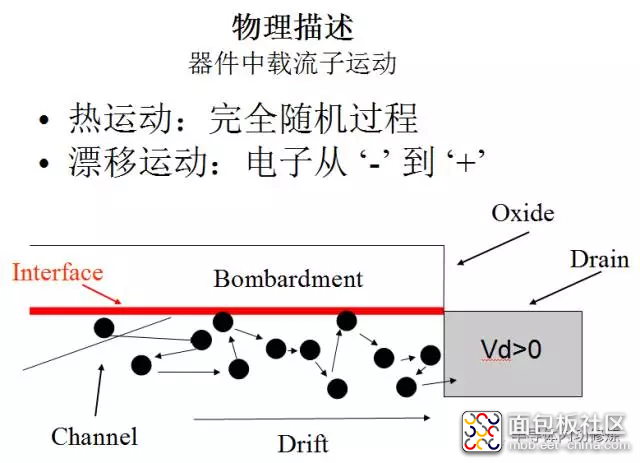

热载流子的物理描述:

界面态陷阱和氧化层陷阱的产生:

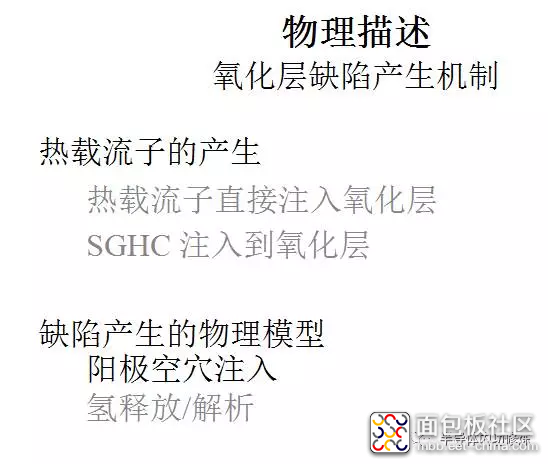

氧化层缺陷产生的机理:

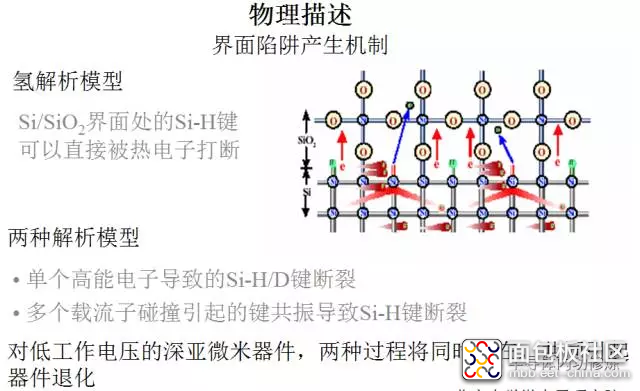

前面介绍过的氢解析模型和两种模型共同作用

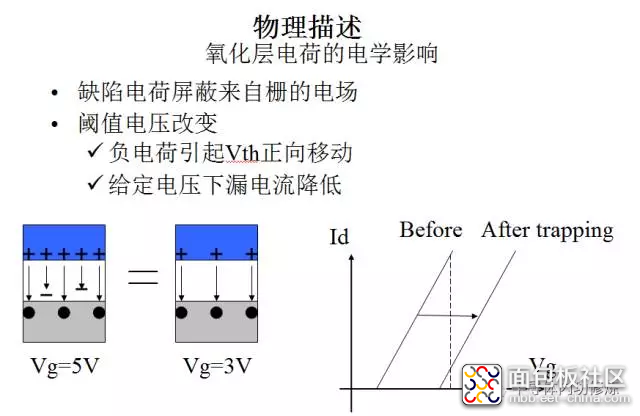

氧化层电荷的电学影响:氧化层电荷增加,自然引起VT变化,这也是热载流子效应比较明显的结果;如果VT变高,自然导致漏电降低。

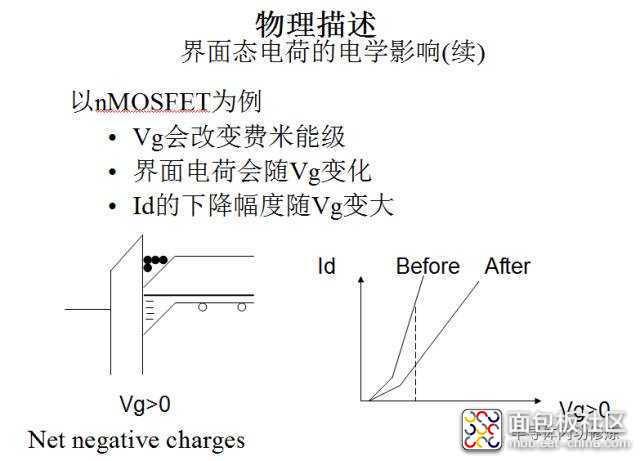

下面介绍NMOS特性退化:

NMOS特性退化的3种模式:

对于带有LDD的NMOS结构,还有spacer氧化层区域的退化问题

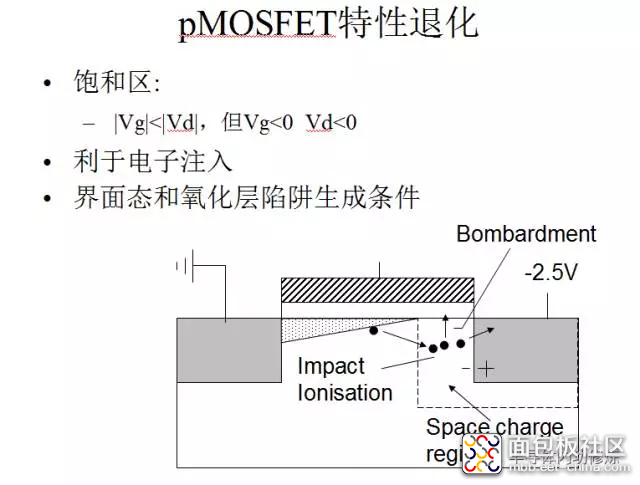

PMOS特性退化类似于NMOS,但相对NMOS要轻微一些

同样的3种退化条件:

下面这张图说明Vg取一半Vd的原因:此时衬底电流最大

Vg在一般Vd前后两种条件下,热载流子效应的差异

内容转载自半导体内功修炼,仅供学习交流使用,如有侵权,请联系删除。

/5

/5