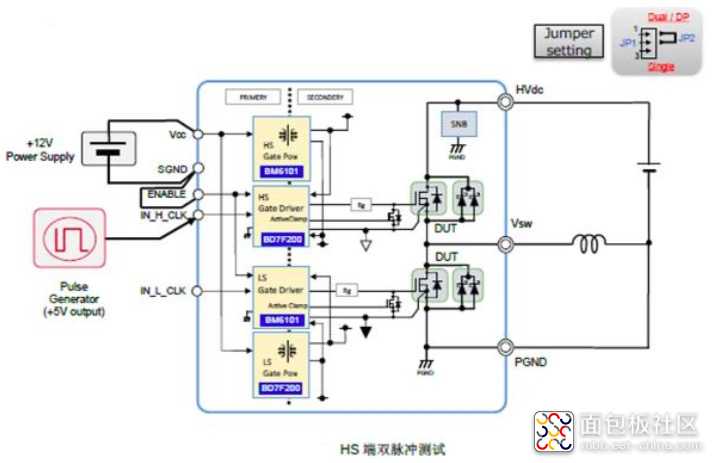

板子到手后焊上 SCT3040KR 的样子如图 1 所示。

图1

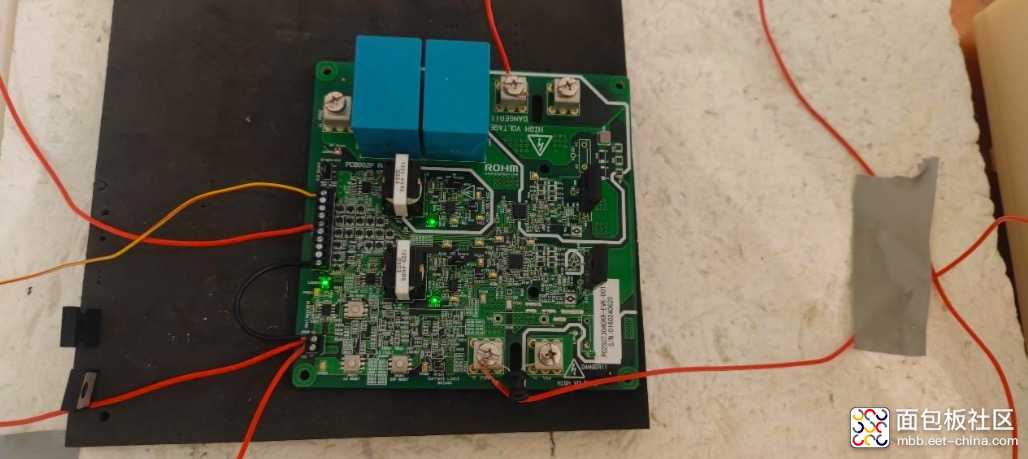

针对 HS 端 MOSFET 的双脉冲测试,从 EMC 方面考虑,对以下两个方向进行了测试:辐

射发射以及 HV-LV S 参数。

图2

一、辐射发射

测试前准备:2 个 12V 电源,1 个脉冲激励,若干导线,330μH 电感,接收机,装有吸

波材料的屏蔽室。(为了安全考虑,HVdc 测电源用 12V 电源代替)

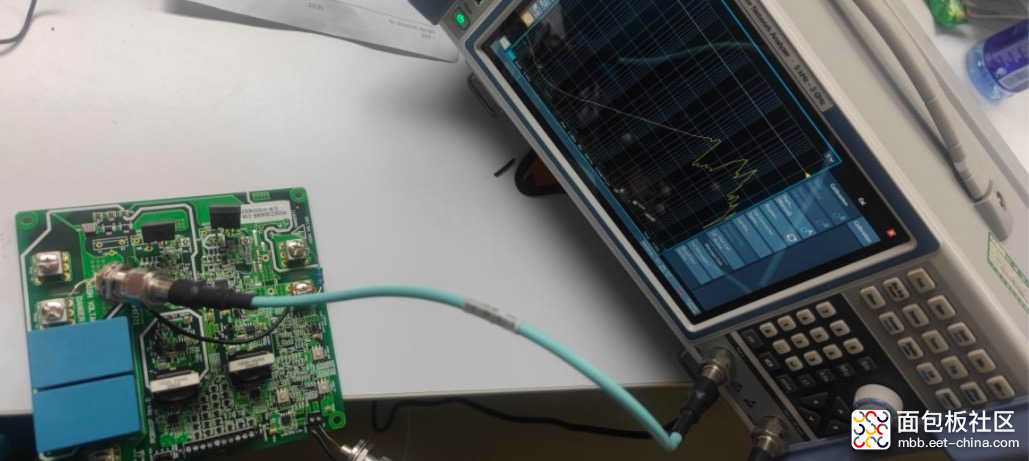

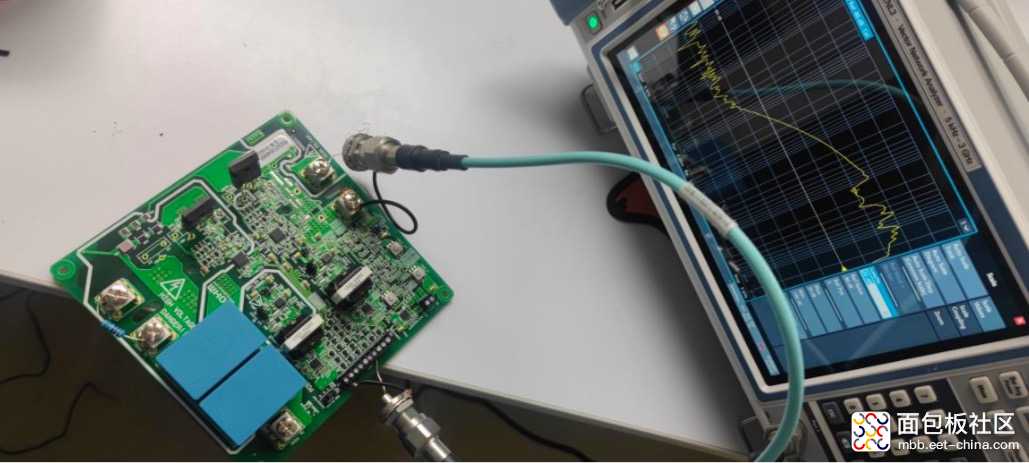

测试搭建:

图3

图4

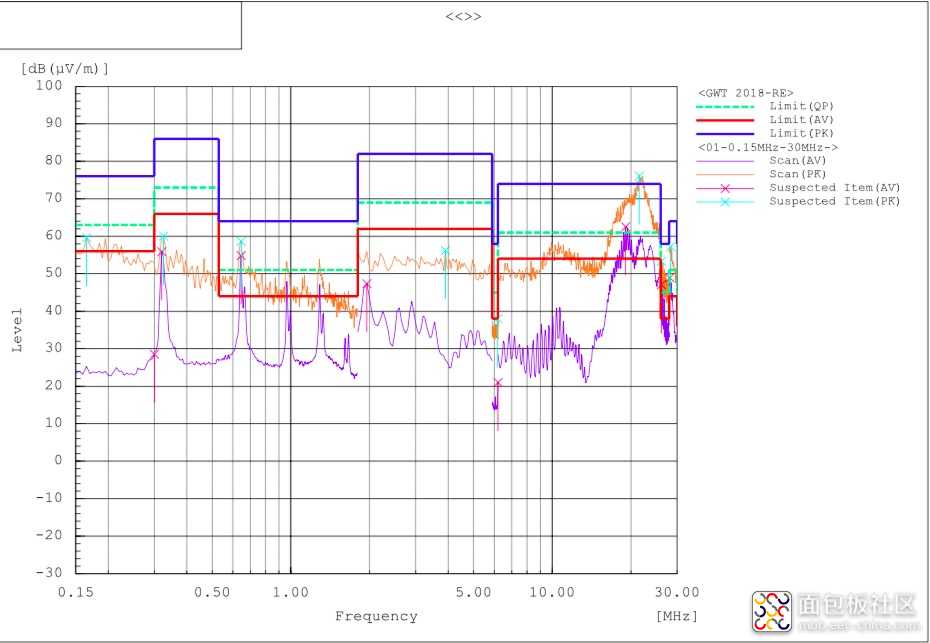

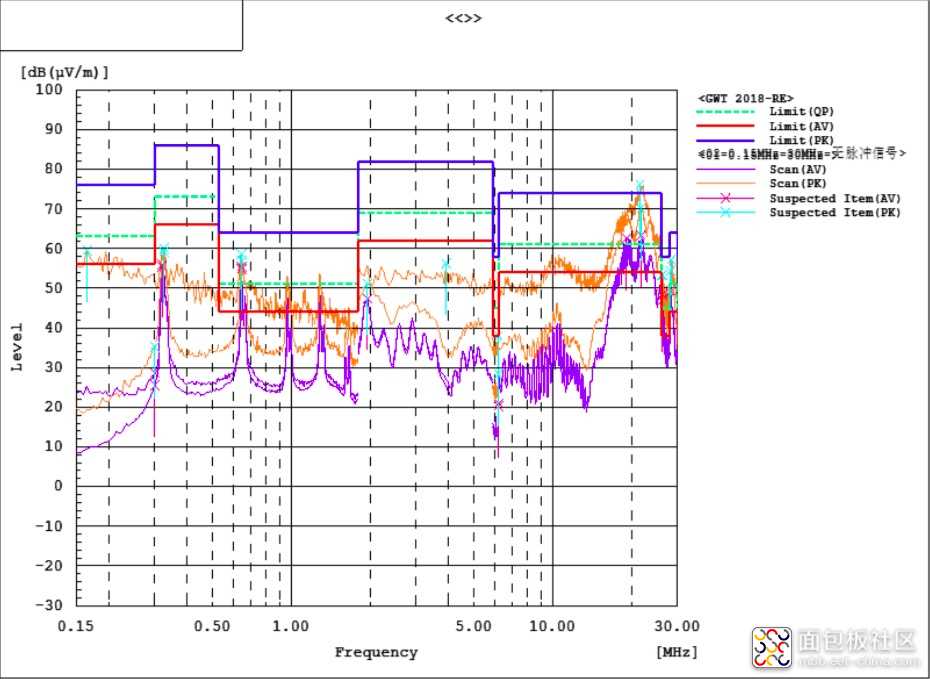

12V 电源和 5V 脉冲激励同时工作时,板子的辐射发射量如下图(图上方的三条折线是车级

的辐射发射限值,分别是峰值,准峰值,平均值)。

图5

由图 5 可知,此评估板的辐射发射整体情况较好,但在 20MHz 附件辐射发射量较大。

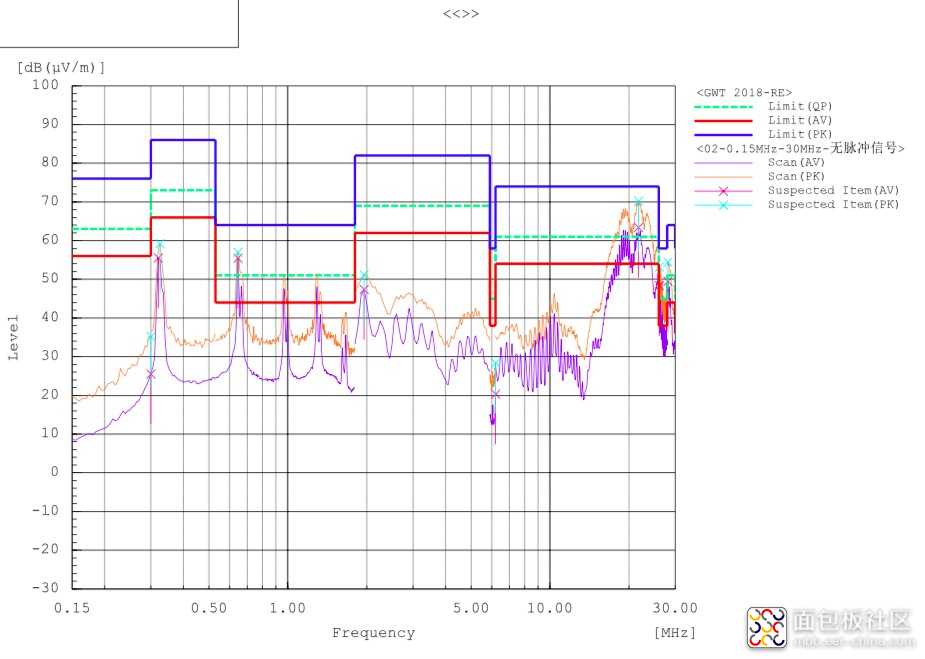

接下来,关闭 5V 脉冲激励,观察仅上电情况下板子的辐射发射情况,结果如图 6

图6

将图 5、图 6 放在一起比较,如图 7:

图7

可以发现两条曲线基本重合。说明 5V 脉冲激励并没有驱动板子或者驱动电路的辐射发

射量太小。若是 5V 激励没有驱动板子,可能原因是脉冲激励的工作频率设置的太小,使负 载电感饱和,相当于负载端短路。不管是 5V 脉冲激励并没有驱动板子,还是驱动电路的辐 射发射量太小,此时所接收到的主要干扰是来自隔离变压器的,由图中的谐振点可知,隔离 变压器的工作频率是 300kHz 左右。由于实验室时间紧张,在发现问题后,无法调整实验再 次测试。

二、HV-LV S 参数

此评估板既有高压侧也有低压侧,而良好的高低压耦合衰减能力是保证 EMC 安全的一 个重要前提。

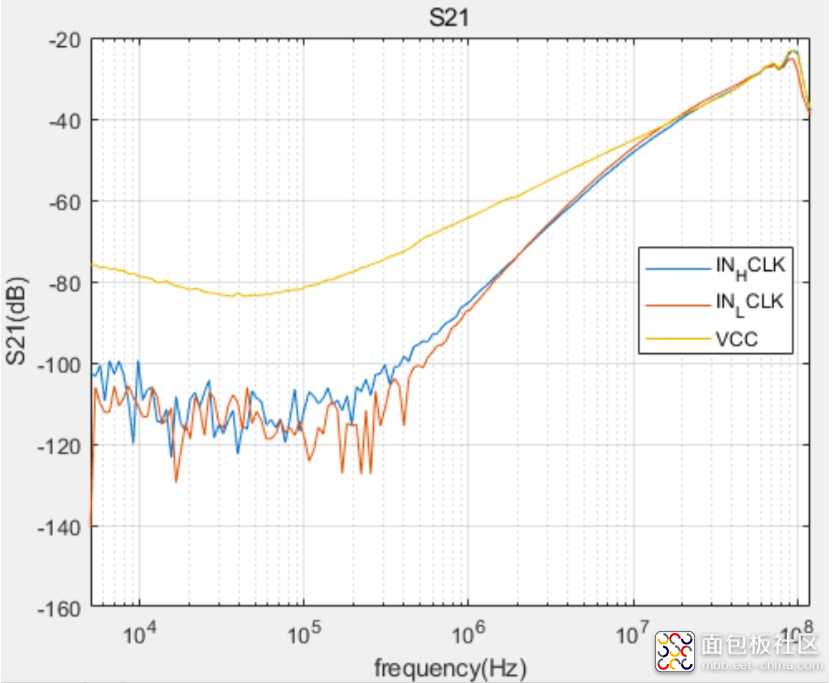

图8 HVdc侧至VCC侧的S参数

图 9 HVdc 侧至 IN_L_CLK 侧的 S 参数

图 10 HVdc 侧至 IN_H_CLK 侧的 S 参数

图 11

图 11 为使用 matlab 处理后的曲线图,将上面测试的三个耦合衰减曲线放在一起对比,可以 发现,HVdc 侧至 VCC 侧是高低压耦合衰减做的最差,而 HVdc 侧至 IN_L_CLK 侧、IN_H_CLK

侧的耦合衰减曲线基本一致。

/5

/5