这几天研究的产品的核心算法是发射和接收的正弦信号的相位差检测。

在STM32F407处理器上,通过DMA+SPI通信对接收和发射信号进行高速采样。

设计算法计算接收和发射信号的相位差。

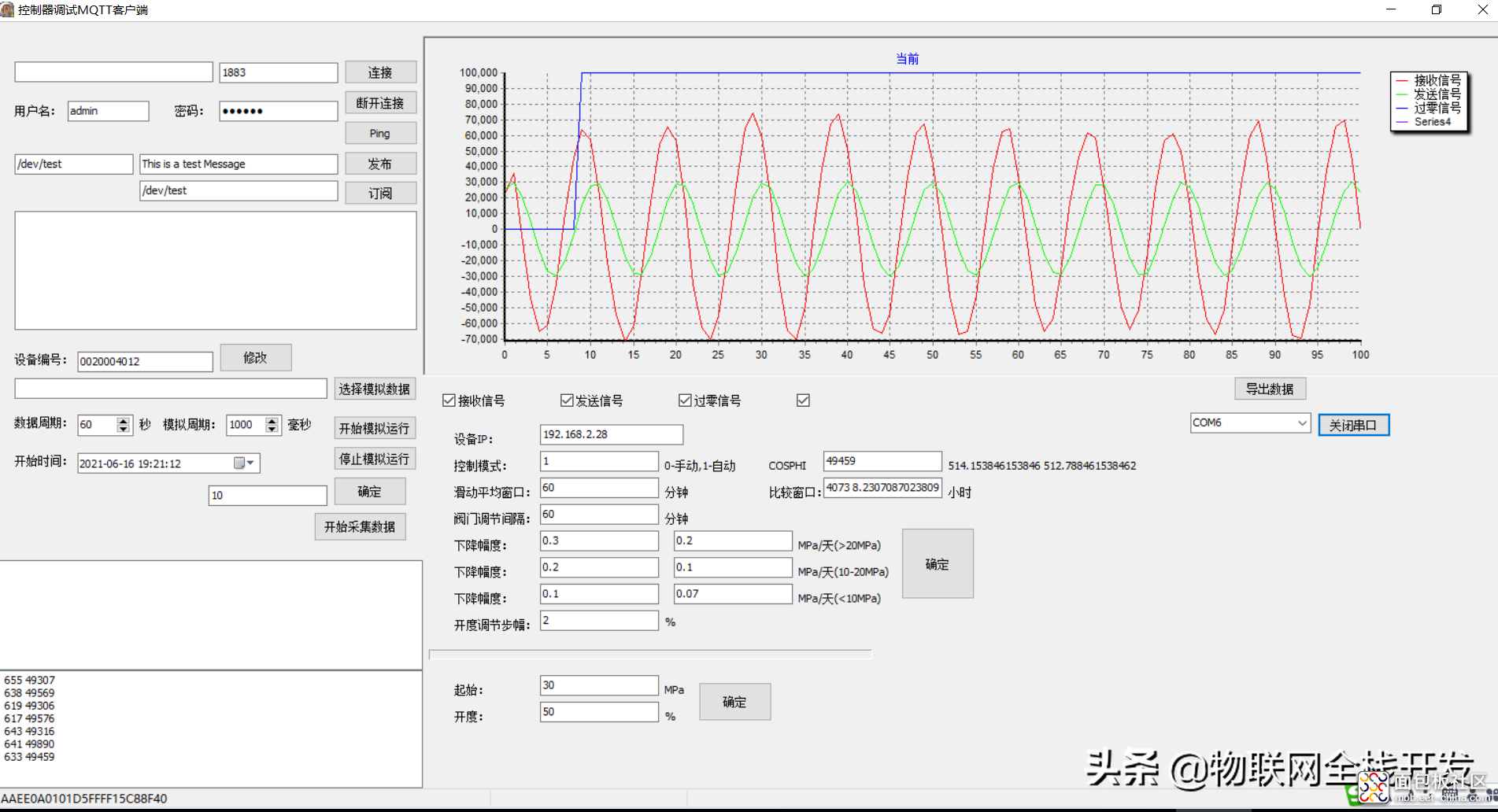

用delphi改了一个简单的调试用的上位机软件。

下位机通过串口将采集到的A/D值以及计算结果发送给上位机。

上位机将数据以图形界面显示出来,同时对计算结果进行统计分析,判断算法的正确性,

并根据分析结果调整参数。

花了两个晚上的时间,完成了上位机和下位机的算法设计、代码编写和调试。

用于产品调试的上位机软件界面

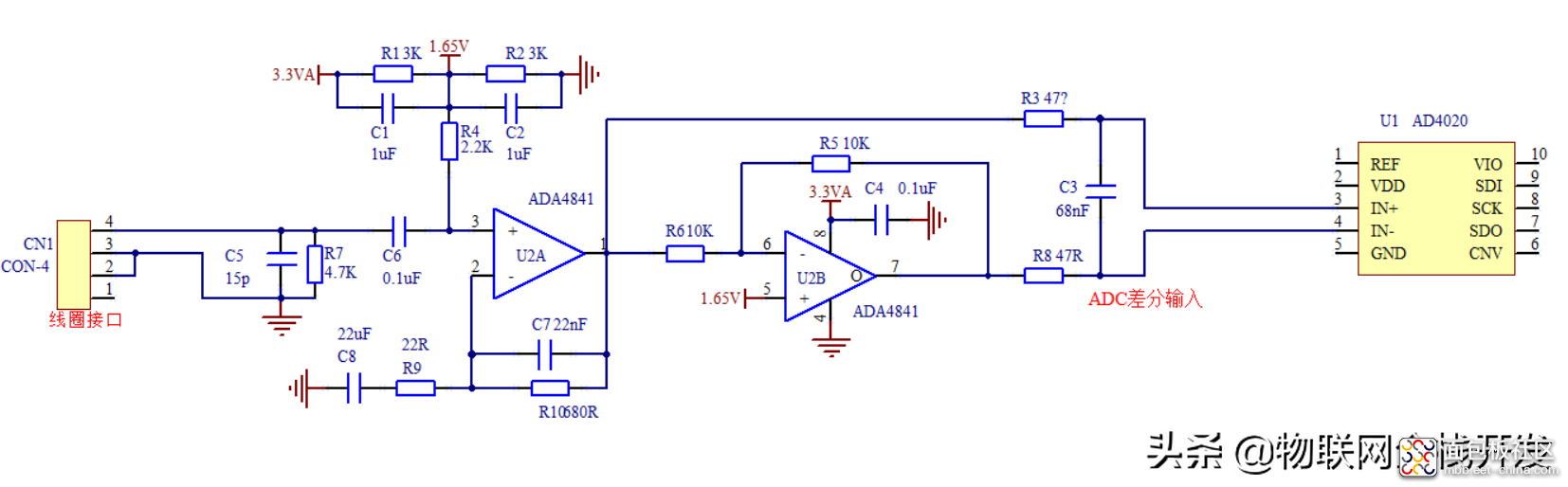

电路分析

今天晚上开始分析测试结果。

第一步是和硬件电路的理论分析进行比较。

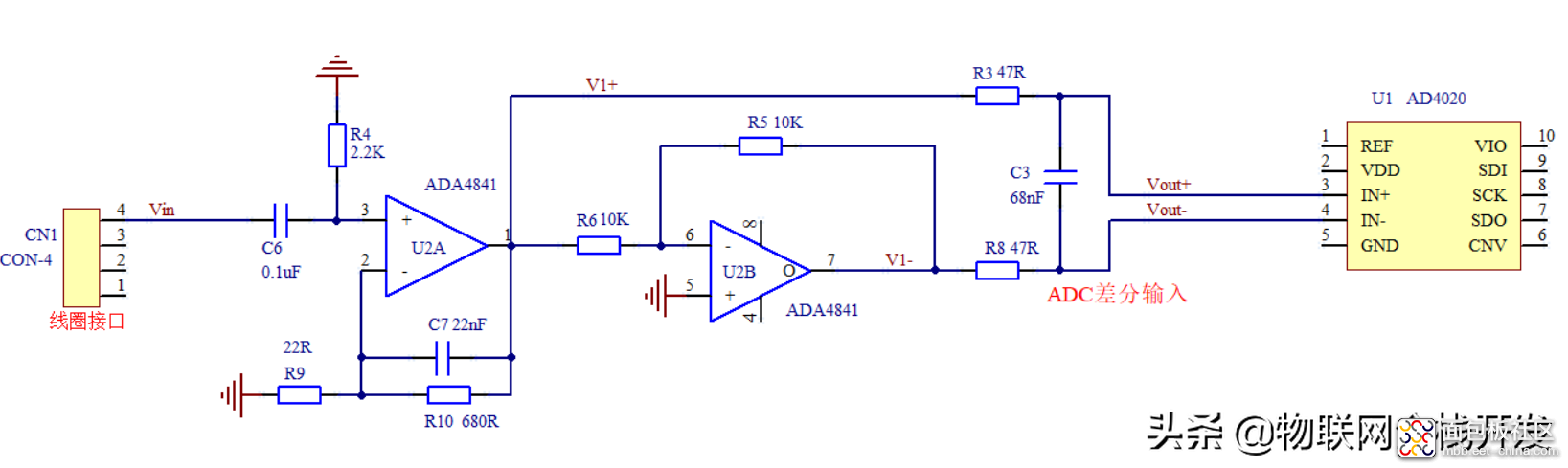

客户设计的电路

输入信号的频率为4kHz-18kHz。

在该电路中,

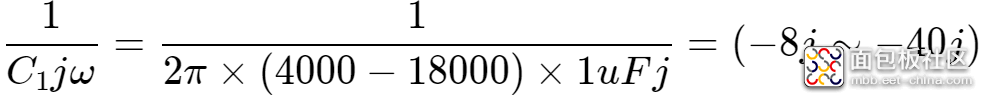

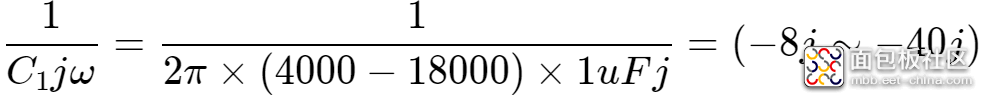

C1、C2的阻抗为:

跟与其串联的电阻R4相比,可以忽略不计。

同理,电容C8的阻抗为

,跟R9相比,也可以忽略不计。

+3.3V通过R1、R3的分压得到1.65V给轨对轨运放ADA4841提供直流工作电平,使其可以通过单电源供电。

综合考虑之后,可以得到该电路的交流通路,如下图:

电路交流通路

相位分析

电阻R4,电容C6构成高通滤波器,

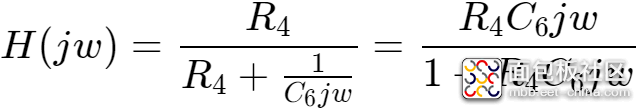

传递函数为:

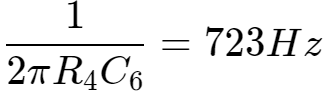

幅值函数为:

-3dB截止截止频率为

幅频特性曲线

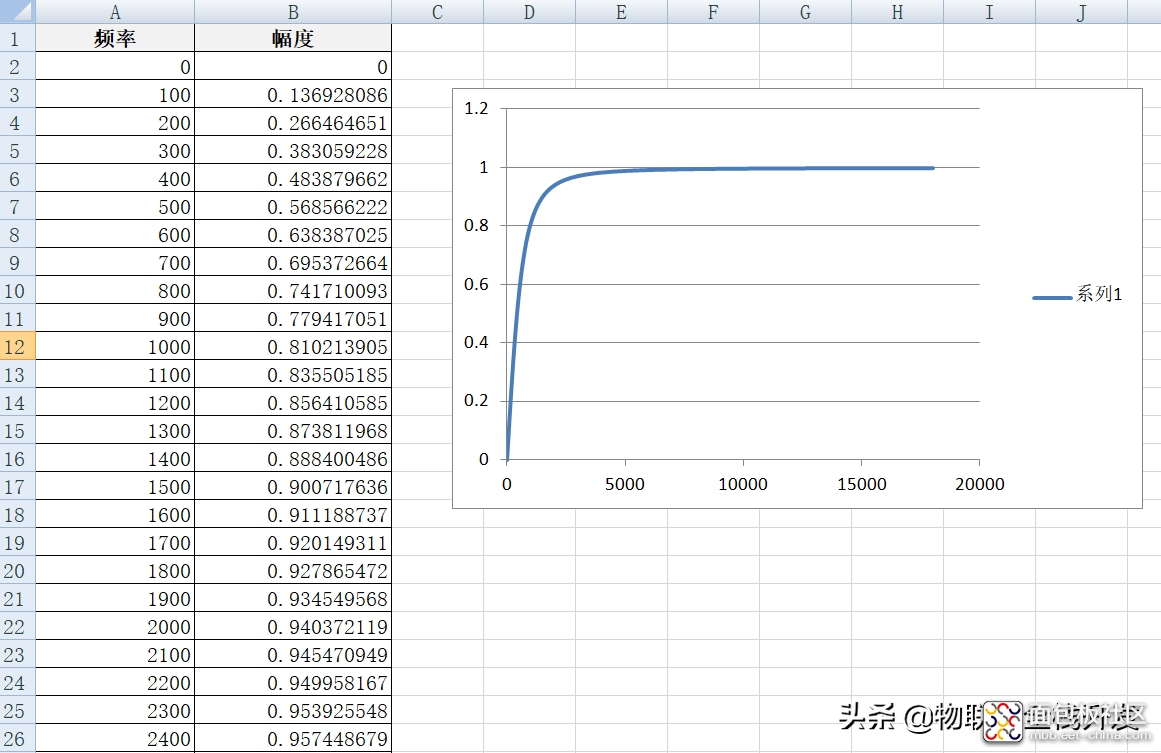

相角函数为:

相频特性

当频率为18KHz时,运放同相输入端的电压相对于输入电压的相位超前

,

幅度比值为1。

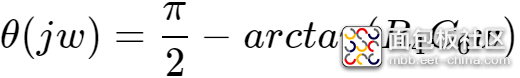

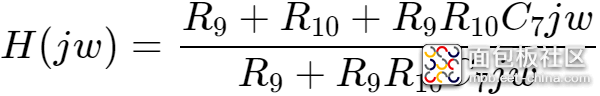

R9、R10、C7构成低通滤波器,从运放同相端到输出端的传递函数为:

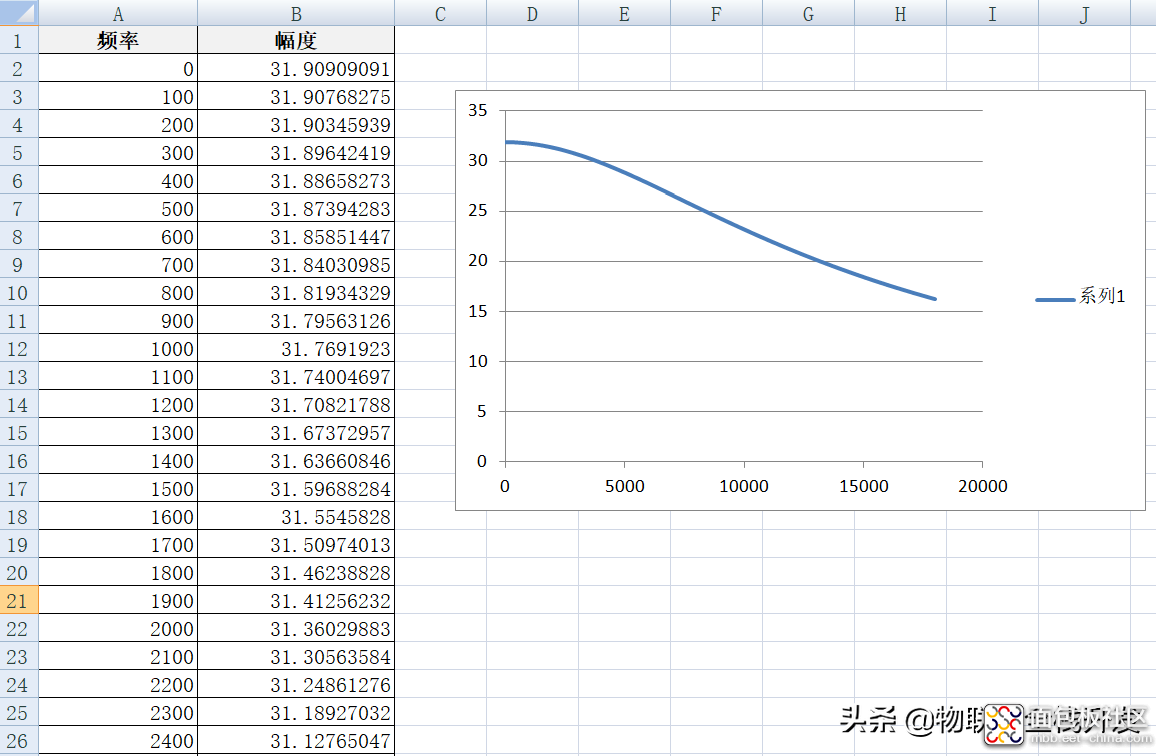

幅频特性曲线

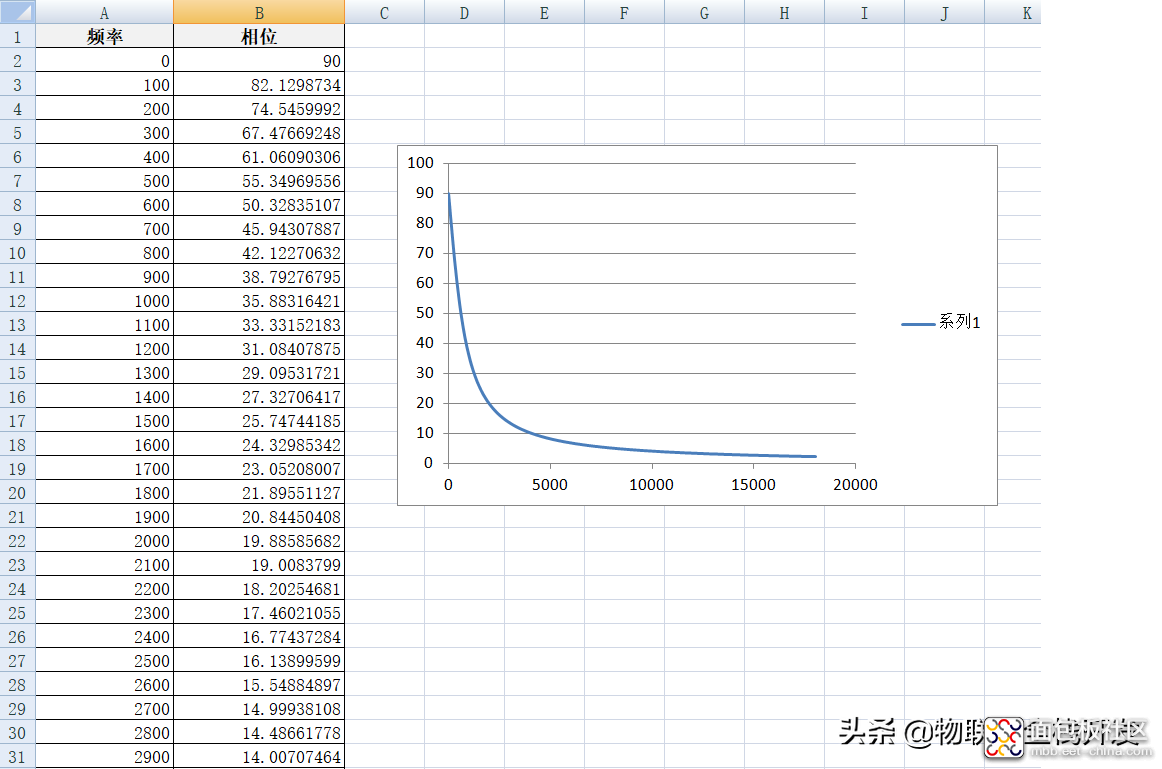

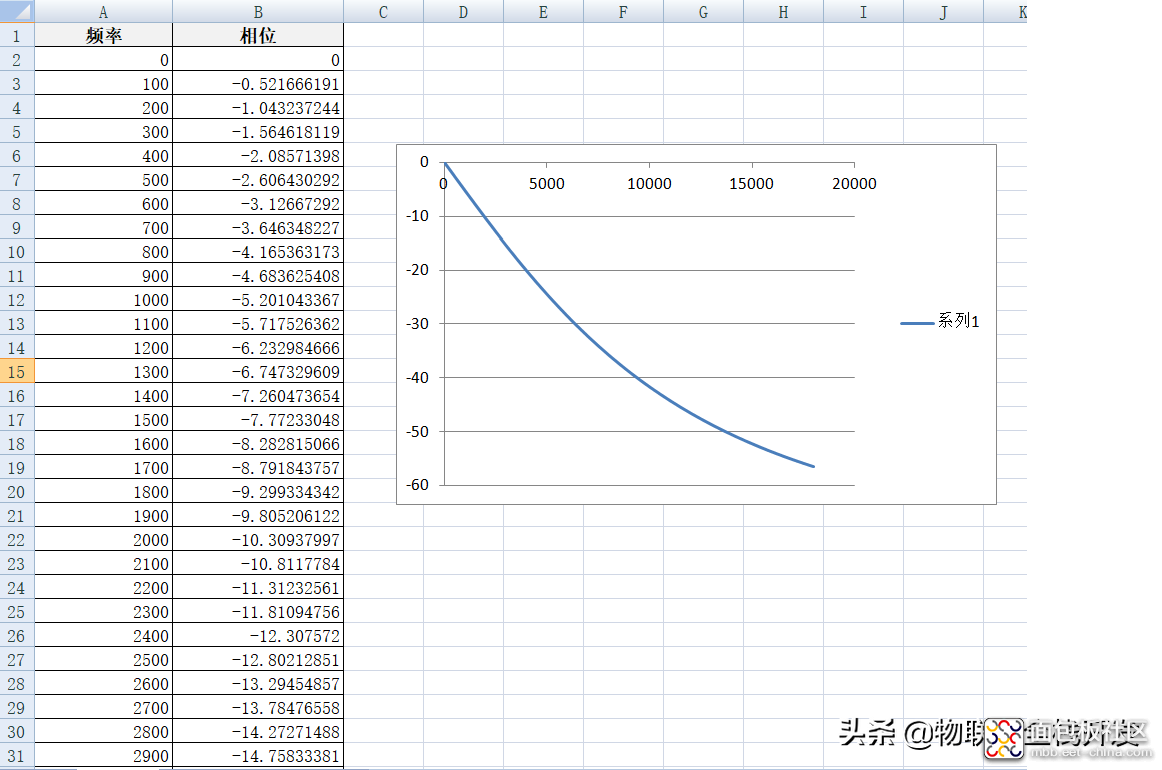

相频特性曲线

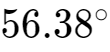

当频率为18KHz时,运放输出端的电压相对于同相输入端电压的相位滞后

,幅度比值为16.25。

因此,当频率为18KHz时,运放输出端与输入信号的相位滞后

。

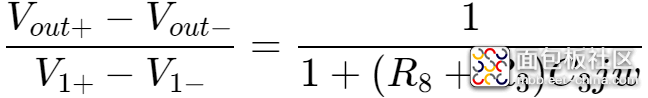

AD4020差分输入信号Vout+-Vout-与运放输出的差分信号V1+-V1-在频率域满足以下关系式:

当频率为18KHz时,AD4020输入信号与运放输出信号相比相位滞后

,幅度比值为0.81。

综上,处理电路导致相位滞后为

。

Multisum仿真

Multisum仿真与计算结果一致。

来源:物联网全栈开发

/5

/5