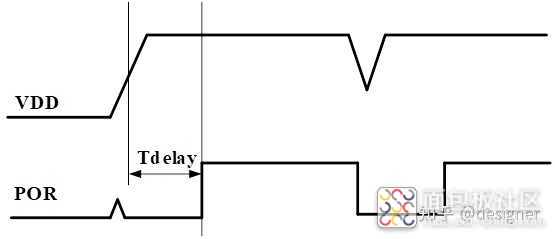

POR电路功能:电源VDD上电初期产生一个复位信号(RESET信号),初始化整个系统芯片,当VDD足够高时,POR跟随电源电压输出,使各模块正常工作,当VDD下降至足够低时,POR输出低即RESET信号,复位整个芯片电路,设计时特别要注意回滞区间和deglitch时间

POR电路的工作波形:

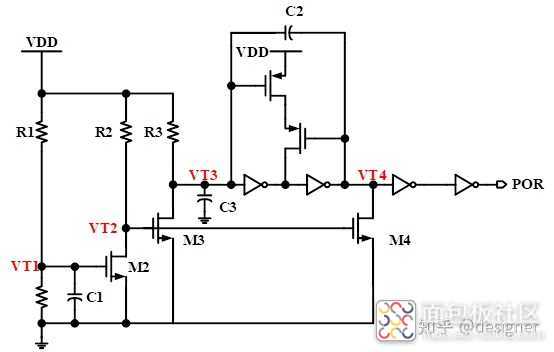

一种POR电路如下

工作原理:

上电阶段,电源VDD开始从0V上升当处于较低电压时,M2的栅极电压VT1较低而处于截止状态,M3的栅极电压VT2随VDD上升,使得M3导通,将VT3拉低,POR输出低电平(RESET信号),VDD持续上升,VT1增大使得M2导通,VT2拉低,M3截止,VT3被拉高至VDD,此时,POR输出高电平(跟随VDD电压),复位信号释放,使芯片系统模块正常工作,至此,POR完成了VDD上电过程中,完成对芯片系统初始状态RESET,在电源正常后输出高电位

设计要点1:

Deglitch时间设计,当电源VDD有尖峰脉冲信号的干扰时,通过设计R3和C3的时间常数T=R3*C3,该事件常数就叫deglitch时间,也叫延迟时间,T越大,表示可抗电源干扰的频率越高,比如:设计f=1/T=1/(R3*C3)=100kHz,如果电源上有一个100kHz以上频率的脉冲干扰,均不会影响VT3节点电压

设计要点2:

回滞区间设计,当VDD高于阈值V_UP时,POR输出高,VDD低于V_DN时,POR输出低,V_UP-V_DN即为回滞区间,一般设计在200mV左右,可以提高POR对VDD的抗干扰能力

/5

/5