基于gm/Id,开发的Analog design Toolbox,利用其设计放大器

https://zhuanlan.zhihu.com/p/563628956

Analog Design Toolbox使用实例

仅供学习交流参考,不做商业使用

才疏学浅,抛砖引玉

前言:

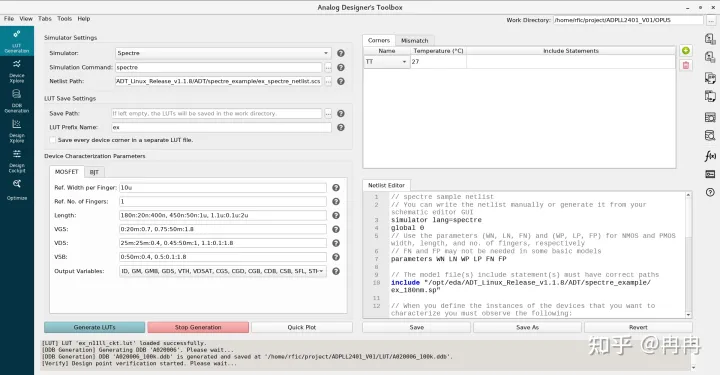

Analog Design Toolbox(下文简称ADT),是一款国外公司基于gm/Id思想,开发的一套模拟设计辅助软件。其主要的使用场景为:各类运算放大器、BG、电流镜、LDO的参数选取。

图1. Analog Designer Toolbox界面(来自官网ADT demo视频截图)

以放大器设计为例,传统方法假设MOS工作在饱和区,符合平方率关系,通过手算获得MOS管的初始尺寸,然后仿真,随着工艺节点进步,平方律假设偏差越来越大,更多二级效应,导致达到预期指标的迭代次数较多,降低了设计效率。能否有一种新的方法论和工具可以考虑这些二级效应,使得设计者的MOS管参数选择都有据可循,减小迭代次数?我们先从宏观的角度来进行分析:

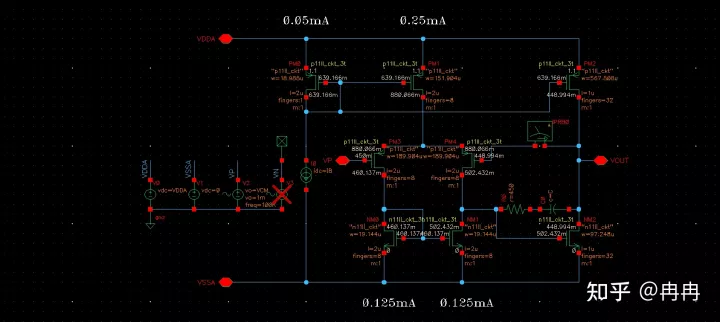

当我们拿到一个确定的工艺后,选定了一种放大器的结构,如图1。如果知道了NMOS和PMOS的每两个端口之间的I-V特性曲线,选定的结构中MOS管之间的连接拓扑关系是确定的。则该结构的放大器在给定的工艺下的性能边界就已经确定了(只是我们设计者“不知道”)。将上述的MOS管的I-V曲线进行利用ADT仿真得到并制作成LUT。我们就可以“知道”选定结果的放大器的性能边界了。使用ADT,我们将回答3个问题:

(1)给定的放大器指标,能不能做?

(2)放大器如果能做,指标能做到多好?

(3)对已经设计完成的放大器,其性能是否还有优化的空间?

注意:我们并没有对放大器结构做特殊假设前提,因此这是一个通用的方法。

ADT的官网是:ADT - Home (master-micro.com) https://adt.master-micro.com/

ADT demo视频教学:The Analog Designer's Toolbox (ADT) | Invited Talk by IEEE Santa Clara Valley Section CAS Society - YouTube https://www.youtube.com/watch?v=FT6kKC5OdE0&list=PLMSBalys69yyjfUj5LNzE2Hwt5aPtn2HW&index=6

官网提供免费版本,包含5种常见的放大器结构,供个人学习

图1. 给定工艺、给定结构的放大器指标边界是确定的

需要注意的是:

(1)电路设计还是需要通过先对结构进行分析,了解各个指标与哪些MOS管相关,可以参考allen的CMOS集成电路设计,做到设计者对电路心里有数。

(2)ADT只是一个辅助工具,可以帮助我们在运放的传统设计流程中获得一个精确的设计MOS管尺寸初值。从而减小迭代次数,加快设计效率。

- 软件版本

Analog Design Toolbox 1.18

- ADT软件的使用流程

图2. ADT的使用流程

图3. 利用Virtuoso生成的scs制作特定工艺下的LUT

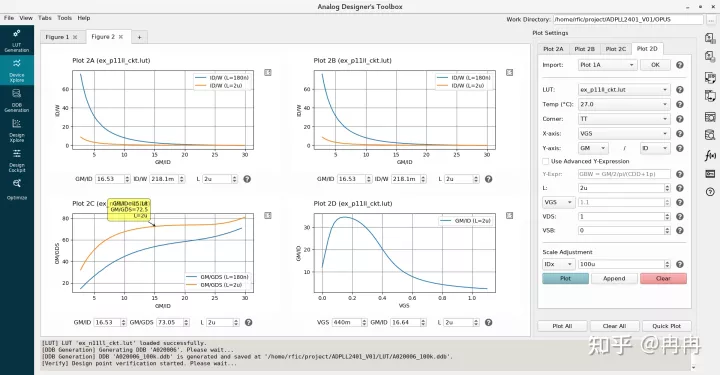

图4. 查看给定工艺下NMOS和PMOS的gm/Id,Id/W等曲线

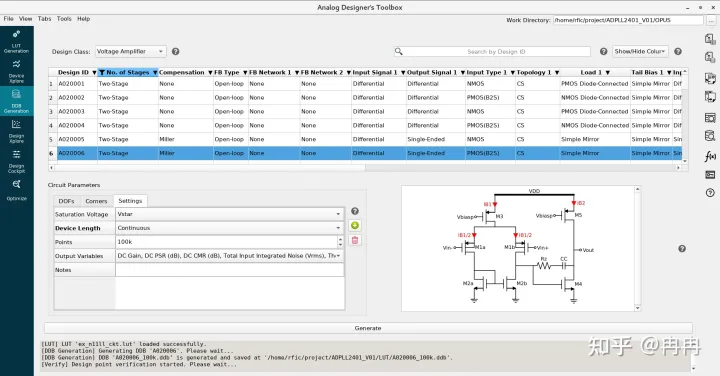

图5. 在DDB中选择特定结构的放大器,设置好Corner,点击Generate生成数据

注意:在选择运放的结构时,需要知道各种结构的优缺点,例如:是追求DC Gain,还是追求大Swing,还是追求GBW等等。这些可以在图5所示的DDB中选取不同结构运放,点击Generate之后很方便的对比,实现快速筛选所需要的结构。

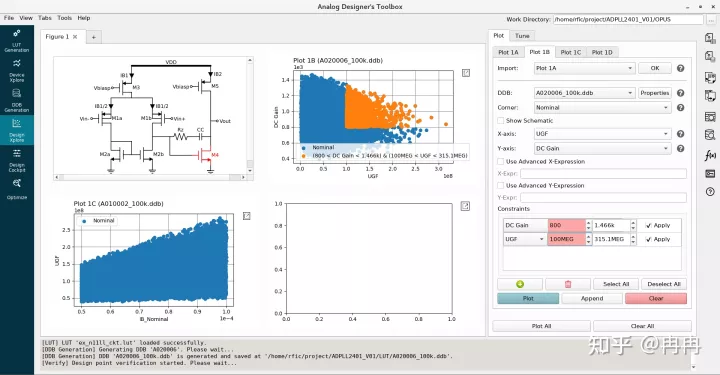

图6. 在Design Xplore中设置所需要的指标约束,获得可选尺寸范围

(蓝色为所有可能的组合,橙色为满足设计约束的组合)

注意:这里可以很直观的看到给定工艺,给定结构的运放的性能边界在哪里~

图7. 根据ADT得到的初始尺寸,带入virtuoso进行仿真验证

注意:在对比ADT和spectre仿真之前,先跑一次DC analysis,确保每条支路的电路都是正常的。

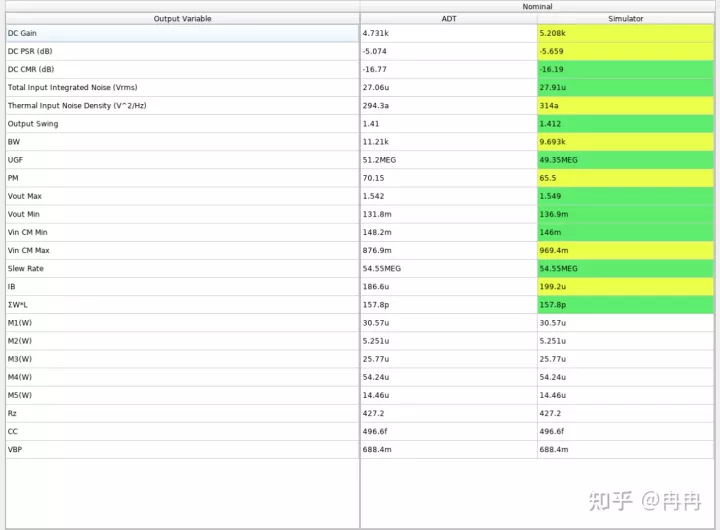

图8. ADT仿真结果

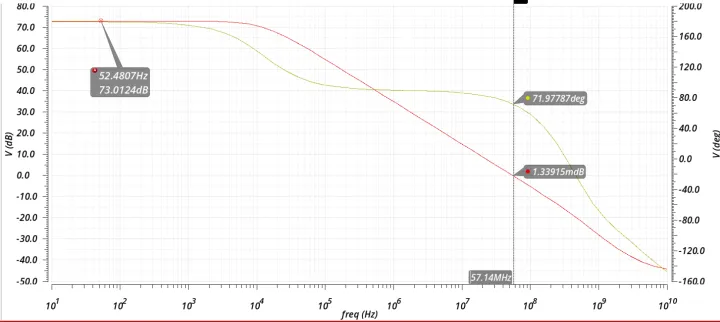

图9. Spectre仿真验证结果

可以看到ADT的结果还是挺准的,目前为止,只进行了1次参数迭代,就实现了所期望的运放指标。目前验证的几种二级米勒补偿OTA,结果都挺准的,误差在5%以内,增益误差<3dB.

当然,如果对于DDB中没有的结构,可以用Device Xploer中生成的Gm/Id查找表,来进行设计。毕竟ADT只是一个辅助工具,也不能全指望它。欢迎大家尝试之后,给予反馈。

其他注意的事项:

- 先打开Device Xploer查看NMOS和PMOS的阈值随L变化曲线,找到最坏corner

- 在DDB Generation,打开corner,根据传统流程中Vov=100-200mV,设置合适的VCM

- 在Design Xplore,所有的L向100nm取整,不用担心带来的30nm的精度丢失,因为你在根据约束选点的时候,就应该要考虑到这些(PVT,MC引起的制造偏差),留合理的裕度即可。

后记:

如何正确利用好ADT(gm/id)来辅助运放设计。大概想法是:设计运放肯定是要先分析清楚指标与哪些参数有关,计算出初值的时候,用gm/id(或者ADT)来辅助进行。如果完全不思考,完全依赖ADT,那就丧失了“design”的精髓,完全不知道GBW,Gain等等和MOS管尺寸之间的相互影响的定性趋势。但是如果还是按照传统平方律假设去计算,则与实际的短沟器件特性偏移越来越大,迭代次数指数上升,在一个设计周期中,大量时间花在调管子,最终把设计者变成了调参的工具人。方法论和工具都是为设计者服务的,能否在具有分析能力的基础上,正确高效的使用工具来加速设计,比起“经验”这种抽象的说法,使用EDA工具获得一个直观的指标之间相互制约trade-off的图表(系统指标可视化),对于新手来说,更容易有深刻理解。

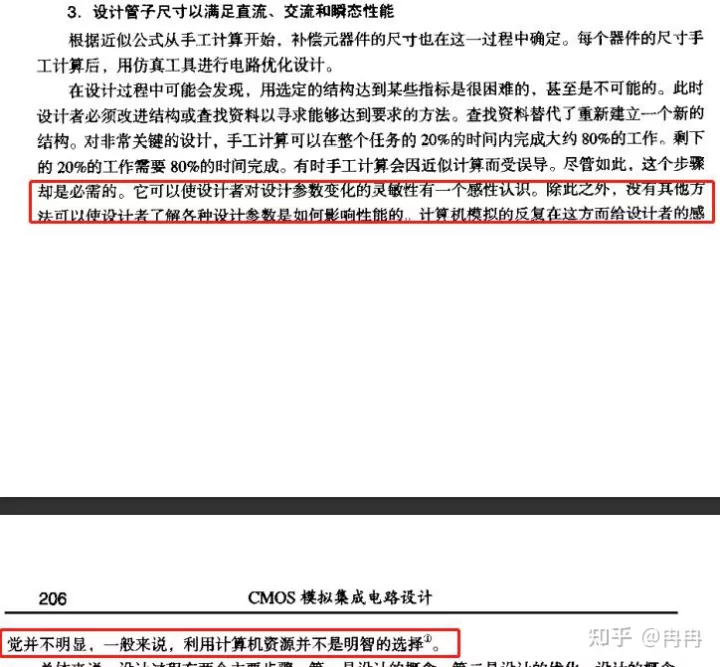

当然,电路分析的能力,是最重要的。EDA,工具,仿真都是验证自己分析的手段。ADT在实际使用的时候,感觉更像是一个模拟电路的验证工具。当然也看是什么人再用,对于初学者,在学习阶段,可以用ADT的可视化功能,来快速建立模拟电路设计的trade-off的感觉。对于老手,可能会用ADT来作为验证自己设计的电路性能的一个简便手段。ADT也好,gm/id也好,都是为设计者更快更好的设计模拟电路提供了另一条手段/途径,让设计者对电路结构有更好的理解。Allen老师在CMOS集成电路设计一书中,提到:

图10. Allen CMOS模拟集成电路设计

随着EDA的进步,Allen老师所担心的,都可以回答了。ADT可以回答三大问题:

(1)给定工艺下,给出指标的运算放大器,能不能做?

(2)如何选择合适的架构,怎么样做?

(3)已设计好的运放,是否能做到多好?

当然了,不管EDA工具如何强大,要牢记,是“设计者“在设计电路,而不是”EDA“在设计电路。ADT应该为设计者所用,而不是将设计者变成ADT的工具人。在电路原理的分析前提下,利用好ADT(gm/Id),完成参数变化的灵敏性的可视化(如图6),有助于初学者直观理解模拟设计中各个指标之间的trade-off关系,也可以作为,模拟设计工程师对已设计完的模拟电路的验证手段,可以将80%的仿真迭代时间缩短为1-2次,何乐何不为呢?

官网可以下载免费的试用版本,大家可以多尝试不同结构运放ADT辅助设计出来与spectre仿真的准确度

/5

/5