- 引言

- 一、奇偶校验器的Verilog代码实现

- 二、 奇偶校验器的 RTL 电路实现

引言

奇偶校验(Parity Check)是一种校验数据传输的正确性的方法,根据被传输的一组二进制代码的数位中 “1” 的个数是奇数或偶数来进行校验;采用奇数的称为奇校验,反之,称为偶校验;采用何种校验是事先规定好的,通常专门设置一个奇偶校验位,用它使这组代码中 “1” 的个数为奇数或偶数;例如奇校验,当接收端收到这组代码时,校验 “1” 的个数是否为奇数,从而确定传输代码的正确性。

一、奇偶校验器的 Verilog 代码实现

利用Verilog语言实现对一个 8 位数据进行奇偶检验,具体方法:如果是奇校验,只要将该 8 位数据第一位和第二位进行异或 XOR,然后将得到的结果和第三位异或,依次下去,直到和第七位异或,这样得到的最后结果,就是奇校验位;如果是偶校验,将上面的奇校验位取反即可。

Plaintext module Parity_Check( input wire [7:0] a, // 输入数据 output odd, // 奇数位 output even // 偶数位 ); assign odd = a[0] ^ a[1] ^ a[2] ^ a[3] ^ a[4] ^ a[5] ^ a[6] ^ a[7]; // assign odd = ^ a; assign even = ~odd; endmodule |

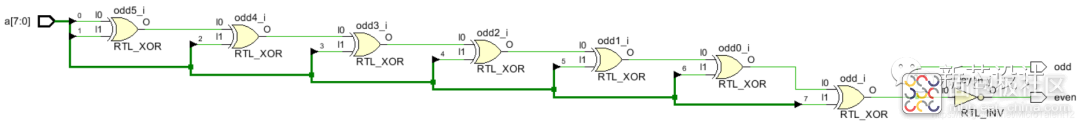

二、 奇偶校验器的 RTL 电路实现

奇偶校验器的 RTL 电路实现

/2

/2