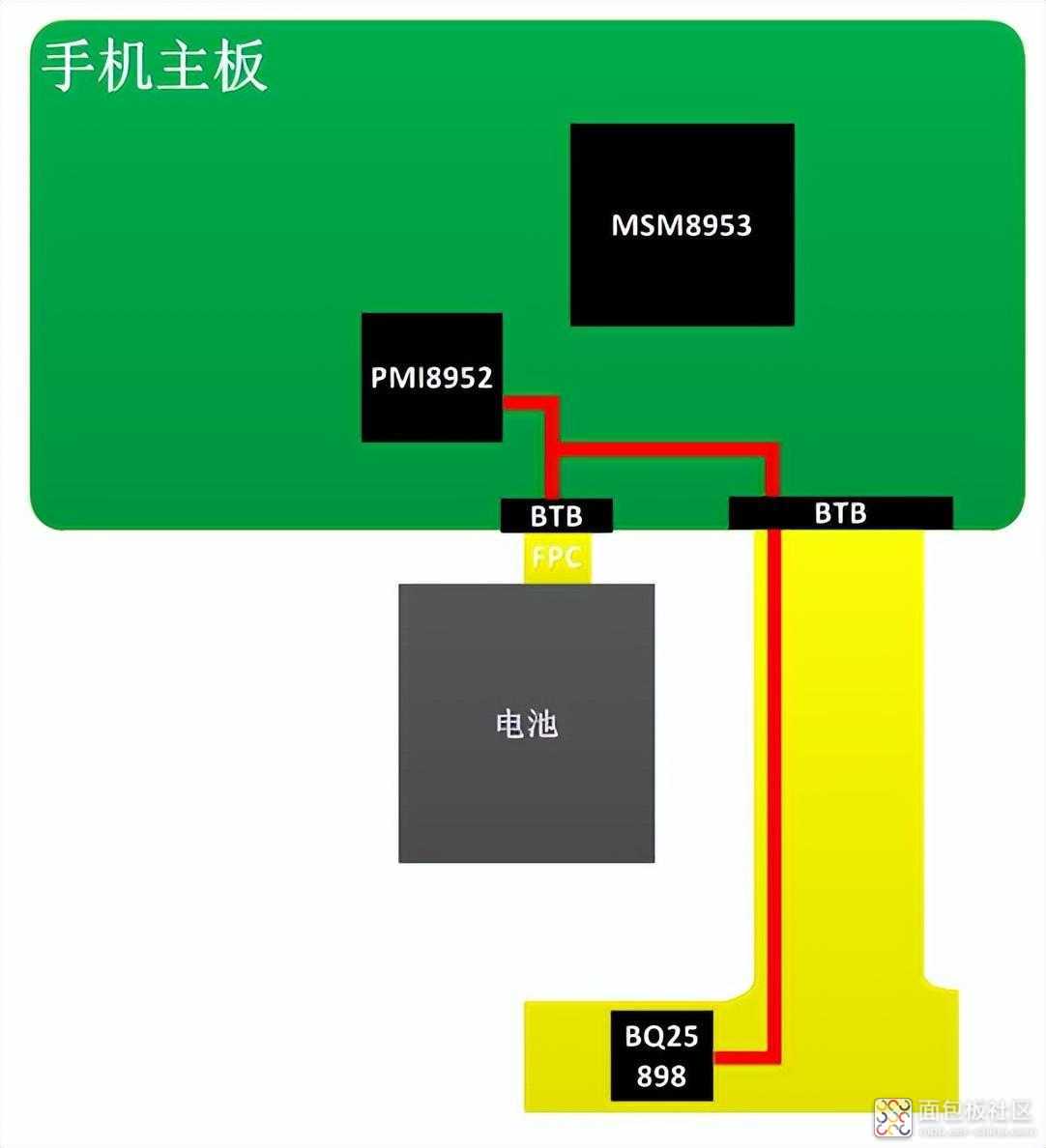

某手机的充电架构如下,主Charger用的是高通MSM8953平台套片的PMI8952,辅Charger用的是TI的BQ25898C。

两个Charger可以单独工作,也可以同时工作,分开放置的目的是更好的散热。

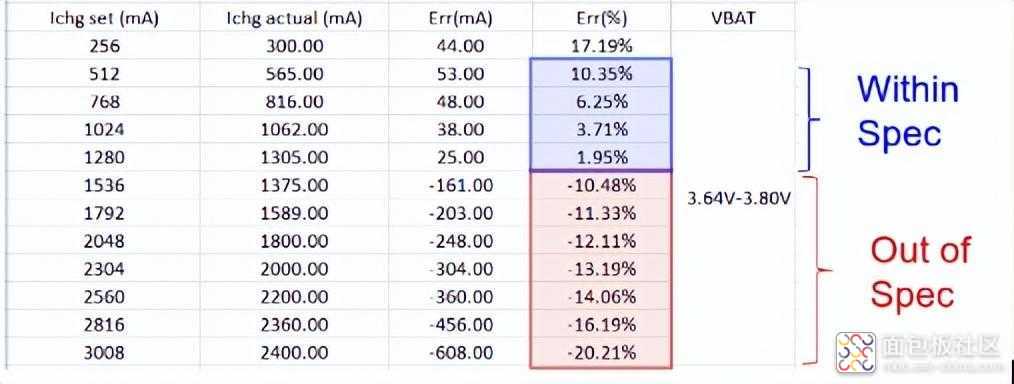

当BQ25898单独工作时,软件设置电流超过1.5A时,实测进入电池的电流总是比设置的值少。结果如下:

经交叉验证,此IC换到TI的EVB上,电流误差都在要求以内,IC本身没问题。

排查寄存器配置,软件反馈也没有问题。

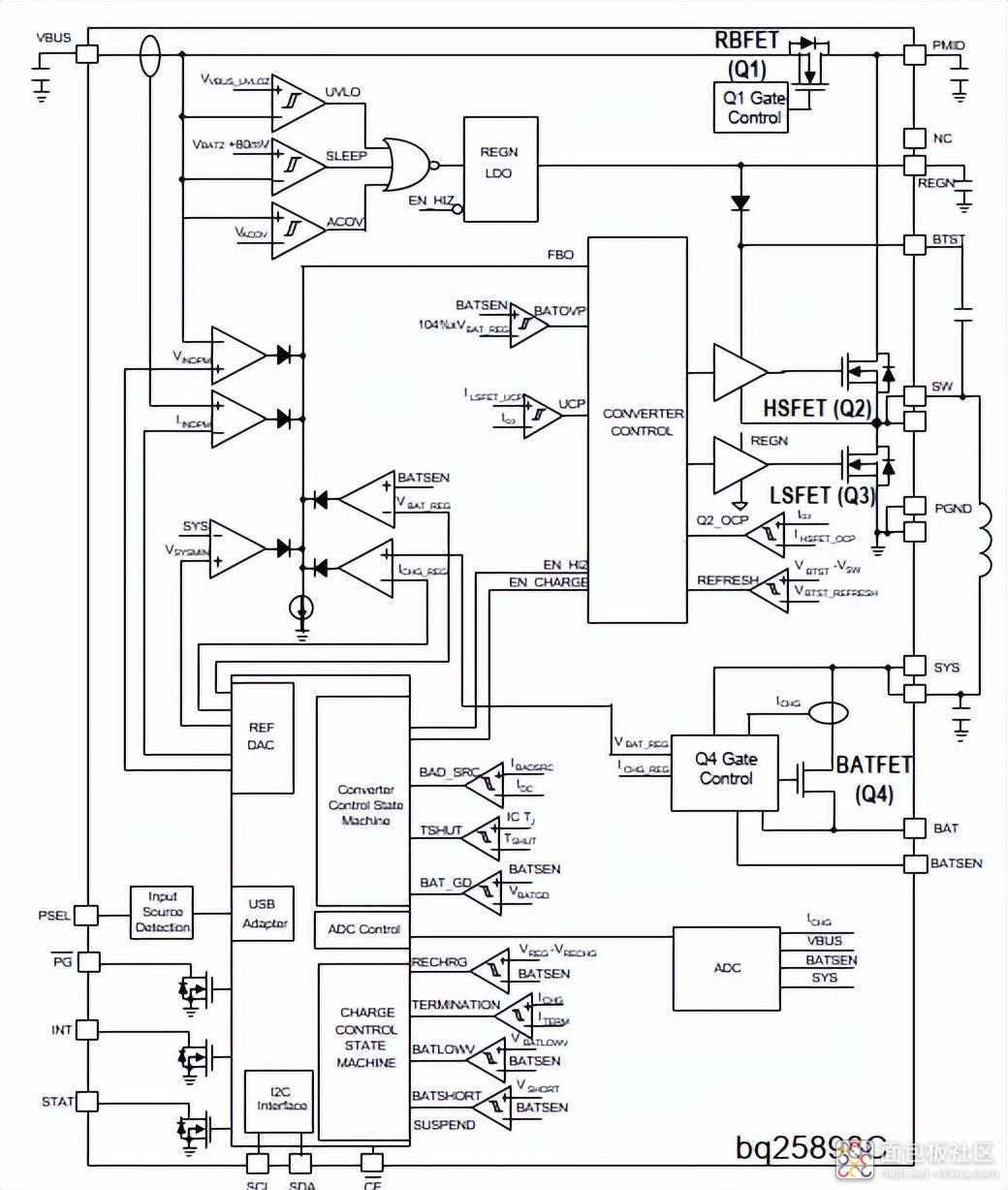

此后把注意力放在PCB Layout上。下面是BQ25898C的内部架构图,Q4的存在证明了这个充电IC是一个带电源路径管理的IC。

把Q4部分放大,能看到这个IC是通过检测经过Q4的电流来判断设置电流是否正确的,那么如何得知Q4的电流呢?

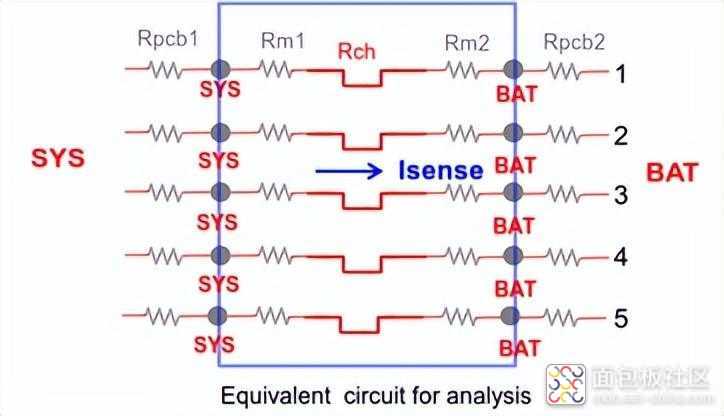

BQ25898C的Q4其实是由5个并联的MOS组成,每个MOS是一个充电通道,当设置充电电流为1.5A以下时,通道的阻抗为28mohm,当设置为1.5A以上时,通道阻抗为8mohm;芯片内部只检测这5个通道中最中间的那个通道的电流,是否正常。

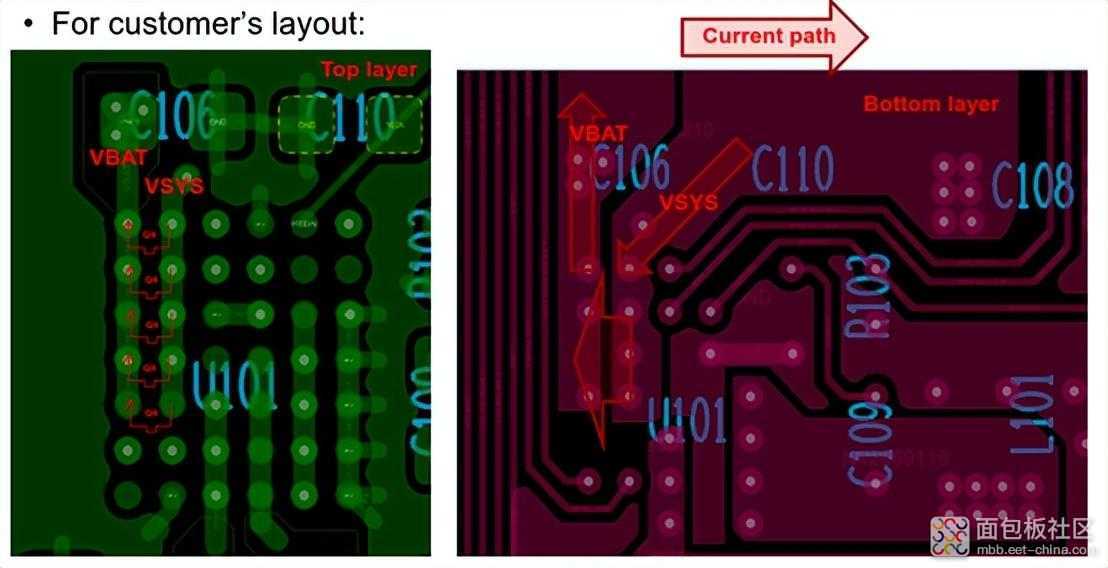

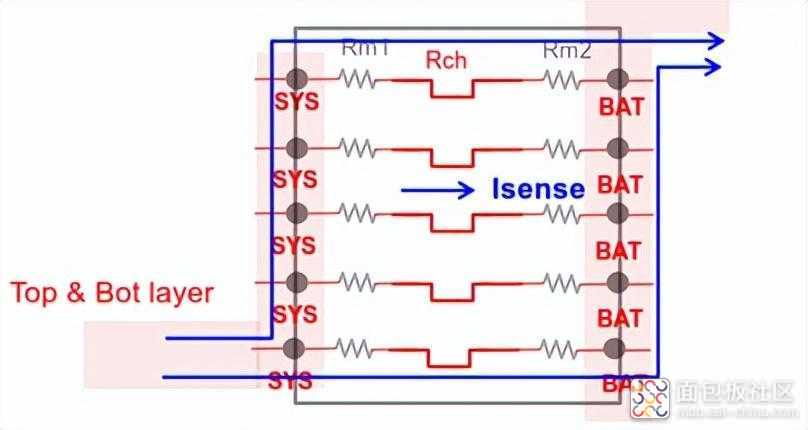

当时手机项目的走线情况如下:

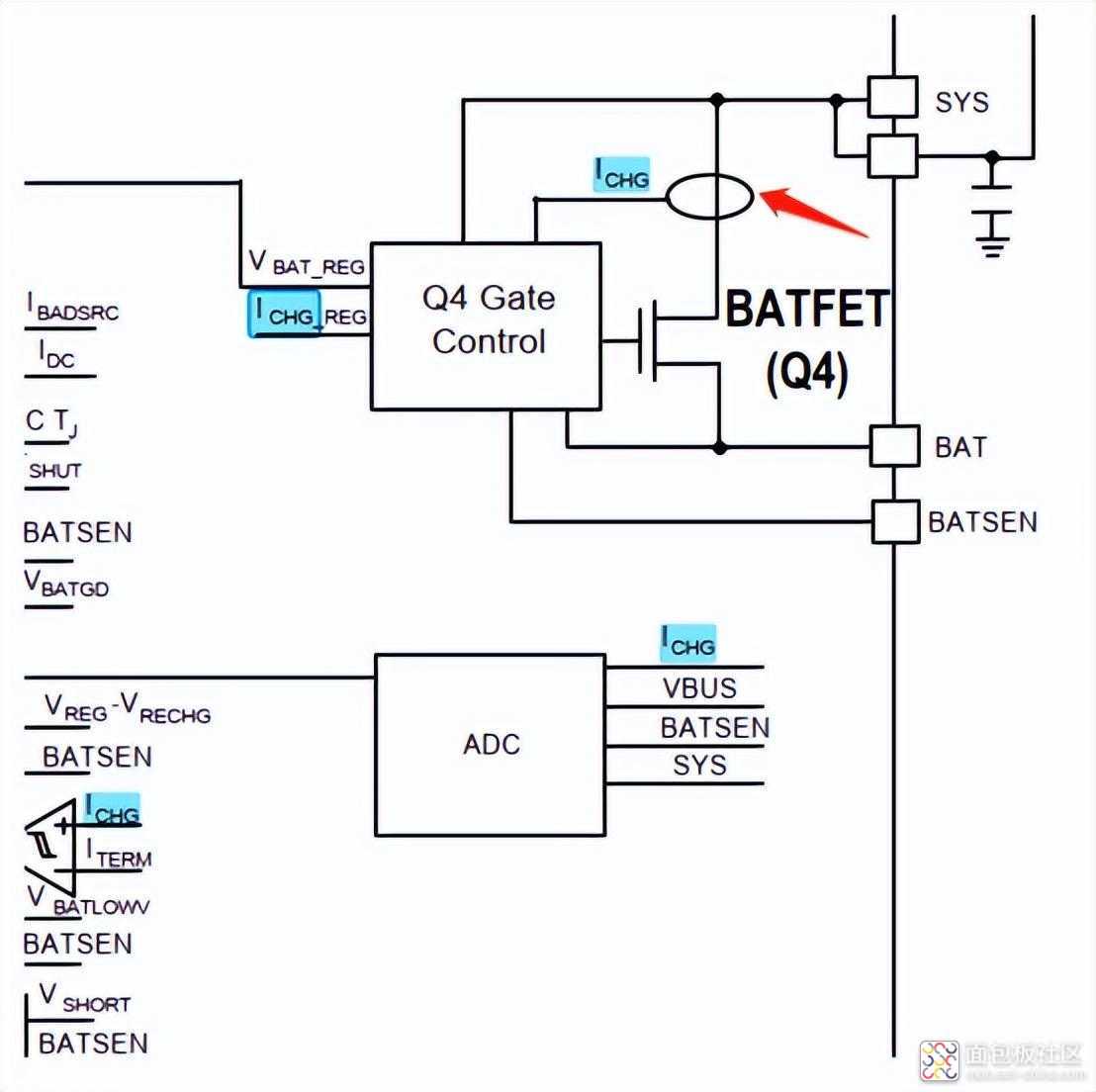

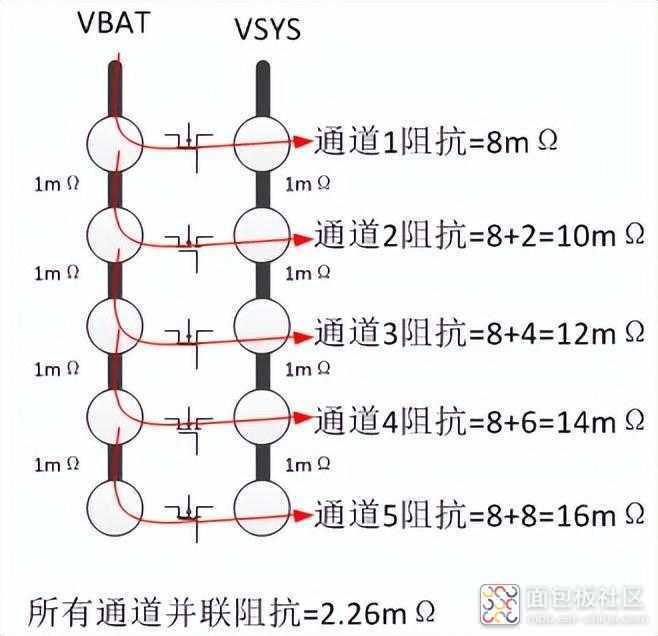

可以看到这5个通道分别占用了5对Pad,这个走线并不好,因为考虑到走线的阻抗,最上面的MOS的电流通路阻抗最小,最下面的MOS电流通路阻抗最大。我们对走线阻抗做如下假设:

图中计算的并联阻抗是从第一通道看进去,计算出的阻抗。

BQ25898是根据通道3两端的电压来判断,实际电流值与设置电流值是否一致。比如寄存器设置充电电流是1.5A,那么只要检测到通道3的电流是0.3A,芯片就认为正常。

当通道3电流是0.3A时,另外几个通道的电流计算如下:

从通道3的两个pad看出去,通道2和4的阻抗是一样的,通道1和5的阻抗是一样的。

通道2和4的电流=0.3Ax8/10=0.24A;

通道1和5的电流=0.3x8/12=0.2A;

所有通道电流之和=0.3A+0.24x2+0.2Ax2=1.18A。

很显然,实际电流不等于设置电流。

所以说,这个问题的根本原因是PCB Layout导致,BQ25898C的VSYS和VBAT的走线不好,没有让5个通道的MOS的电流路径对称。

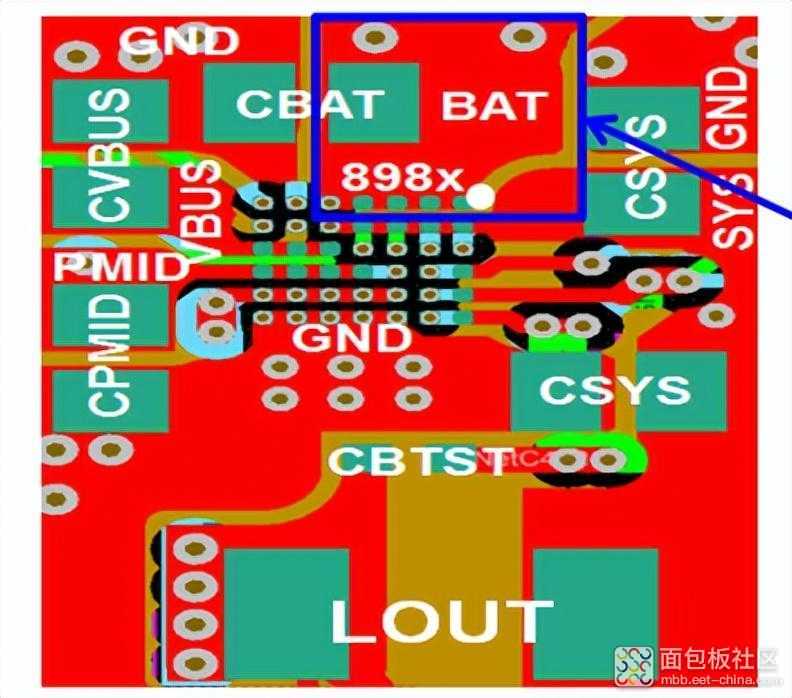

解决方案如下:

1、Vbat和Vsys的PIN铺一大块铜皮,并且加厚,减小阻抗。

2、保证每个通道的阻抗是对称的。

/4

/4