GD32H759拥有强大的显示功能,能轻松的驱动RGB屏,当然离不开LVGL这个强大的图形工具!由于此开发板刚推出来,查不到任何相关的LVGL的移植先例,花费了好几天,终于成功,特此分享如下:

【移植步骤】

1、下载官方源码:Gitee 极速下载/littlevGL

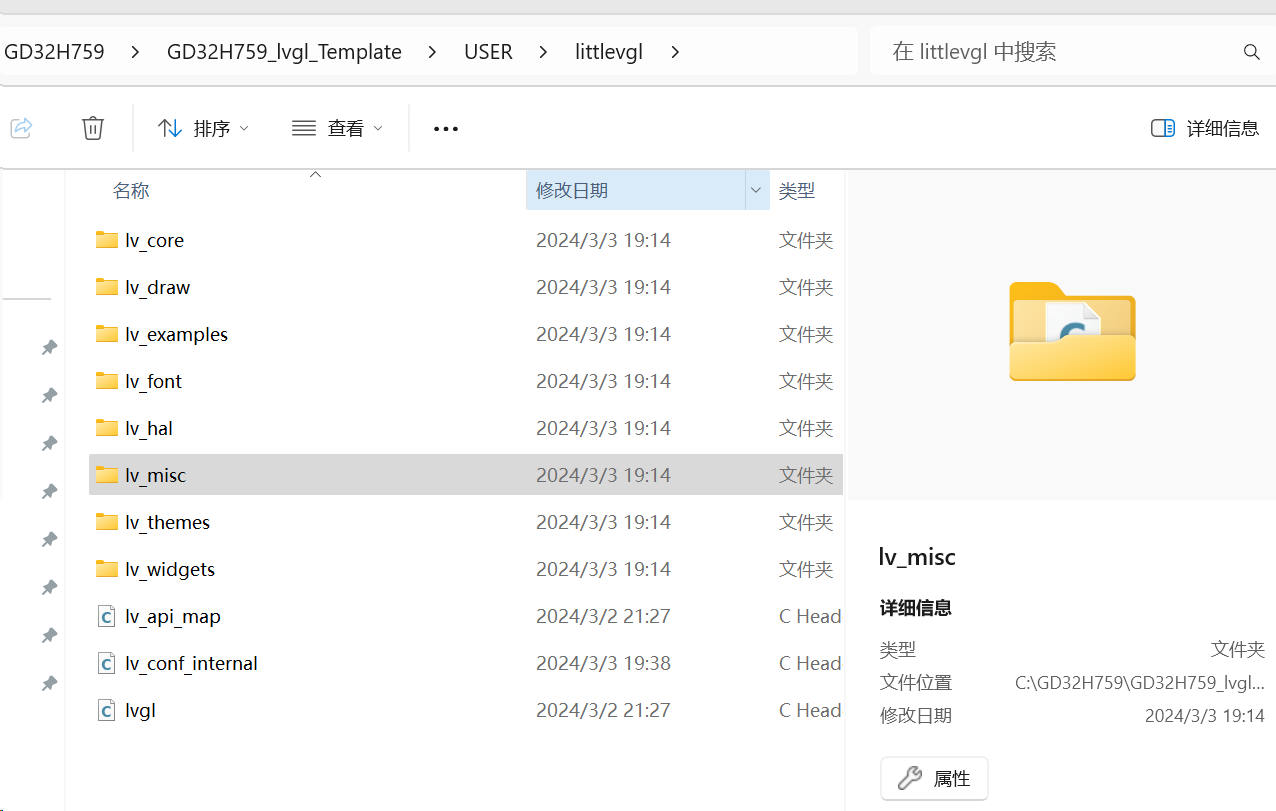

2、新建littlevlg文件夹,把src目录下的相关文件复制进来,复制后目录如下:

由于源码需要添加的目录太多,我这里根据网友的经验,把相关文件整一下,各位也可以根据其他的移植方法添加相关的文件与目录。

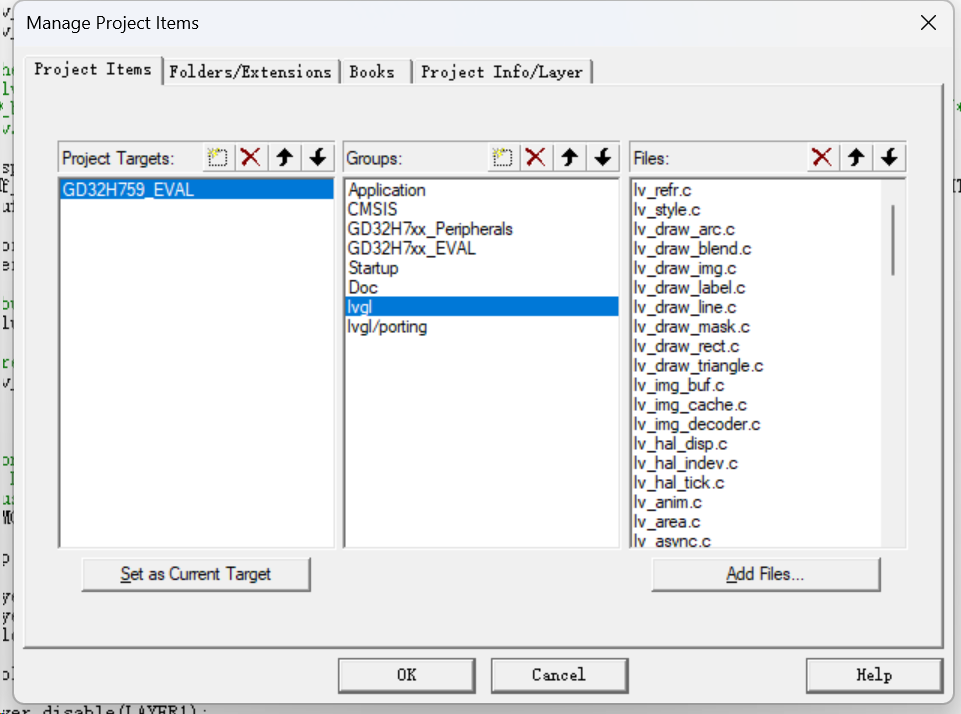

3、把以上文件下examples的目录,的所有文件均添加进工种分组中。

4、新建工程分组lvgl/porting,新建littlevgl_support.c以及.h文件。

5、在littlevgl_support.c,分别驱动屏幕驱动以及sram驱动。详细代码如下:

#include "gd32h7xx.h"

#include "systick.h"

#include <stdio.h>

#include "main.h"

#include "gd32h759i_eval.h"

#include "littlevgl_support.h"

#include "lvgl.h"

#include "lv_conf.h"

/*******************************************************************************

* Definitions

******************************************************************************/

#define HORIZONTAL_SYNCHRONOUS_PULSE 41

#define HORIZONTAL_BACK_PORCH 2

#define ACTIVE_WIDTH 480

#define HORIZONTAL_FRONT_PORCH 2

#define VERTICAL_SYNCHRONOUS_PULSE 10

#define VERTICAL_BACK_PORCH 2

#define ACTIVE_HEIGHT 272

#define VERTICAL_FRONT_PORCH 2

/*******************************************************************************

* Prototypes

******************************************************************************/

static void DEMO_FlushDisplay(lv_disp_drv_t * disp_drv, const lv_area_t * area, lv_color_t * color_p);

static bool DEMO_ReadTouch(lv_indev_drv_t * indev_drv, lv_indev_data_t *data);

static void tli_gpio_config(void);

static void tli_config_twolayout(void);

/*******************************************************************************

* Variables

******************************************************************************/

static volatile bool s_framePending;

// static lv_color_t buf2_1[LCD_WIDTH * LCD_HEIGHT * LCD_FB_BYTE_PER_PIXEL]; /*A buffer for 10 rows*/

// static lv_color_t buf2_2[LCD_WIDTH * LCD_HEIGHT * LCD_FB_BYTE_PER_PIXEL]; /*An other buffer for 10 rows*/

/*******************************************************************************

* SDRAM

******************************************************************************/

// #include "exmc_sdram.h"

/* Define mode register content */

/* Burst Length */

#define SDRAM_MODEREG_BURST_LENGTH_1 ((uint16_t)0x0000)

#define SDRAM_MODEREG_BURST_LENGTH_2 ((uint16_t)0x0001)

#define SDRAM_MODEREG_BURST_LENGTH_4 ((uint16_t)0x0002)

#define SDRAM_MODEREG_BURST_LENGTH_8 ((uint16_t)0x0003)

/* Burst Type */

#define SDRAM_MODEREG_BURST_TYPE_SEQUENTIAL ((uint16_t)0x0000)

#define SDRAM_MODEREG_BURST_TYPE_INTERLEAVED ((uint16_t)0x0008)

/* CAS Latency */

#define SDRAM_MODEREG_CAS_LATENCY_2 ((uint16_t)0x0020)

#define SDRAM_MODEREG_CAS_LATENCY_3 ((uint16_t)0x0030)

/* Write Mode */

#define SDRAM_MODEREG_WRITEBURST_MODE_PROGRAMMED ((uint16_t)0x0000)

#define SDRAM_MODEREG_WRITEBURST_MODE_SINGLE ((uint16_t)0x0200)

#define SDRAM_MODEREG_OPERATING_MODE_STANDARD ((uint16_t)0x0000)

#define SDRAM_TIMEOUT ((uint32_t)0x0000FFFF)

#define SDRAM_DEVICE0_ADDR ((uint32_t)0xC0000000)

/*!

\brief sdram peripheral initialize

\param[in] sdram_device: specifie the SDRAM device

\param[out] none

\retval none

*/

void exmc_synchronous_dynamic_ram_init(uint32_t sdram_device)

{

exmc_sdram_parameter_struct sdram_init_struct;

exmc_sdram_timing_parameter_struct sdram_timing_init_struct;

exmc_sdram_command_parameter_struct sdram_command_init_struct;

uint32_t command_content = 0, bank_select;

uint32_t timeout = SDRAM_TIMEOUT;

/* enable EXMC clock */

rcu_periph_clock_enable(RCU_EXMC);

rcu_periph_clock_enable(RCU_GPIOA);

rcu_periph_clock_enable(RCU_GPIOC);

rcu_periph_clock_enable(RCU_GPIOD);

rcu_periph_clock_enable(RCU_GPIOE);

rcu_periph_clock_enable(RCU_GPIOF);

rcu_periph_clock_enable(RCU_GPIOG);

rcu_periph_clock_enable(RCU_GPIOH);

/* common GPIO configuration */

/* SDNE0(PC2),SDCKE0(PC3) D12(PC0) pin configuration */

gpio_af_set(GPIOC, GPIO_AF_12, GPIO_PIN_2 | GPIO_PIN_3 | GPIO_PIN_0);

gpio_mode_set(GPIOC, GPIO_MODE_AF, GPIO_PUPD_PULLUP, GPIO_PIN_2 | GPIO_PIN_3 | GPIO_PIN_0);

gpio_output_options_set(GPIOC, GPIO_OTYPE_PP, GPIO_OSPEED_85MHZ, GPIO_PIN_2 | GPIO_PIN_3 | GPIO_PIN_0);

/* D2(PD0),D3(PD1),D13(PD8),D14(PD9),D15(PD10),D0(PD14),D1(PD15) pin configuration */

gpio_af_set(GPIOD, GPIO_AF_12, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_8 | GPIO_PIN_9 |

GPIO_PIN_10 | GPIO_PIN_14 | GPIO_PIN_15);

gpio_mode_set(GPIOD, GPIO_MODE_AF, GPIO_PUPD_PULLUP, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_8 | GPIO_PIN_9 |

GPIO_PIN_10 | GPIO_PIN_14 | GPIO_PIN_15);

gpio_output_options_set(GPIOD, GPIO_OTYPE_PP, GPIO_OSPEED_85MHZ, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_8 | GPIO_PIN_9 |

GPIO_PIN_10 | GPIO_PIN_14 | GPIO_PIN_15);

/* NBL0(PE0),NBL1(PE1),D4(PE7),D5(PE8),D6(PE9),D7(PE10),D8(PE11), D9(PE12),D10(PE13),D11(PE14) pin configuration */

gpio_af_set(GPIOE, GPIO_AF_12, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_7 | GPIO_PIN_8 |

GPIO_PIN_9 | GPIO_PIN_10 | GPIO_PIN_11 | GPIO_PIN_12 | GPIO_PIN_13 |

GPIO_PIN_14);

gpio_mode_set(GPIOE, GPIO_MODE_AF, GPIO_PUPD_PULLUP, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_7 | GPIO_PIN_8 |

GPIO_PIN_9 | GPIO_PIN_10 | GPIO_PIN_11 | GPIO_PIN_12 | GPIO_PIN_13 |

GPIO_PIN_14);

gpio_output_options_set(GPIOE, GPIO_OTYPE_PP, GPIO_OSPEED_85MHZ, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_7 | GPIO_PIN_8 |

GPIO_PIN_9 | GPIO_PIN_10 | GPIO_PIN_11 | GPIO_PIN_12 | GPIO_PIN_13 |

GPIO_PIN_14);

/* A0(PF0),A1(PF1),A2(PF2),A3(PF3),A4(PF4),A5(PF5),NRAS(PF11),A6(PF12),A7(PF13),A8(PF14),A9(PF15) pin configuration */

gpio_af_set(GPIOF, GPIO_AF_12, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_2 | GPIO_PIN_3 |

GPIO_PIN_4 | GPIO_PIN_5 | GPIO_PIN_11 | GPIO_PIN_12 |

GPIO_PIN_13 | GPIO_PIN_14 | GPIO_PIN_15);

gpio_mode_set(GPIOF, GPIO_MODE_AF, GPIO_PUPD_PULLUP, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_2 | GPIO_PIN_3 |

GPIO_PIN_4 | GPIO_PIN_5 | GPIO_PIN_11 | GPIO_PIN_12 |

GPIO_PIN_13 | GPIO_PIN_14 | GPIO_PIN_15);

gpio_output_options_set(GPIOF, GPIO_OTYPE_PP, GPIO_OSPEED_85MHZ, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_2 | GPIO_PIN_3 |

GPIO_PIN_4 | GPIO_PIN_5 | GPIO_PIN_11 | GPIO_PIN_12 |

GPIO_PIN_13 | GPIO_PIN_14 | GPIO_PIN_15);

/* A10(PG0),A11(PG1),A12(PG2),BA0/A14(PG4),BA1/A15(PG5),SDCLK(PG8),NCAS(PG15) pin configuration */

gpio_af_set(GPIOG, GPIO_AF_12, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_2 | GPIO_PIN_4 |

GPIO_PIN_5 | GPIO_PIN_8 | GPIO_PIN_15);

gpio_mode_set(GPIOG, GPIO_MODE_AF, GPIO_PUPD_PULLUP, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_2 | GPIO_PIN_4 |

GPIO_PIN_5 | GPIO_PIN_8 | GPIO_PIN_15);

gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_85MHZ, GPIO_PIN_0 | GPIO_PIN_1 | GPIO_PIN_2 | GPIO_PIN_4 |

GPIO_PIN_5 | GPIO_PIN_8 | GPIO_PIN_15);

/* SDNWE(PH5) pin configuration */

gpio_af_set(GPIOH, GPIO_AF_12, GPIO_PIN_5);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_PULLUP, GPIO_PIN_5);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_85MHZ, GPIO_PIN_5);

/* specify which SDRAM to read and write */

if(EXMC_SDRAM_DEVICE0 == sdram_device) {

bank_select = EXMC_SDRAM_DEVICE0_SELECT;

} else {

bank_select = EXMC_SDRAM_DEVICE1_SELECT;

}

/* EXMC SDRAM device initialization sequence --------------------------------*/

/* Step 1 : configure SDRAM timing registers --------------------------------*/

/* LMRD: 2 clock cycles */

sdram_timing_init_struct.load_mode_register_delay = 4;

/* XSRD: min = 67ns */

sdram_timing_init_struct.exit_selfrefresh_delay = 24;

/* RASD: min=42ns , max=120k (ns) */

sdram_timing_init_struct.row_address_select_delay = 16;

/* ARFD: min=60ns */

sdram_timing_init_struct.auto_refresh_delay = 11;

/* WRD: min=1 Clock cycles +6ns */

sdram_timing_init_struct.write_recovery_delay = 4;

/* RPD: min=18ns */

sdram_timing_init_struct.row_precharge_delay = 8;

/* RCD: min=18ns */

sdram_timing_init_struct.row_to_column_delay = 6;

/* step 2 : configure SDRAM control registers ---------------------------------*/

sdram_init_struct.sdram_device = sdram_device;

sdram_init_struct.column_address_width = EXMC_SDRAM_COW_ADDRESS_9;

sdram_init_struct.row_address_width = EXMC_SDRAM_ROW_ADDRESS_13;

sdram_init_struct.data_width = EXMC_SDRAM_DATABUS_WIDTH_16B;

sdram_init_struct.internal_bank_number = EXMC_SDRAM_4_INTER_BANK;

sdram_init_struct.cas_latency = EXMC_CAS_LATENCY_3_SDCLK;

sdram_init_struct.write_protection = DISABLE;

sdram_init_struct.sdclock_config = EXMC_SDCLK_PERIODS_3_CK_EXMC;

sdram_init_struct.burst_read_switch = ENABLE;

sdram_init_struct.pipeline_read_delay = EXMC_PIPELINE_DELAY_1_CK_EXMC;

sdram_init_struct.timing = &sdram_timing_init_struct;

/* EXMC SDRAM bank initialization */

exmc_sdram_init(&sdram_init_struct);

/* step 3 : configure CKE high command---------------------------------------*/

sdram_command_init_struct.command = EXMC_SDRAM_CLOCK_ENABLE;

sdram_command_init_struct.bank_select = bank_select;

sdram_command_init_struct.auto_refresh_number = EXMC_SDRAM_AUTO_REFLESH_1_SDCLK;

sdram_command_init_struct.mode_register_content = 0;

/* wait until the SDRAM controller is ready */

while((exmc_flag_get(sdram_device, EXMC_SDRAM_FLAG_NREADY) != RESET) && (timeout > 0)) {

timeout--;

}

/* send the command */

exmc_sdram_command_config(&sdram_command_init_struct);

/* step 4 : insert 10ms delay----------------------------------------------*/

delay_1ms(100);

/* step 5 : configure precharge all command----------------------------------*/

sdram_command_init_struct.command = EXMC_SDRAM_PRECHARGE_ALL;

sdram_command_init_struct.bank_select = bank_select;

sdram_command_init_struct.auto_refresh_number = EXMC_SDRAM_AUTO_REFLESH_1_SDCLK;

sdram_command_init_struct.mode_register_content = 0;

/* wait until the SDRAM controller is ready */

timeout = SDRAM_TIMEOUT;

while((exmc_flag_get(sdram_device, EXMC_SDRAM_FLAG_NREADY) != RESET) && (timeout > 0)) {

timeout--;

}

/* send the command */

exmc_sdram_command_config(&sdram_command_init_struct);

/* step 6 : configure Auto-Refresh command-----------------------------------*/

sdram_command_init_struct.command = EXMC_SDRAM_AUTO_REFRESH;

sdram_command_init_struct.bank_select = bank_select;

sdram_command_init_struct.auto_refresh_number = EXMC_SDRAM_AUTO_REFLESH_8_SDCLK;

sdram_command_init_struct.mode_register_content = 0;

/* wait until the SDRAM controller is ready */

timeout = SDRAM_TIMEOUT;

while((exmc_flag_get(sdram_device, EXMC_SDRAM_FLAG_NREADY) != RESET) && (timeout > 0)) {

timeout--;

}

/* send the command */

exmc_sdram_command_config(&sdram_command_init_struct);

/* step 7 : configure load mode register command-----------------------------*/

/* program mode register */

command_content = (uint32_t)SDRAM_MODEREG_BURST_LENGTH_1 |

SDRAM_MODEREG_BURST_TYPE_SEQUENTIAL |

SDRAM_MODEREG_CAS_LATENCY_3 |

SDRAM_MODEREG_OPERATING_MODE_STANDARD |

SDRAM_MODEREG_WRITEBURST_MODE_SINGLE;

sdram_command_init_struct.command = EXMC_SDRAM_LOAD_MODE_REGISTER;

sdram_command_init_struct.bank_select = bank_select;

sdram_command_init_struct.auto_refresh_number = EXMC_SDRAM_AUTO_REFLESH_1_SDCLK;

sdram_command_init_struct.mode_register_content = command_content;

/* wait until the SDRAM controller is ready */

timeout = SDRAM_TIMEOUT;

while((exmc_flag_get(sdram_device, EXMC_SDRAM_FLAG_NREADY) != RESET) && (timeout > 0)) {

timeout--;

}

/* send the command */

exmc_sdram_command_config(&sdram_command_init_struct);

/* step 8 : set the auto-refresh rate counter--------------------------------*/

/* 64ms, 8192-cycle refresh, 64ms/8192=7.81us */

/* SDCLK_Freq = SYS_Freq/2 */

/* (7.81 us * SDCLK_Freq) - 20 */

exmc_sdram_refresh_count_set(1542);

/* wait until the SDRAM controller is ready */

timeout = SDRAM_TIMEOUT;

while((exmc_flag_get(sdram_device, EXMC_SDRAM_FLAG_NREADY) != RESET) && (timeout > 0)) {

timeout--;

}

}

/*******************************************************************************

* Code

******************************************************************************/

void lv_port_disp_init(void)

{

/*-------------------------

* Initialize your display

* -----------------------*/

exmc_synchronous_dynamic_ram_init(EXMC_SDRAM_DEVICE0);

delay_1ms(1);

memset((void *)EXT_BUFFER0_ADDR, 0, LCD_WIDTH * LCD_HEIGHT * LCD_FB_BYTE_PER_PIXEL*4);

memset((void *)EXT_BUFFER1_ADDR, 0, LCD_WIDTH * LCD_HEIGHT * LCD_FB_BYTE_PER_PIXEL*4);

tli_gpio_config();

tli_config_twolayout();

tli_layer_enable(LAYER0);

tli_reload_config(TLI_REQUEST_RELOAD_EN);

tli_enable();

/*-----------------------------------

* Register the display in LittlevGL

*----------------------------------*/

lv_disp_drv_t disp_drv; /*Descriptor of a display driver*/

lv_disp_drv_init(&disp_drv); /*Basic initialization*/

/*Set up the functions to access to your display*/

// static lv_disp_buf_t disp_buf_2;

// lv_disp_buf_init(&disp_buf_2, buf2_1, buf2_2, LCD_WIDTH * LCD_HEIGHT * LCD_FB_BYTE_PER_PIXEL); /*Initialize the display buffer*/

// disp_drv.buffer = &disp_buf_2;

static lv_disp_buf_t disp_buf;

lv_disp_buf_init(&disp_buf, (void *)EXT_BUFFER0_ADDR, (void *)EXT_BUFFER1_ADDR, LCD_WIDTH * LCD_HEIGHT * LCD_FB_BYTE_PER_PIXEL);

disp_drv.buffer = &disp_buf;

disp_drv.hor_res = LCD_WIDTH;

disp_drv.ver_res = LCD_HEIGHT;

/*Used in buffered mode (LV_VDB_SIZE != 0 in lv_conf.h)*/

disp_drv.flush_cb = DEMO_FlushDisplay;

/*Finally register the driver*/

lv_disp_drv_register(&disp_drv);

}

/* Flush the content of the internal buffer the specific area on the display

* You can use DMA or any hardware acceleration to do this operation in the background but

* 'lv_disp_flush_ready()' has to be called when finished*/

static void DEMO_FlushDisplay(lv_disp_drv_t * disp_drv, const lv_area_t * area, lv_color_t * color_p)

{

if (color_p == EXT_BUFFER0_ADDR)

{

tli_layer_disable(LAYER0);

tli_layer_enable(LAYER1);

tli_reload_config(TLI_FRAME_BLANK_RELOAD_EN);

}

else if (color_p == EXT_BUFFER1_ADDR)

{

tli_layer_disable(LAYER1);

tli_layer_enable(LAYER0);

tli_reload_config(TLI_FRAME_BLANK_RELOAD_EN);

}

/* IMPORTANT!!!

* Inform the graphics library that you are ready with the flushing*/

lv_disp_flush_ready(disp_drv);

}

static void tli_config_twolayout(void)

{

tli_parameter_struct tli_init_struct;

tli_layer_parameter_struct tli_layer_init_struct;

rcu_periph_clock_enable(RCU_TLI);

tli_gpio_config();

/* configure PLL2 to generate TLI clock 25MHz/25*216/3 = 72MHz */

rcu_pll_input_output_clock_range_config(IDX_PLL2, RCU_PLL2RNG_1M_2M, RCU_PLL2VCO_150M_420M);

if(ERROR == rcu_pll2_config(50, 188, 9, 9, 9)) {

while(1) {

}

}

rcu_pll_clock_output_enable(RCU_PLL2R);

rcu_tli_clock_div_config(RCU_PLL2R_DIV8);

rcu_osci_on(RCU_PLL2_CK);

if(ERROR == rcu_osci_stab_wait(RCU_PLL2_CK)) {

while(1) {

}

}

/* configure TLI parameter struct */

tli_init_struct.signalpolarity_hs = TLI_HSYN_ACTLIVE_LOW;

tli_init_struct.signalpolarity_vs = TLI_VSYN_ACTLIVE_LOW;

tli_init_struct.signalpolarity_de = TLI_DE_ACTLIVE_LOW;

tli_init_struct.signalpolarity_pixelck = TLI_PIXEL_CLOCK_TLI;

/* LCD display timing configuration */

tli_init_struct.synpsz_hpsz = HORIZONTAL_SYNCHRONOUS_PULSE - 1;

tli_init_struct.synpsz_vpsz = VERTICAL_SYNCHRONOUS_PULSE - 1;

tli_init_struct.backpsz_hbpsz = HORIZONTAL_SYNCHRONOUS_PULSE + HORIZONTAL_BACK_PORCH - 1;

tli_init_struct.backpsz_vbpsz = VERTICAL_SYNCHRONOUS_PULSE + VERTICAL_BACK_PORCH - 1;

tli_init_struct.activesz_hasz = HORIZONTAL_SYNCHRONOUS_PULSE + HORIZONTAL_BACK_PORCH + ACTIVE_WIDTH - 1;

tli_init_struct.activesz_vasz = VERTICAL_SYNCHRONOUS_PULSE + VERTICAL_BACK_PORCH + ACTIVE_HEIGHT - 1;

tli_init_struct.totalsz_htsz = HORIZONTAL_SYNCHRONOUS_PULSE + HORIZONTAL_BACK_PORCH + ACTIVE_WIDTH + HORIZONTAL_FRONT_PORCH - 1;

tli_init_struct.totalsz_vtsz = VERTICAL_SYNCHRONOUS_PULSE + VERTICAL_BACK_PORCH + ACTIVE_HEIGHT + VERTICAL_FRONT_PORCH - 1;

/* configure LCD background R,G,B values */

tli_init_struct.backcolor_red = 0xFF;

tli_init_struct.backcolor_green = 0xFF;

tli_init_struct.backcolor_blue = 0xFF;

tli_init(&tli_init_struct);

/* TLI layer1 configuration */

/* TLI window size configuration */

tli_layer_init_struct.layer_window_leftpos = HORIZONTAL_SYNCHRONOUS_PULSE + HORIZONTAL_BACK_PORCH;

tli_layer_init_struct.layer_window_rightpos = (LCD_WIDTH + HORIZONTAL_SYNCHRONOUS_PULSE + HORIZONTAL_BACK_PORCH - 1);

tli_layer_init_struct.layer_window_toppos = VERTICAL_SYNCHRONOUS_PULSE + VERTICAL_BACK_PORCH;

tli_layer_init_struct.layer_window_bottompos = (LCD_HEIGHT + VERTICAL_SYNCHRONOUS_PULSE + VERTICAL_BACK_PORCH - 1);

/* TLI window pixel format configuration */

tli_layer_init_struct.layer_ppf = LAYER_PPF_RGB565;

/* TLI window specified alpha configuration */

tli_layer_init_struct.layer_sa = 255;

/* TLI window blend configuration */

tli_layer_init_struct.layer_acf1 = LAYER_ACF1_PASA;

tli_layer_init_struct.layer_acf2 = LAYER_ACF2_PASA;

/* TLI layer default alpha R,G,B value configuration */

tli_layer_init_struct.layer_default_alpha = 0;

tli_layer_init_struct.layer_default_blue = 0xFF;

tli_layer_init_struct.layer_default_green = 0xFF;

tli_layer_init_struct.layer_default_red = 0xFF;

/* TLI layer frame buffer base address configuration */

tli_layer_init_struct.layer_frame_bufaddr = (uint32_t)EXT_BUFFER0_ADDR;

tli_layer_init_struct.layer_frame_line_length = ((LCD_WIDTH * 2) + 3);

tli_layer_init_struct.layer_frame_buf_stride_offset = (LCD_WIDTH * 4);

tli_layer_init_struct.layer_frame_total_line_number = LCD_HEIGHT;

tli_layer_init(LAYER1, &tli_layer_init_struct);

/* TLI layer0 configuration */

tli_layer_init_struct.layer_window_leftpos = HORIZONTAL_SYNCHRONOUS_PULSE + HORIZONTAL_BACK_PORCH;

tli_layer_init_struct.layer_window_rightpos = (LCD_WIDTH + HORIZONTAL_SYNCHRONOUS_PULSE + HORIZONTAL_BACK_PORCH - 1);

tli_layer_init_struct.layer_window_toppos = VERTICAL_SYNCHRONOUS_PULSE + VERTICAL_BACK_PORCH;

tli_layer_init_struct.layer_window_bottompos = (LCD_HEIGHT + VERTICAL_SYNCHRONOUS_PULSE + VERTICAL_BACK_PORCH - 1);

tli_layer_init_struct.layer_ppf = LAYER_PPF_RGB565;

/* TLI window specified alpha configuration */

tli_layer_init_struct.layer_sa = 255;

/* TLI layer default alpha R,G,B value configuration */

tli_layer_init_struct.layer_default_blue = 0xFF;

tli_layer_init_struct.layer_default_green = 0xFF;

tli_layer_init_struct.layer_default_red = 0xFF;

tli_layer_init_struct.layer_default_alpha = 0xFF;

/* TLI window blend configuration */

tli_layer_init_struct.layer_acf1 = LAYER_ACF1_PASA;

tli_layer_init_struct.layer_acf2 = LAYER_ACF2_PASA;

/* TLI layer frame buffer base address configuration */

tli_layer_init_struct.layer_frame_bufaddr = (uint32_t)EXT_BUFFER1_ADDR;

tli_layer_init_struct.layer_frame_line_length = ((LCD_WIDTH * 2) + 3);

tli_layer_init_struct.layer_frame_buf_stride_offset = (LCD_WIDTH * 4);

tli_layer_init_struct.layer_frame_total_line_number = LCD_HEIGHT;

tli_layer_init(LAYER0, &tli_layer_init_struct);

tli_dither_config(TLI_DITHER_ENABLE);

}

/*!

\brief configure TLI GPIO

\param[in] none

\param[out] none

\retval none

*/

void tli_gpio_config(void)

{

/* enable GPIO clock */

rcu_periph_clock_enable(RCU_GPIOA);

rcu_periph_clock_enable(RCU_GPIOB);

rcu_periph_clock_enable(RCU_GPIOC);

rcu_periph_clock_enable(RCU_GPIOD);

rcu_periph_clock_enable(RCU_GPIOE);

rcu_periph_clock_enable(RCU_GPIOF);

rcu_periph_clock_enable(RCU_GPIOH);

rcu_periph_clock_enable(RCU_GPIOG);

/* configure HSYNC(PE15), VSYNC(PA7), PCLK(PG7) */

gpio_af_set(GPIOE, GPIO_AF_14, GPIO_PIN_15);

gpio_af_set(GPIOA, GPIO_AF_14, GPIO_PIN_7);

gpio_af_set(GPIOG, GPIO_AF_14, GPIO_PIN_7);

gpio_mode_set(GPIOE, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_15);

gpio_output_options_set(GPIOE, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_15);

gpio_mode_set(GPIOA, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_7);

gpio_output_options_set(GPIOA, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_7);

gpio_mode_set(GPIOG, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_7);

gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_7);

/* configure LCD_R7(PG6), LCD_R6(PH12), LCD_R5(PH11), LCD_R4(PA5), LCD_R3(PH9),LCD_R2(PH8),

LCD_R1(PH3), LCD_R0(PH2) */

gpio_af_set(GPIOG, GPIO_AF_14, GPIO_PIN_6);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_12);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_11);

gpio_af_set(GPIOA, GPIO_AF_14, GPIO_PIN_5);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_9);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_8);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_3);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_2);

gpio_mode_set(GPIOG, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_6);

gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_6);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_12);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_12);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_11);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_11);

gpio_mode_set(GPIOA, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_5);

gpio_output_options_set(GPIOA, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_5);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_9);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_9);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_8);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_8);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_3);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_3);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_2);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_2);

/* configure LCD_G7(PD3), LCD_G6(PC7), LCD_G5(PC1), LCD_G4(PH15), LCD_G3(PH14), LCD_G2(PH13),LCD_G1(PB0), LCD_G0(PB1) */

gpio_af_set(GPIOD, GPIO_AF_14, GPIO_PIN_3);

gpio_af_set(GPIOC, GPIO_AF_14, GPIO_PIN_7);

gpio_af_set(GPIOC, GPIO_AF_14, GPIO_PIN_1);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_15);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_14);

gpio_af_set(GPIOH, GPIO_AF_14, GPIO_PIN_13);

gpio_af_set(GPIOB, GPIO_AF_14, GPIO_PIN_0);

gpio_af_set(GPIOB, GPIO_AF_14, GPIO_PIN_1);

gpio_mode_set(GPIOD, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_3);

gpio_output_options_set(GPIOD, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_3);

gpio_mode_set(GPIOC, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_7);

gpio_output_options_set(GPIOC, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_7);

gpio_mode_set(GPIOC, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_1);

gpio_output_options_set(GPIOC, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_1);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_15);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_15);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_14);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_14);

gpio_mode_set(GPIOH, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_13);

gpio_output_options_set(GPIOH, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_13);

gpio_mode_set(GPIOB, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_0);

gpio_output_options_set(GPIOB, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_0);

gpio_mode_set(GPIOB, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_1);

gpio_output_options_set(GPIOB, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_1);

/* configure LCD_B7(PB9), LCD_B6(PB8), LCD_B5(PB5), LCD_B4(PC11), LCD_B3(PG11),LCD_B2(PG10), LCD_B1(PG12), LCD_B0(PG14) */

gpio_af_set(GPIOB, GPIO_AF_14, GPIO_PIN_9);

gpio_af_set(GPIOB, GPIO_AF_14, GPIO_PIN_8);

gpio_af_set(GPIOB, GPIO_AF_3, GPIO_PIN_5);

gpio_af_set(GPIOC, GPIO_AF_14, GPIO_PIN_11);

gpio_af_set(GPIOG, GPIO_AF_14, GPIO_PIN_11);

gpio_af_set(GPIOG, GPIO_AF_14, GPIO_PIN_10);

gpio_af_set(GPIOG, GPIO_AF_14, GPIO_PIN_12);

gpio_af_set(GPIOG, GPIO_AF_14, GPIO_PIN_14);

gpio_mode_set(GPIOB, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_9);

gpio_output_options_set(GPIOB, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_9);

gpio_mode_set(GPIOB, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_8);

gpio_output_options_set(GPIOB, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_8);

gpio_mode_set(GPIOB, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_5);

gpio_output_options_set(GPIOB, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_5);

gpio_mode_set(GPIOC, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_11);

gpio_output_options_set(GPIOC, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_11);

gpio_mode_set(GPIOG, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_11);

gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_11);

gpio_mode_set(GPIOG, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_10);

gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_10);

gpio_mode_set(GPIOG, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_12);

gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_12);

gpio_mode_set(GPIOG, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_14);

gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_14);

/* configure LCD_DE(PF10) */

gpio_af_set(GPIOF, GPIO_AF_14, GPIO_PIN_10);

gpio_mode_set(GPIOF, GPIO_MODE_AF, GPIO_PUPD_NONE, GPIO_PIN_10);

gpio_output_options_set(GPIOF, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_10);

/* LCD PWM BackLight(PG13) */

gpio_mode_set(GPIOG, GPIO_MODE_OUTPUT, GPIO_PUPD_PULLUP, GPIO_PIN_13);

gpio_output_options_set(GPIOG, GPIO_OTYPE_PP, GPIO_OSPEED_60MHZ, GPIO_PIN_13);

gpio_bit_set(GPIOG, GPIO_PIN_13);

}

复制代码 lv_init();

lv_port_disp_init();

// lv_port_indev_init();

lv_obj_t* obj1 = lv_obj_create(lv_scr_act(),NULL);

lv_obj_set_height(obj1, 200); //只设置高度

lv_obj_set_width(obj1, 300); //只设置宽度

lv_obj_set_size(obj1, 300,200); //设置宽高

lv_obj_set_x(obj1, 10);//设置x

lv_obj_set_y(obj1, 20);//设置y

lv_obj_set_pos(obj1, 10,20);//设置xy

lv_obj_t *label = lv_label_create(lv_scr_act(),NULL);

lv_obj_set_x(label, 10);//设置x

lv_obj_set_y(label, 20);//设置y

lv_label_set_text(label,"Hello World\r\n GD32H759\r\n mbb.eet-china.com");

while(1) {

/* turn on LED1, turn off LED2 */

delay_1ms(2);

lv_tick_inc(2);

lv_task_handler();

mytick++;

if(mytick < 100)

{

gpio_bit_reset(GPIOA, GPIO_PIN_6);

gpio_bit_reset(GPIOF, GPIO_PIN_10);

}

else if(mytick>300 )

{

mytick = 0;

}

else

{

gpio_bit_set(GPIOA, GPIO_PIN_6);

gpio_bit_set(GPIOF, GPIO_PIN_10);

}

}

复制代码

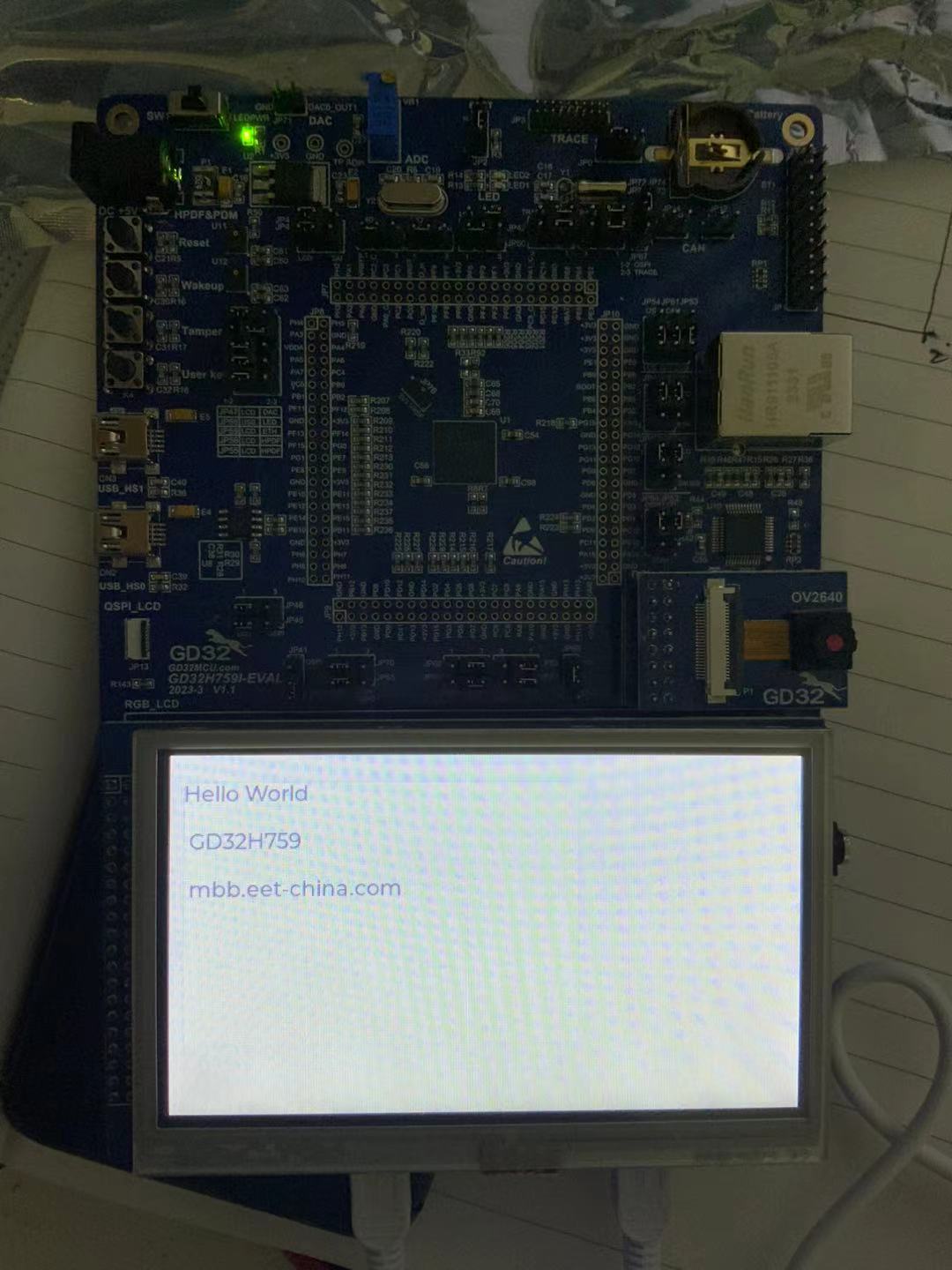

【总结】

GD32H759有着强大的显示加速功能,配合LVGL,可以在图形方面胜出友商不少。

/2

/2