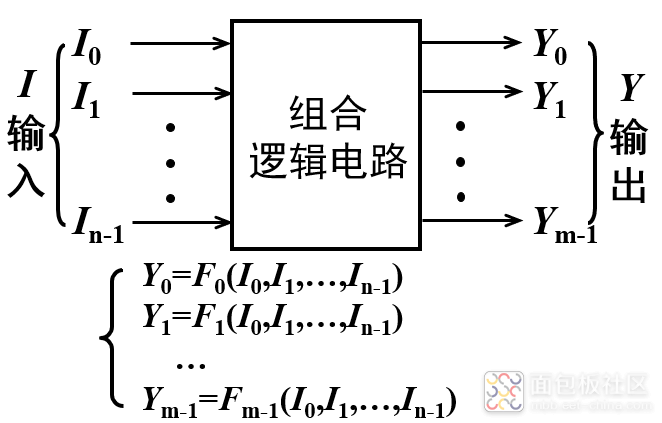

组合逻辑电路的特点:

逻辑功能的特点:任意时刻的稳定输出仅仅取决于当时的输入信号,而与电路原来的状态无关。

电路结构的特点:

1)由门电路组合而成,不包含任何记忆元件;

2)信号是单向传输的,不存在输出到输入的反馈回路。、

组合电路逻辑功能的表示方法:

逻辑图、真值表、卡诺图、逻辑表达式及时间图等。

组合逻辑电路的分类

1)按照逻辑功能特点不同划分:加法器、比较器、编码器、译码器、数据选择器和分配器、只读存储器等。

2)按照使用基本开关元件不同划分:CMOS、TTL等。

3)按照集成度不同划分:SSI(Small Scale IC,小规模集成电路 )、MSI (Medium Scale IC,中规模集成电路 ) 、LSI (Large Scale IC,大规模集成电路 ) 、VLSI (Very Large Scale IC,超大规模集成电路 )等。

1、组合电路的基本分析方法

①根据给定的逻辑图写出输出函数的逻辑表达式。

②化简逻辑表达式,求出输出函数的最简与或表达式。

③列出输出函数的真值表。

④描述电路的逻辑功能。

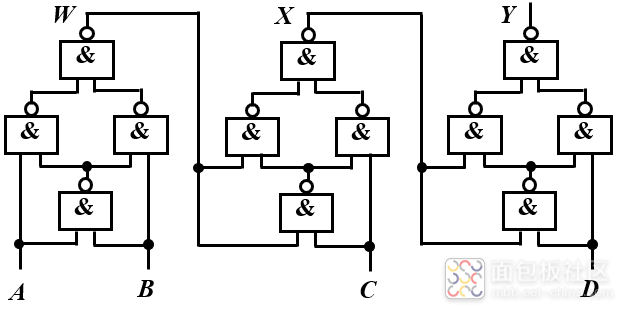

例:试分析下图所示电路的逻辑功能,图中输入信号A、B、C、D是一组4位二进制代码。

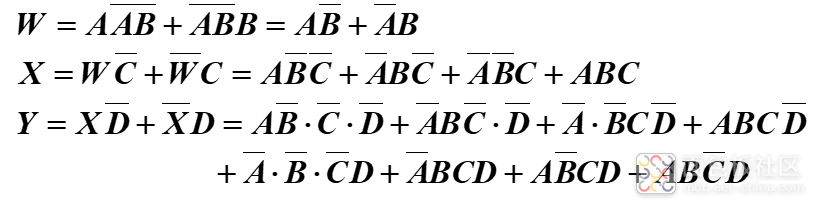

解:⑴ 写输出函数Y的逻辑表达式

⑵ 进行化简

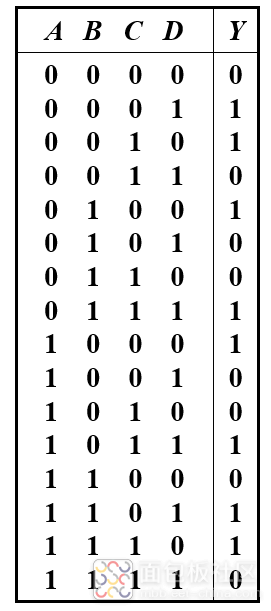

⑶ 列真值表

⑷ 功能说明

由上表所示真值表可以看出,所示的逻辑图是一个检奇电路,即当输入4位二进制代码A、B、C、D的取值中,1的个数为奇数时输出Y为1,反之,为偶数时输出Y为0。

2、组合电路的基本设计方法:

设计方法:

1、进行逻辑抽象

①分析设计要求,确定输入、输出信号及它们之间的因果关系。

②设定变量,即用英文字母表示有关输入、输出信号,表示输入信号者称为输入变量,表示输出信号者称为输出变量。

③状态赋值,即用0和1表示信号的有关状态。

④列真值表。根据因果关系,把变量的各种取值和相应的函数值,以表格形式一一列出,而变量取值顺序则常按二进制数递增排列,也可按循环码排列。

2、进行化简

①输入变量比较少时,可以用卡诺图化简。

②输入变量比较多时,可以用公式法化简。

3、画逻辑图

①变换最简与或表达式,求出所需要的最简式。

②根据最简式画出逻辑图。

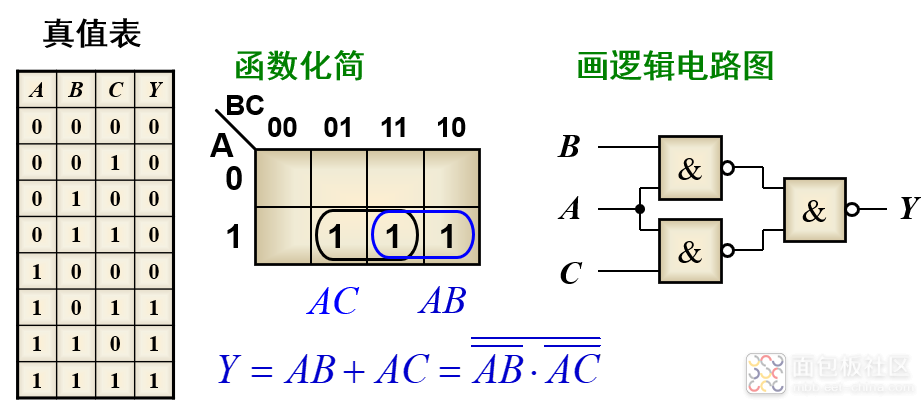

例:设计一个三变量表决器,其中A具有否决权。

解:首先确定输入变量:

设:A,B,C为输入变量,Y为输出结果。

规定:A,B,C为1表示赞成,为0表示反对。Y=1表示通过,Y=0 表示没有通过。

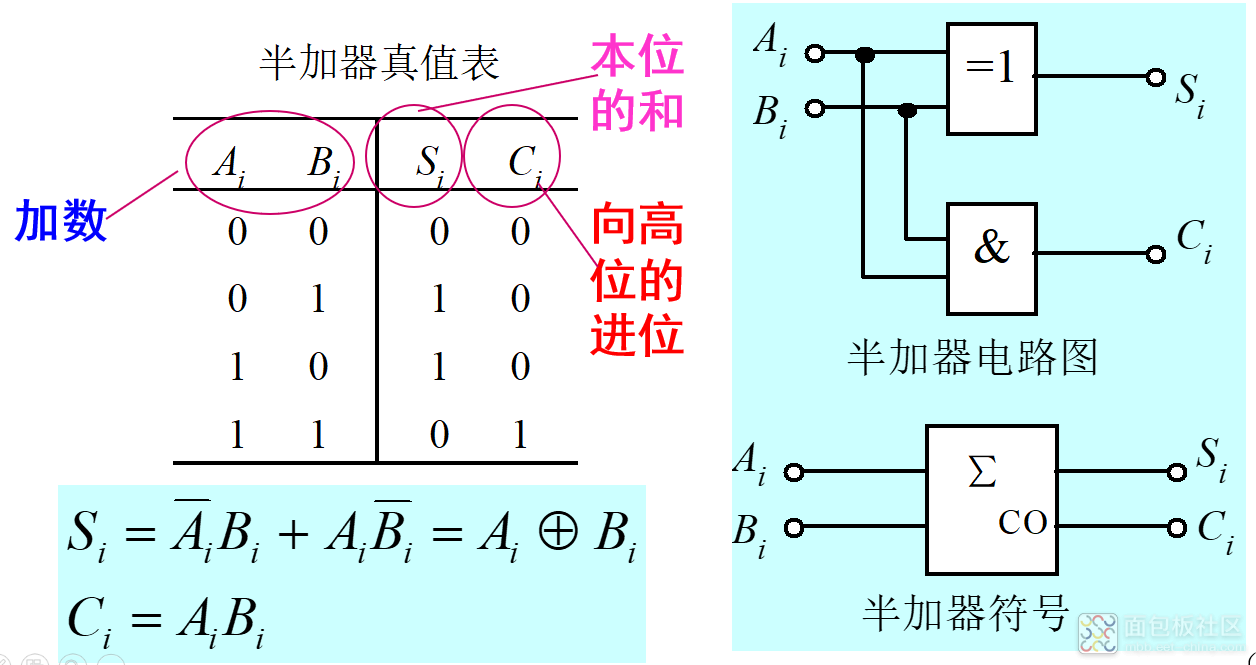

半加器:

两个1位二进制数相加,而且不考虑低位进位的器件。

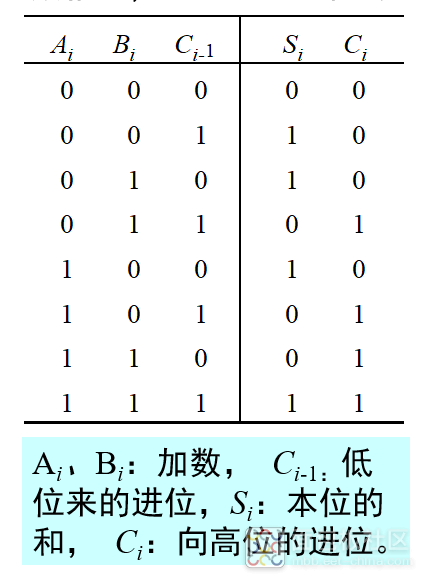

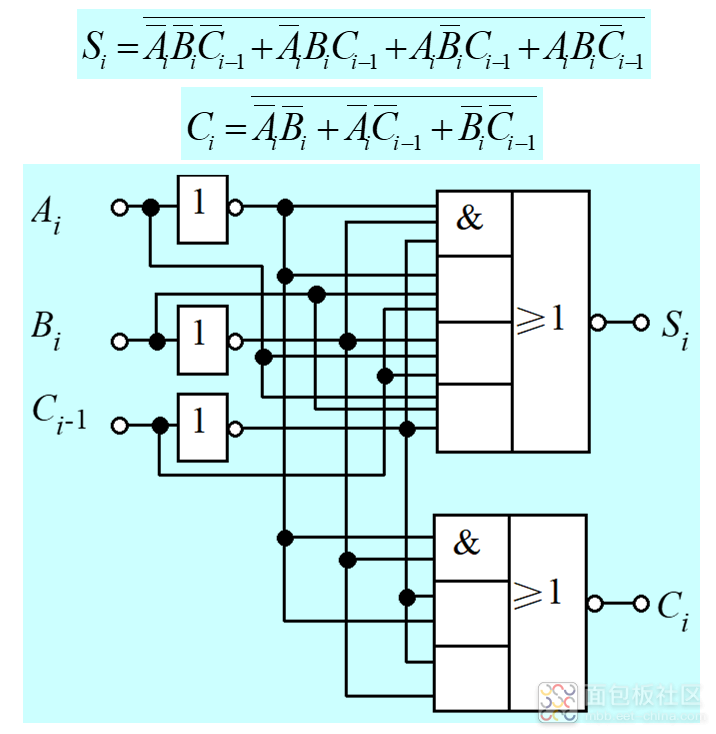

全加器:

能对两个1位二进制数进行相加并考虑低位来的进位,即相当于3个1位二进制数相加,求得和及进位的逻辑电路称为全加器。

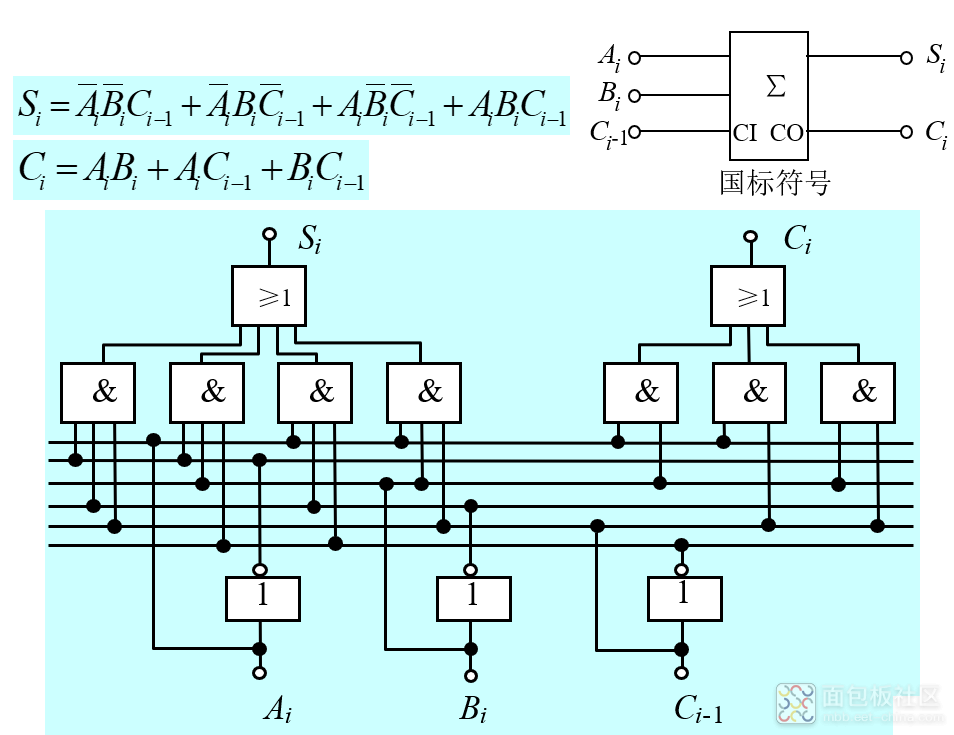

用与门和或门实现:

用与或非门和非门实现:

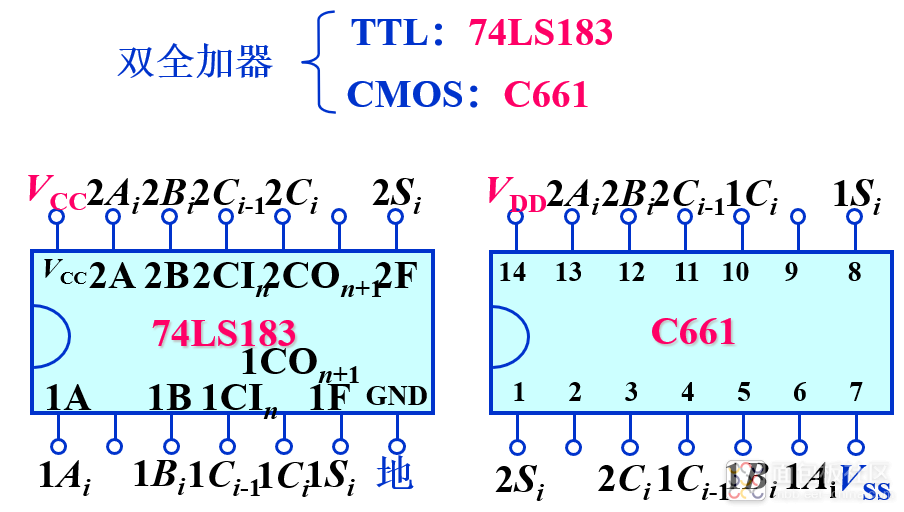

集成全加器:

加法器:

实现多位二进制数相加的电路称为加法器。

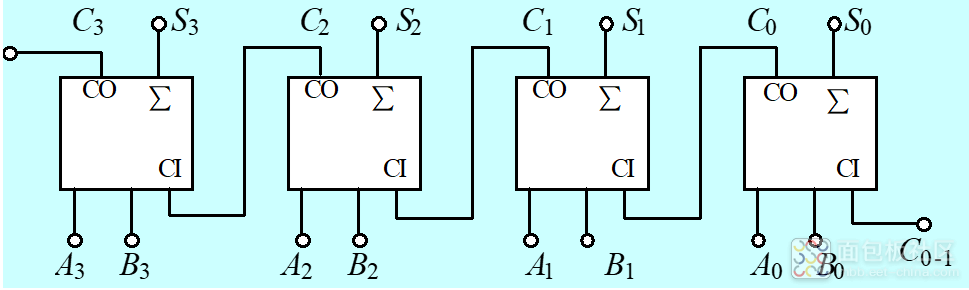

1、4位串行进位加法器

构成:把4个全加器串联起来,低位全加器的进位输出连接到相邻的高位全加器的进位输入。

由于每一位相加结果,必须等到低一位的进位产生以后才能建立,因此这种结构也叫做逐位进位加法器。其特点是结构简单,最大缺点是运算速度慢。为了提高运算速度,必须减小或消除由于进位信号逐位传递所消耗的时间,采用超前进位加法器。

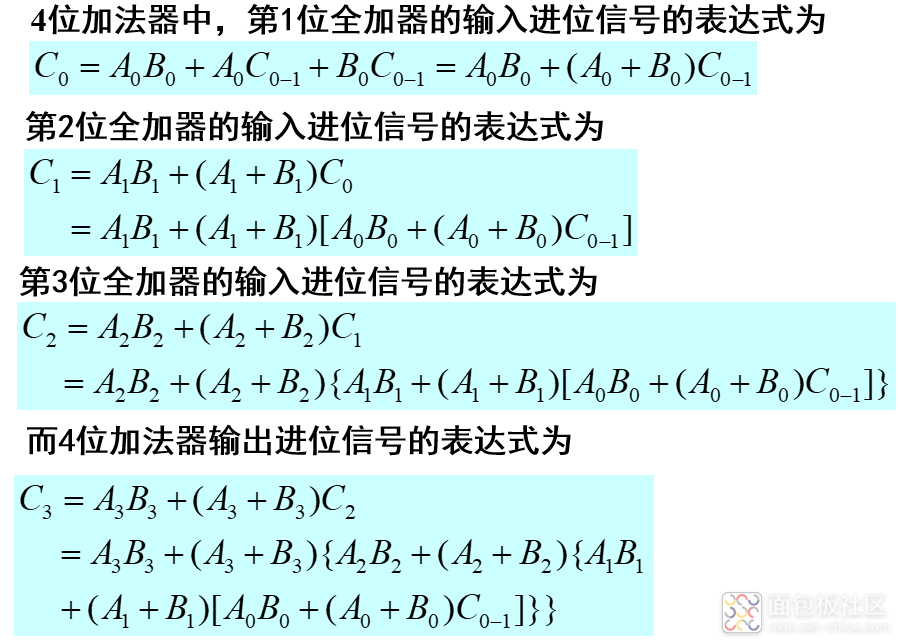

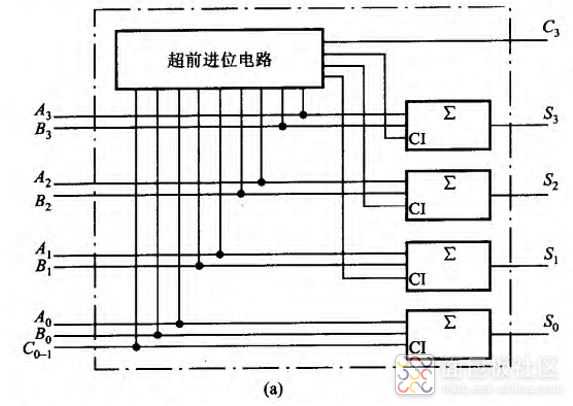

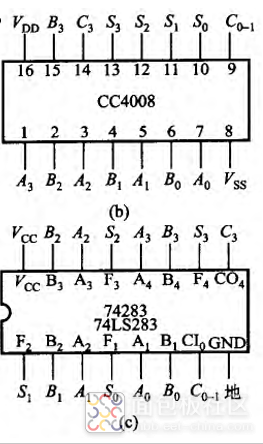

2、超前进位加法器(并行进位加法器)

显而易见,只要A3、A2、A1、A0 、B3、B2、B1、B0和C0-1给出之后,便可按上述表达式直接确定C3、C2、C1、C0。因此如果用门电路实现上述逻辑关系,并将结果送到相应全加器的进位输入端,就会极大地提高加法运算速度,因为高位的全加运算再也不需等待了。4位超前进位加法器就是由四个全加器和相应的进位逻辑电路组成的。

图(a)是4位超前进位加法器的逻辑电路结构示意图。图(b)、(c)是相应的CMOS与TTL集成电路的型号与引脚图。

编码器:

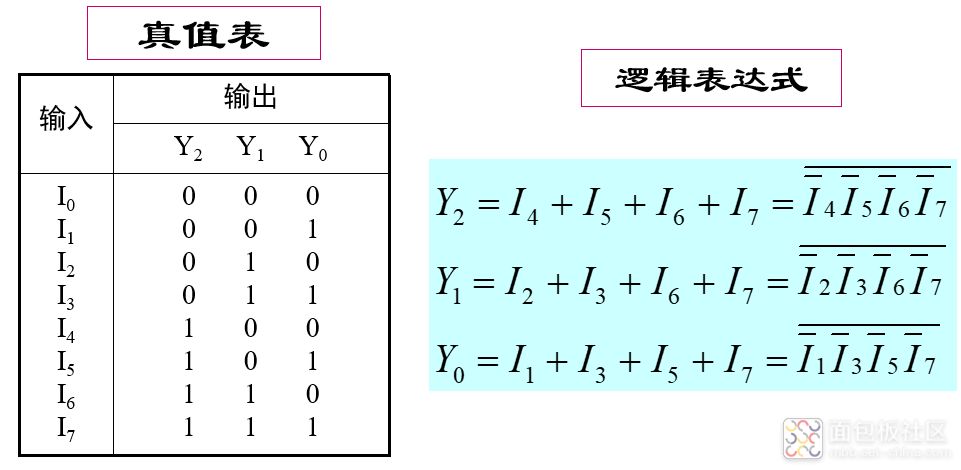

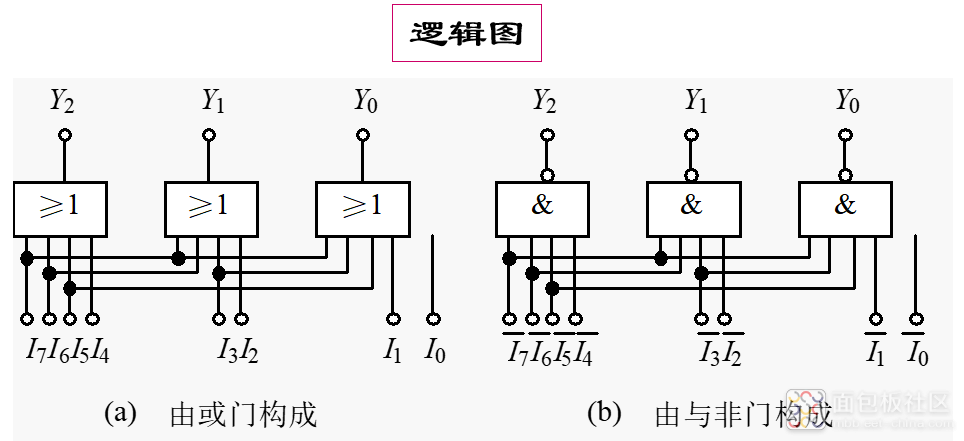

1、二进制编码器

输入是八个需要进行编码的信号用I0~I7表示,输出是用来进行编码的3位二进制代码,用Y0、Y1 、Y2表示。该编码器在任何时刻,只能对一个输入信号进行编码,即不允许有两个和两个以上输入信号同时存在,也就是I0、I1、…I7是一组互相排斥的变量。

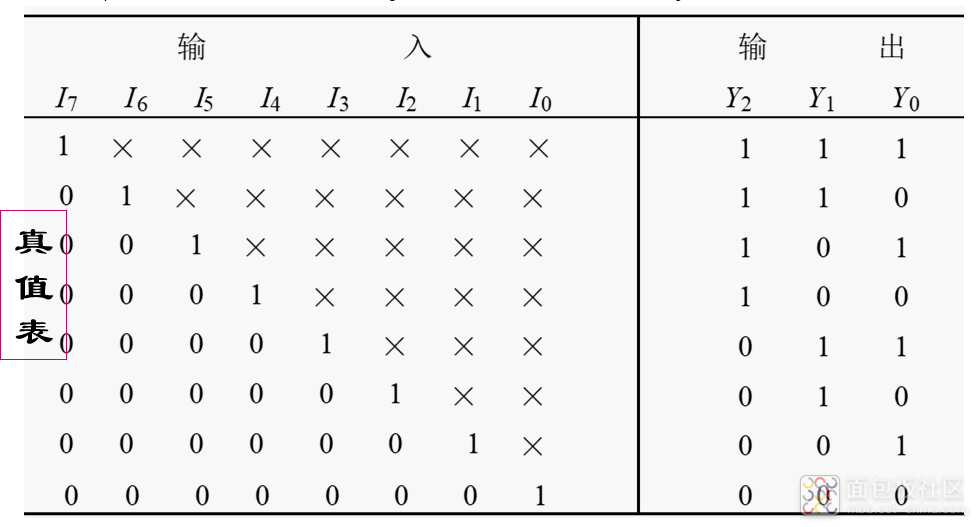

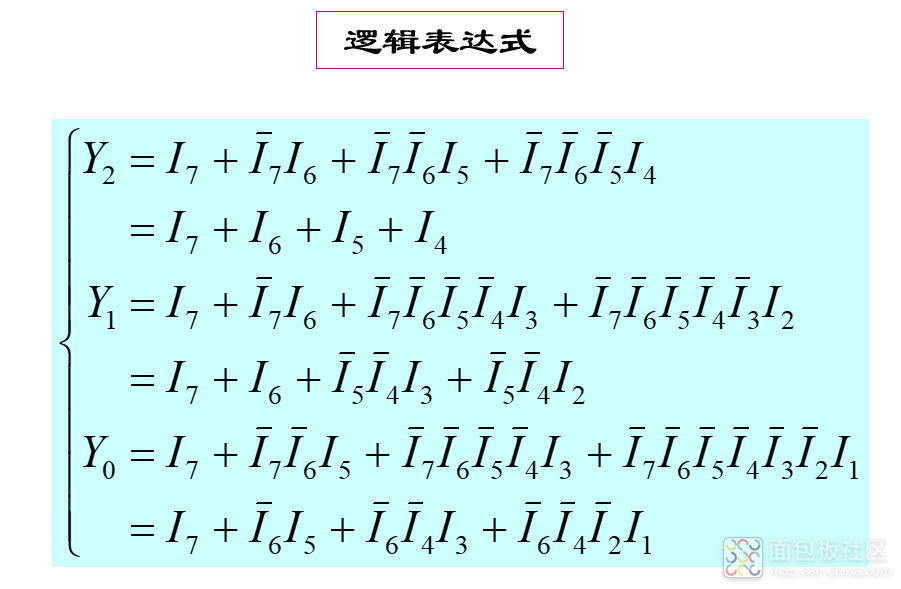

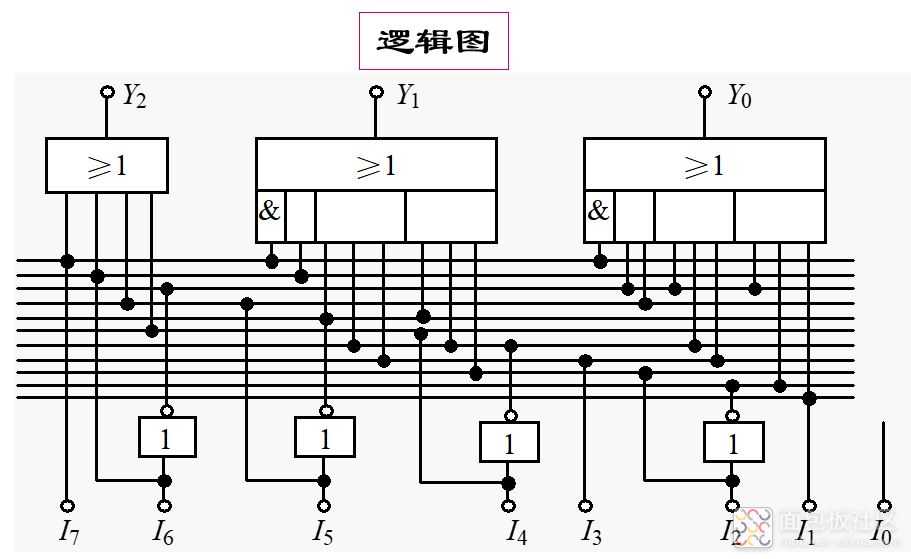

2、3位二进制优先编码器

在优先编码器中允许几个信号同时输入,但是电路只对其中优先级别最高的进行编码,不理睬级别低的信号。设I7的优先级别最高,I6次之,依此类推,I0最低。

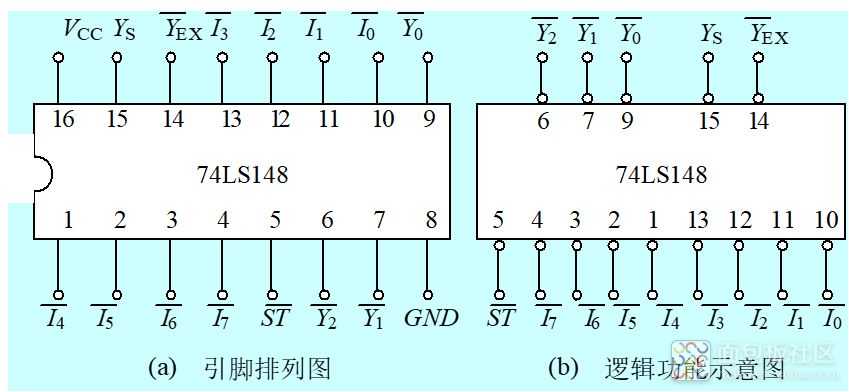

3、集成3位二进制优先编码器

集成3位二进制优先编码器74LS148:

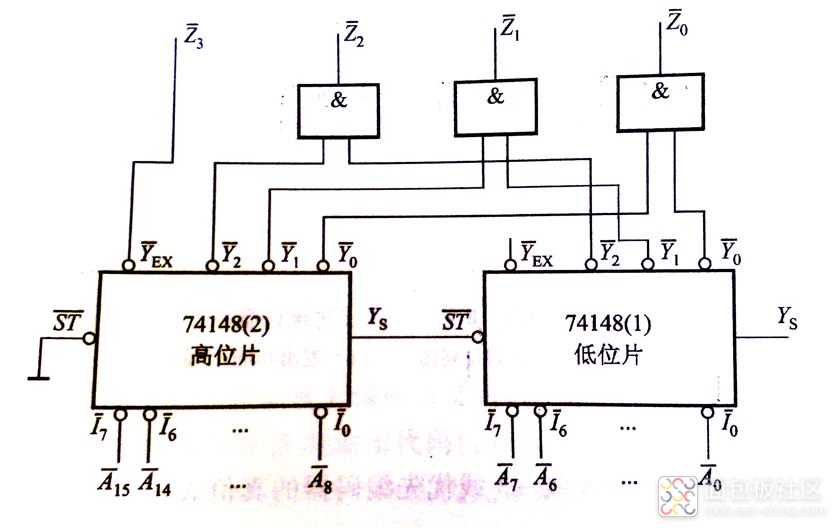

用两片8线-3线优先编码器构成的16线-4线优先编码器:

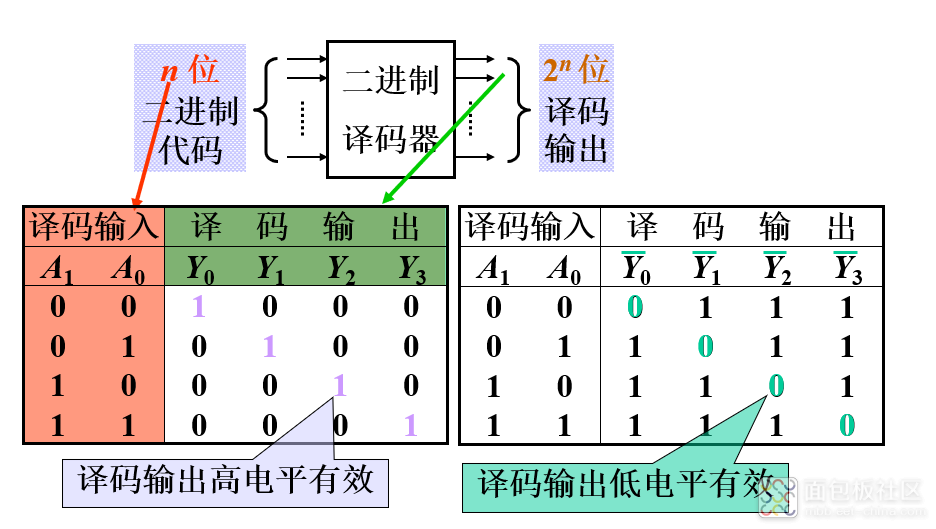

译码器:

一、二进制译码器

设二进制译码器的输入端为n个,则输出端为2的n次方个。

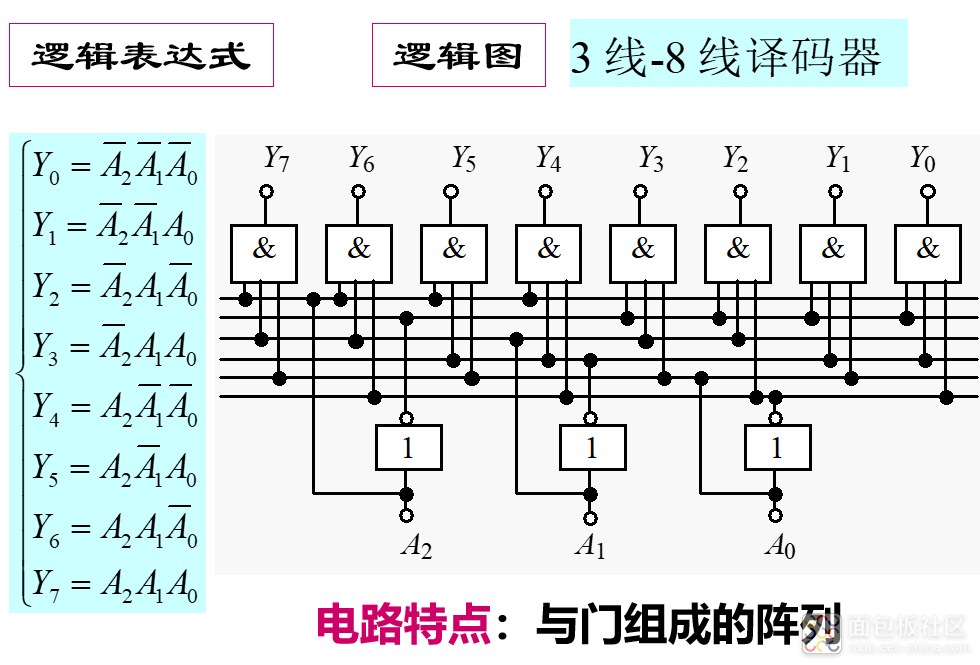

3位二进制译码器:输入:3位二进制代码;输出:8个信号

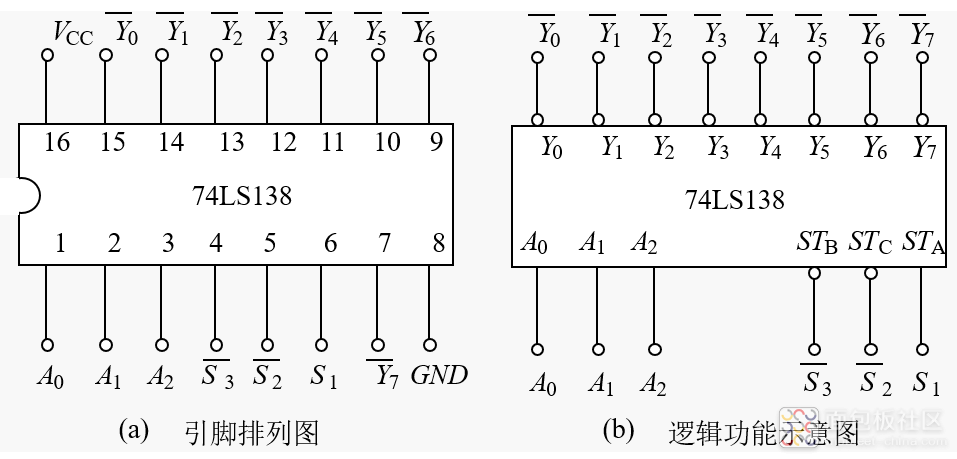

集成3线-8线译码器:

二进制译码器的级联:

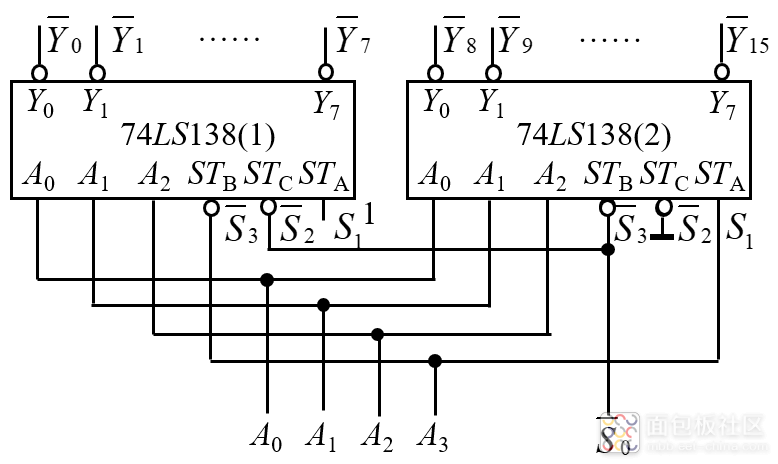

下图是把两片74LS138级联起来构成的4线-16线译码器:

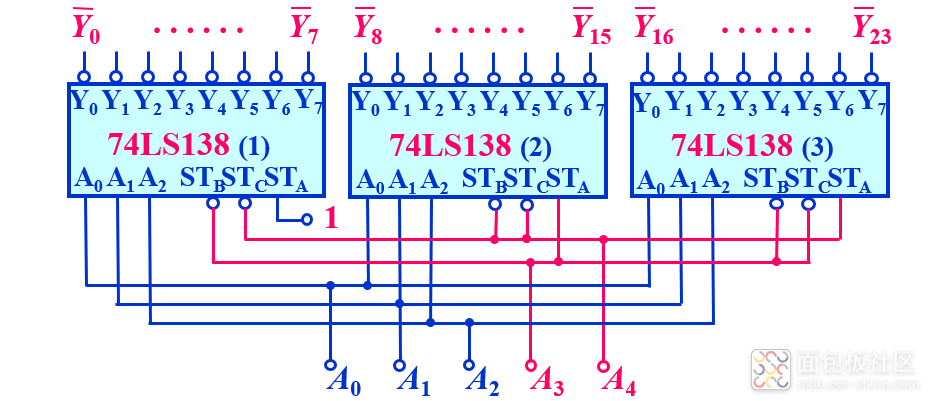

下图是把三片74LS138级联起来构成的5线-32线译码器。

/2

/2