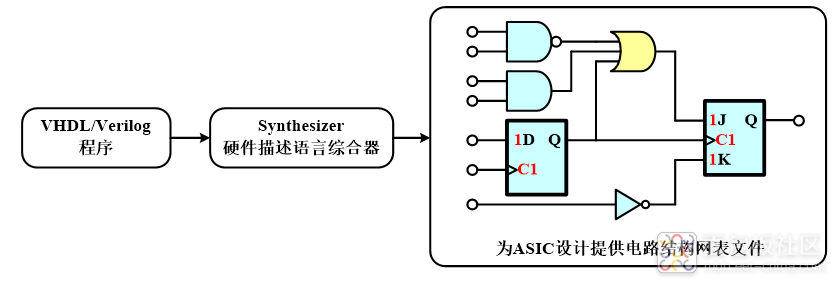

数字电路的设计由传统的“自下而上”(由底层电路电子系统)的设计方法,改变为以EDA工具为设计平台的“自上而下” (由电子系统底层硬件电路)的设计方式。

将电子系统的高层行为描述转换到低层硬件描述和确定的物理实现,使设计人员无须直接面对低层电路,不必了解具体的逻辑器件。

硬件描述语言(Hardware Description Language)是一种用于设计硬件电子系统的计算机语言,用软件编程的方式在EDA工具中建立电路模型。

VHDL——Very High Speed Integrated Circuit HDL;Verilog HDL——Verilog Hardware Description Language

VHDL语言基础:

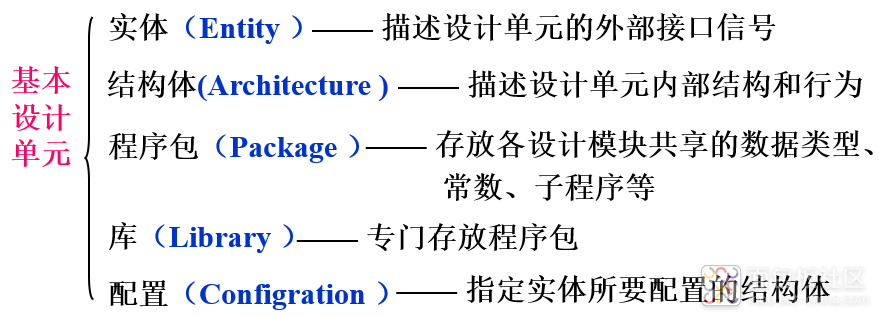

VHDL的主要构件:

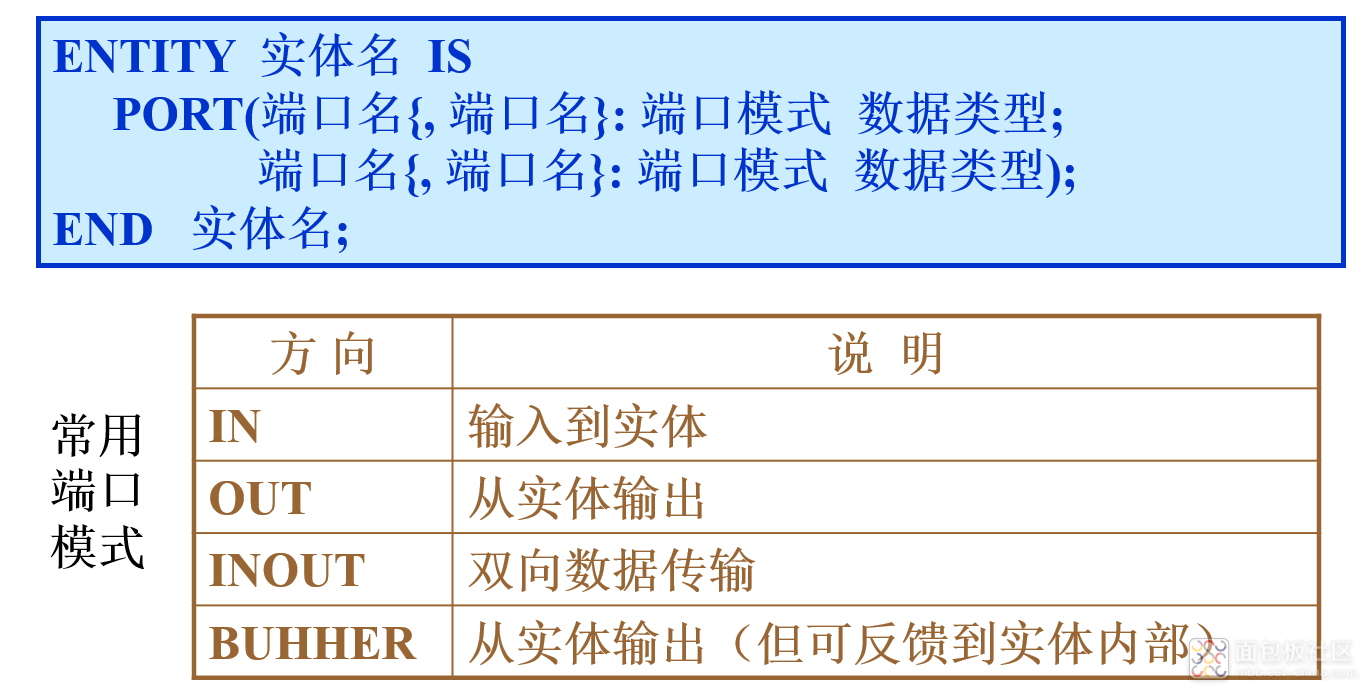

1. 实体

功能:实现设计单元的端口说明。

语法结构:

例:2 输入与门的实体说明

ENTITY and2 IS

PORT(a, b: IN STD_LOGIC;

y: OUT STD_LOGIC );

END and2;

设计单元端口结果:

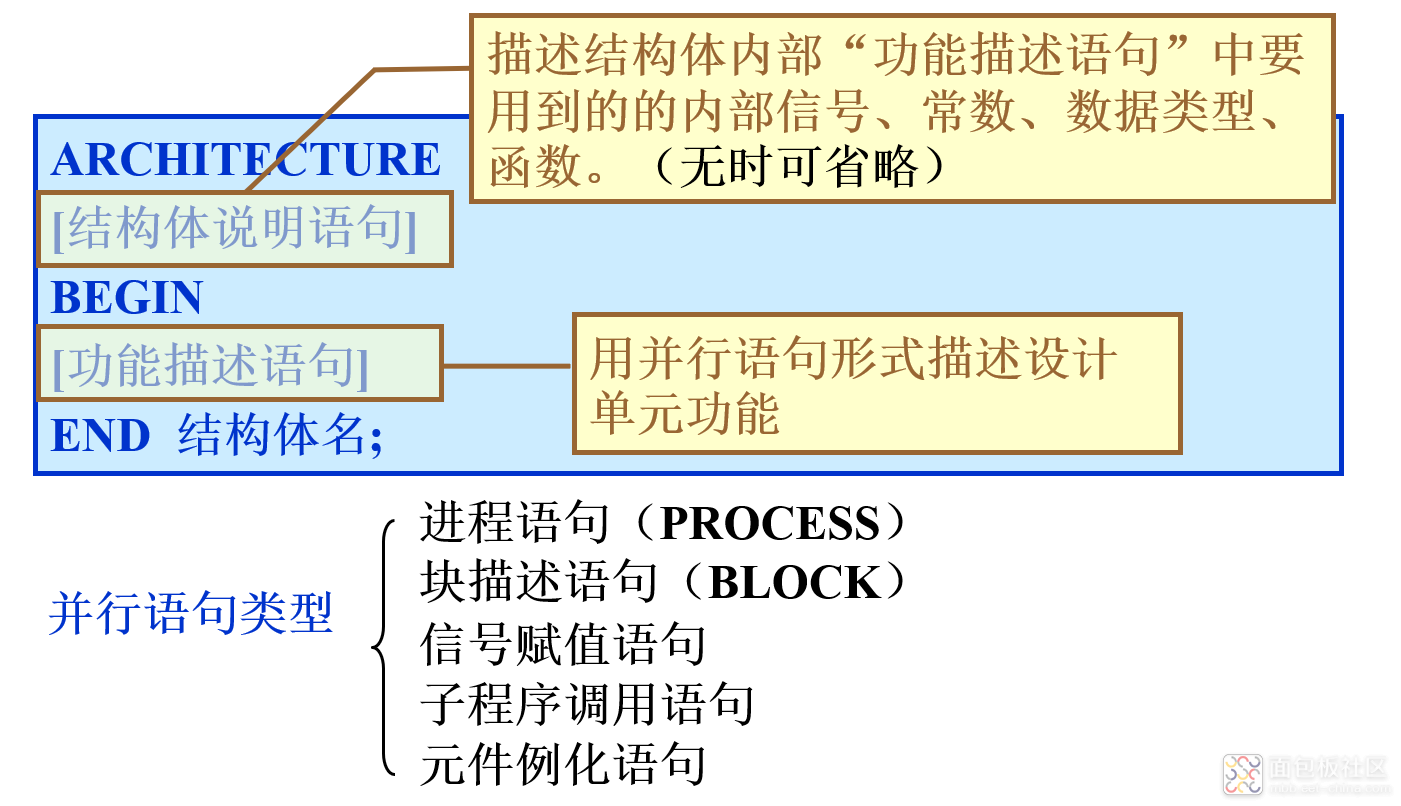

2. 结构体

功能:描述设计单元内部结构和行为,建立输入输出关系。

语法结构:

3. 库、程序包和配置

(1) 库

功能:存储和放置设计单元(元件、程序包等)。

VHDL库:

IEEE库:常用资源库,含IEEE认可和某些公司提供的如:STD_LOGIC_1164 程序包

STD库:VHDL标准库,存放:STANDARD的程序集合,集合定义了多种常用的数据类型

ASIC库:资源库,存放:和各种逻辑门一一对应的实体

WORK库:当前作业库,存放:当前设计项目生成的全部文件目录

用户自定义库:资源库,存放:用户自己创建定义的非标准程序包集合和实体。

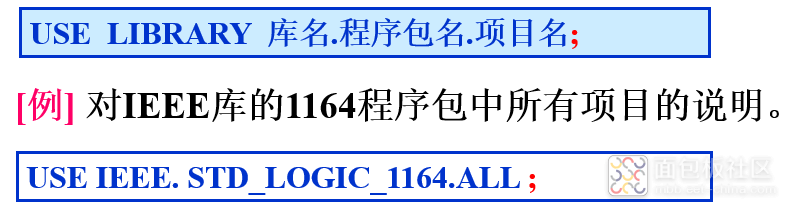

库说明语句格式:

LIBRARY 库名;

(2) 程序包

功能:存放各设计模块共享的数据类型、常数、子程序等。

语法格式:

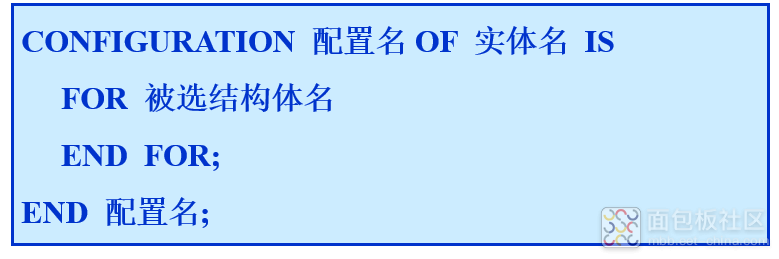

(3) 配置

功能:为实体指定所要配置的结构体

语法格式:

例:

ENTITY equ2 IS

PORT(a,b: IN STD_LOGIC_VECTOR(1 DOWNTO 0);

equ: OUT STD_LOGIC );

END equ2;

ARCHITECTURE equation OF equ2 IS --结构体一

……

END equation ;

ARCHITECTURE con_behave OF equ2 IS --结构体二

……

END con_behave ;

ARCHITECTURE seq_behave OF equ2 IS --结构体三

……

END seq_behave ;

实体equ2拥有三个结构体: equation、con_behave、seq_behave,可以用配置语句选择与实体对应的结构体。

如选用结构体con_behave,可用以下语句实现:

CONFIGURATION aequb OF equ2 IS

FOR con_behave

END FOR ;

END CONFIGURATION;

4. VHDL的数据对象和数据类型:

1. VHDL数据对象

(1)常量

常量:不变的量,定义时进行赋值,在整个程序中保持不变。

语法格式:CONSTANT 常量名:数据类型:=表达式;

(2)变量

语法格式:VARIABLE 变量名:数据类型[:=表达式];

(3)信号

信号:定义电路中的连线和元件的端口的数据对象。

语法格式:SIGNAL 信号名:数据类型;

2、VHDL数据类型

(1)整数数据类型(INTEGER)

取值范围:-2147483547~ 2147483546

(2)实数数据类型(REAL)

取值范围:-1.0E38~ 1.0E38

3)位数据类型(BIT)

属于枚举数据类型,取值为‘1’和‘0’。

(4)位矢量数据类型(BIT_VECTOR)

用双引号括起来的一组位数据,如“10011”,通常用来表示数据总线。

(5)布尔数据类型(BOOLEAN)

属于枚举数据类型,取值为‘TRUE’和‘FALSE’。常用来表示关系运算和关系运算结果。

(6)字符数据类型(CHARACTER)

ASCII码的128个字符,书写时用单引号,区分大小写,如‘a’、‘A’等。

(7)字符串数据类型(STRING)

双引号括起来的一串字符,如“abgh”。

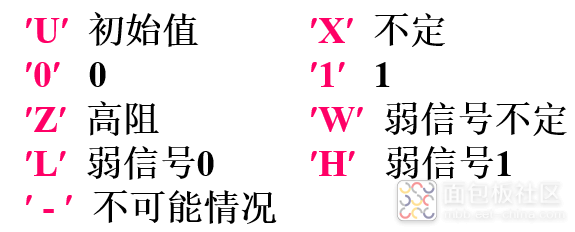

(8)STD_LOGIC数据类型

属于枚举数据类型,取值有以下九种:

(9)STD_LOGIC_VECTOR数据类型

用双引号括起来的一组STD_LOGIC数据,如“101011”,通常用来表示数据总线。

5. VHDL的操作符和表达式

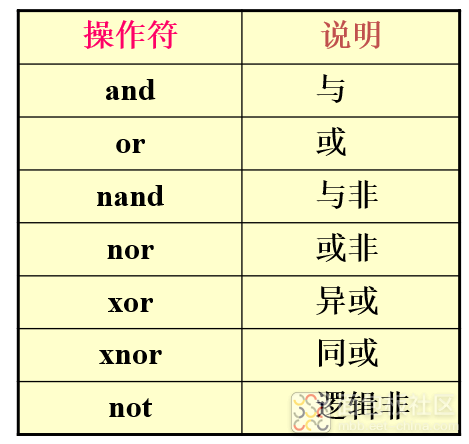

逻辑操作符和逻辑表达式:

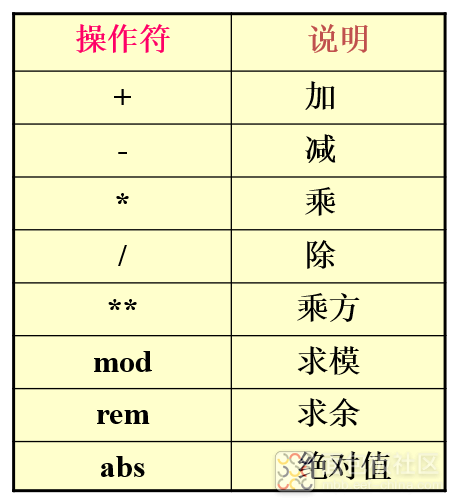

算术操作符和算术表达式:

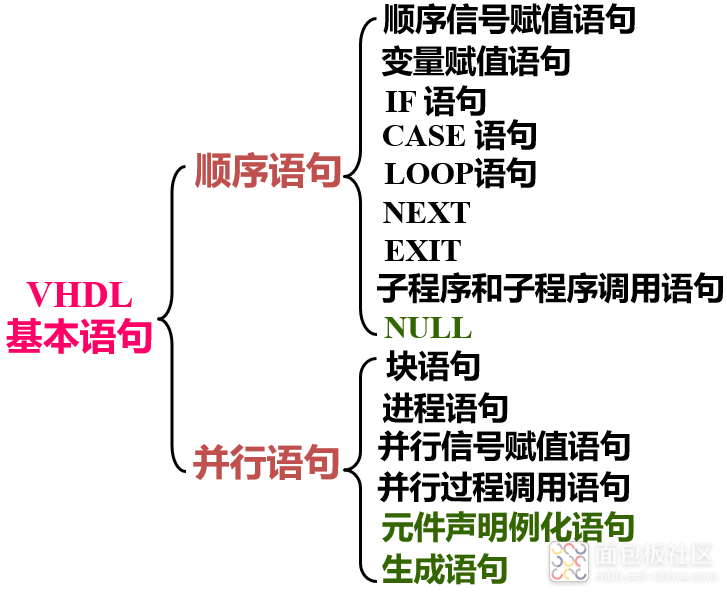

6. VHDL基本语句

顺序描述语句:执行顺序与书写顺序一致,只用于进程和子程序中。

(1)顺序信号赋值语句

格式: 目标信号<=表达式;

(2)变量赋值语句

格式: 目的变量:=表达式;

(3)IF语句(条件控制语句)

格式一:

IF 条件表达式 THEN

顺序语句;

END IF;

格式二:

IF 条件表达式 THEN

顺序语句;

ELSE

顺序语句;

END IF;

(4)CASE语句

语法格式:

CASE 表达式 IS

WHEN 选择值=>顺序语句;

WHEN 选择值=>顺序语句;

…

[WHEN OTHERS=>顺序语句;]

END CASE;

“选择值”的具体表示形式有以下四种:

WHEN 值=>顺序语句;

WHEN 值|值|…|值=>顺序语句;

WHEN 值 TO 值=>顺序语句;

WHEN OTHERS=>顺序语句;

例:用CASE语句设计“4选1”数据选择器的程序片段

SIGNAL s:STD_LOGIC_VECTOR (1 DOWNTO 0);

…

CASE s IS

WHEN 00=> z<=a;

WHEN 01=> z<=b;

WHEN 10=> z<=c;

WHEN 11=> z<=d;

WHEN OTHERS=> z<=X;

END CASE;

(5)LOOP语句

无条件LOOP语句语法格式:

[LOOP标号:]LOOP

顺序语句;

END LOOP [LOOP标号];

FOR…LOOP语句语法格式:

[LOOP标号:] FOR 循环变量 IN 循环次数范围 LOOP

顺序语句;

END LOOP [LOOP标号] ;

WHILE…LOOP语句语法格式:

[LOOP标号:] WHILE 条件表达式 LOOP

顺序语句;

END LOOP [LOOP标号];

例:WHILE…LOOP应用举例

abcd: WHILE (i<10) LOOP

sun:=i+sum;

i=i+1;

END LOOP abcd;

(6)NEXT语句

格式:NEXT [WHEN 条件];

例如:NEXT语句举例

loop2:LOOP

b:=b+1 ;

NEXT WHEN b<10;

…

END LOOP loop2;

(7)EXIT语句

格式:EXIT [标号][WHEN 条件];

例:EXIT语句在数值比较程序设计中的应用

FOR i IN 1 DOWNTO 0 LOOP

IF (a(i)=1 AND b(i)= 0 ) THEN

a_less_than_b<=false;

EXIT;

ELSIF (a(i)= 0 AND b(i)= 1 ) THEN

a_less_than_b<=true;

EXIT;

ELSE NULL;

END IF;

END LOOP;

(8)子程序和子程序调用语句

VHDL子程序:过程(PROCEDURE)和函数(FOUNCTION)

函数定义语句的语法格式:

FOUNCTION <函数名>(参数表) RETURN <数据类型> IS

BEGIN

顺序语句;

RETURN [返回变量名];

END <函数名>;

函数调用语句的语法格式:

函数名(实际参数表);

/5

/5