锁相环路,简称PLL,作用:可以锁定相位,可以消除频率误差。

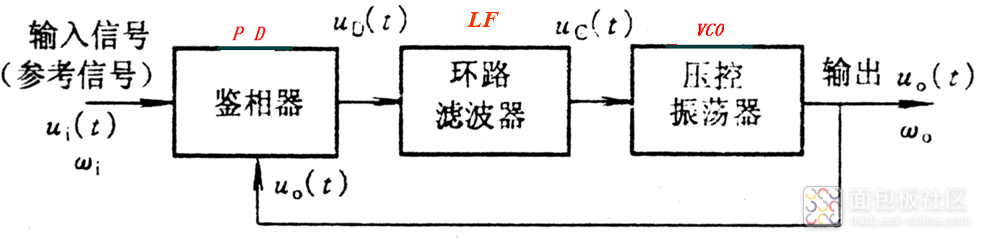

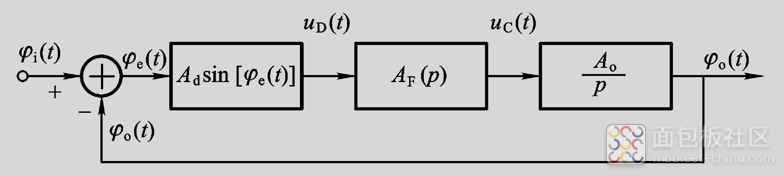

1、锁相环路基本组成

鉴相器(PD):用以比较ui、 uo相位,输出反映相位误差的电压uD(t)。

环路滤波器(LF): 用以滤除误差信号中的高频分量和噪声,提高系统稳定性。

压控振荡器(VCO):在uC(t)控制下输出相应频率 fo。

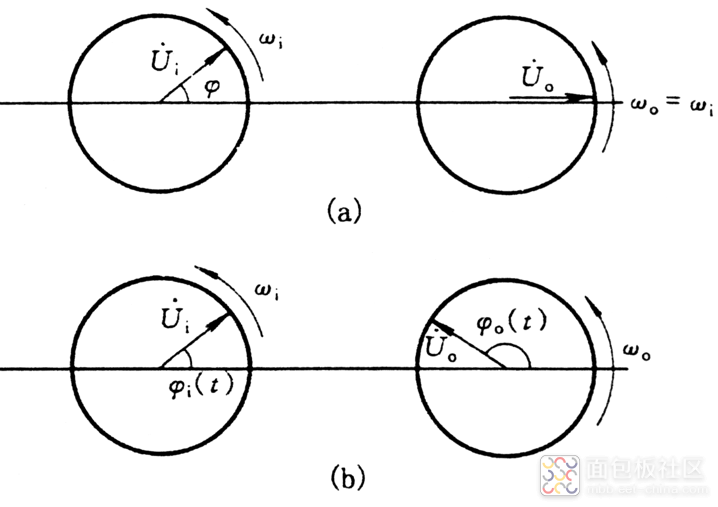

若两正弦信号频率相等,则二者之相位差恒定;反之,只要保持其相位差恒定,即可使两信号频率相等。

锁相环路的基本工作原理:

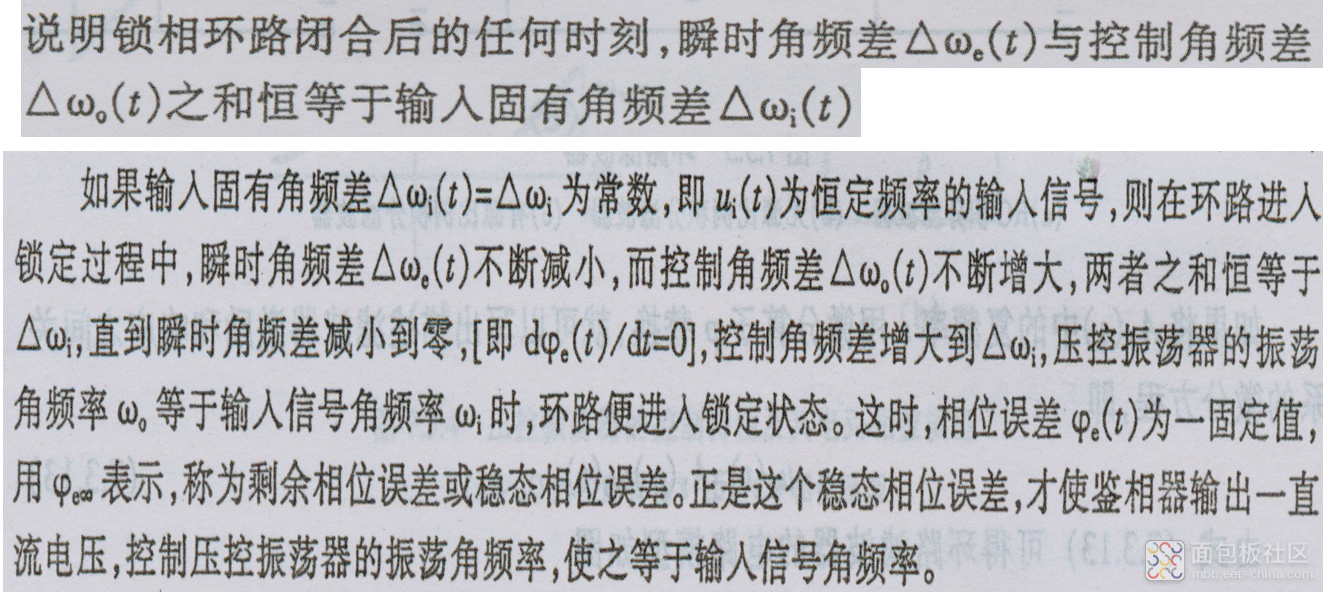

若wi ≠wo,则ui(t)和uo(t)之间产生相位变化 → uD(t) ,与瞬时误差相位成正比→uc(t),滤除了高频分量和噪声→ wo ,去接近wi ;最终使 wi = wo ,相位误差为常数,环路锁定,这时的相位误差称为剩余相位误差或稳态相位误差。

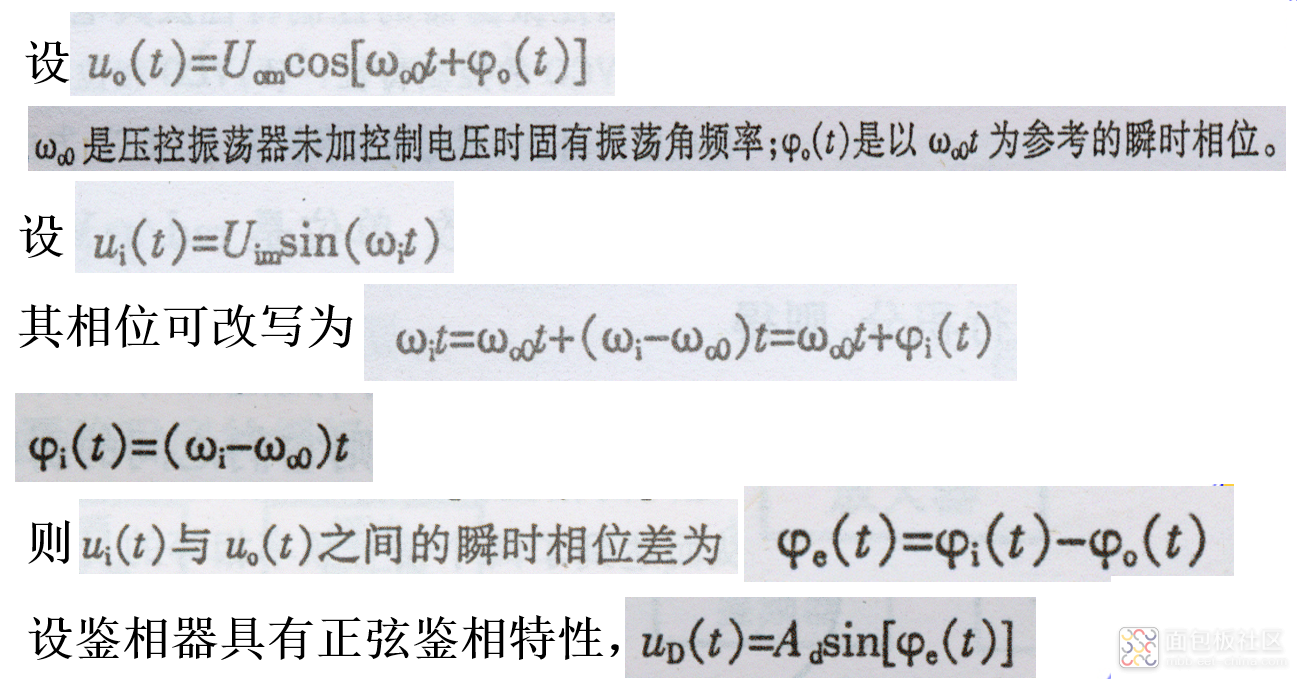

2、锁相环路的数学模型

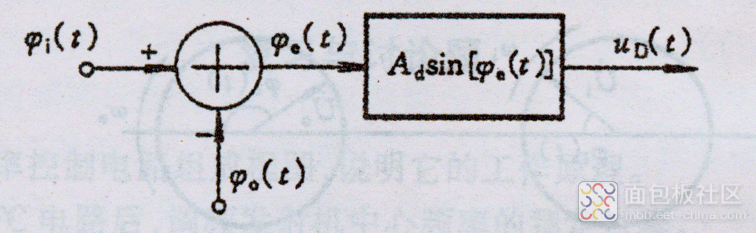

鉴相器的相位模型:

模型为:

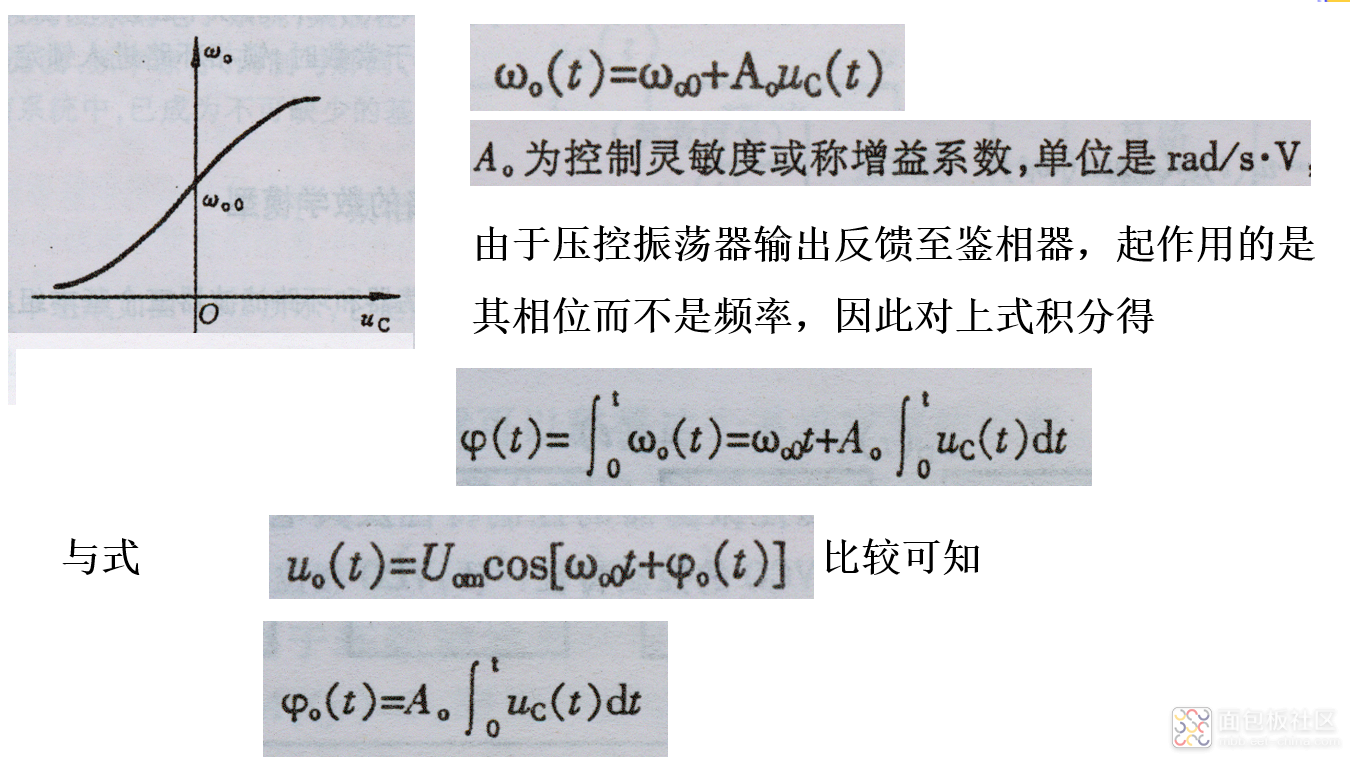

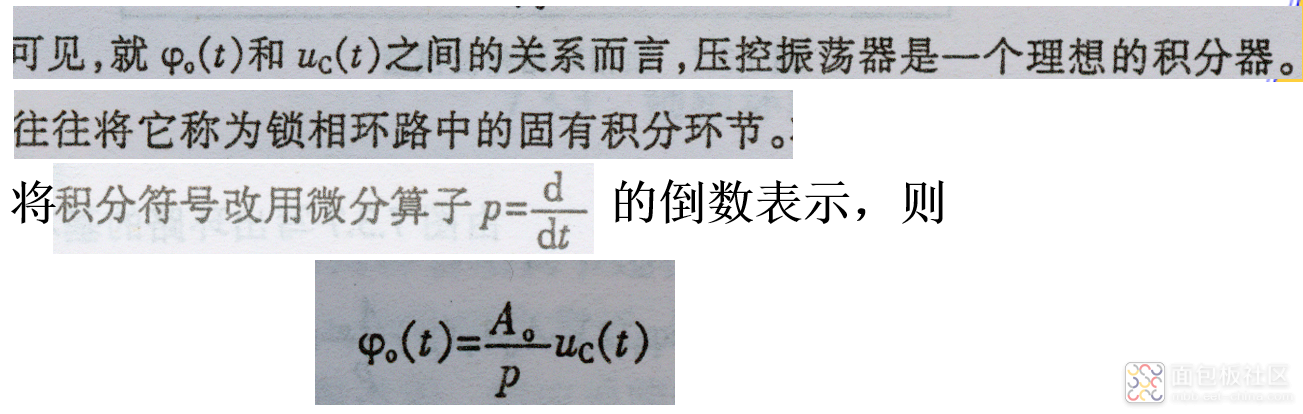

压控振荡器的相位模型:

模型为:

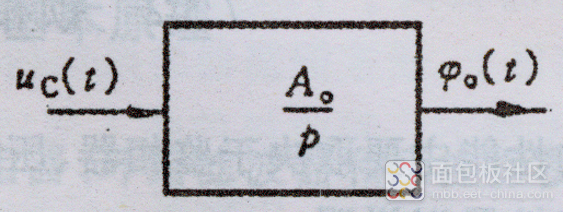

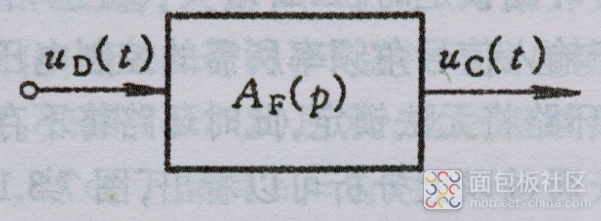

环路滤波器的电路模型:

模型为:

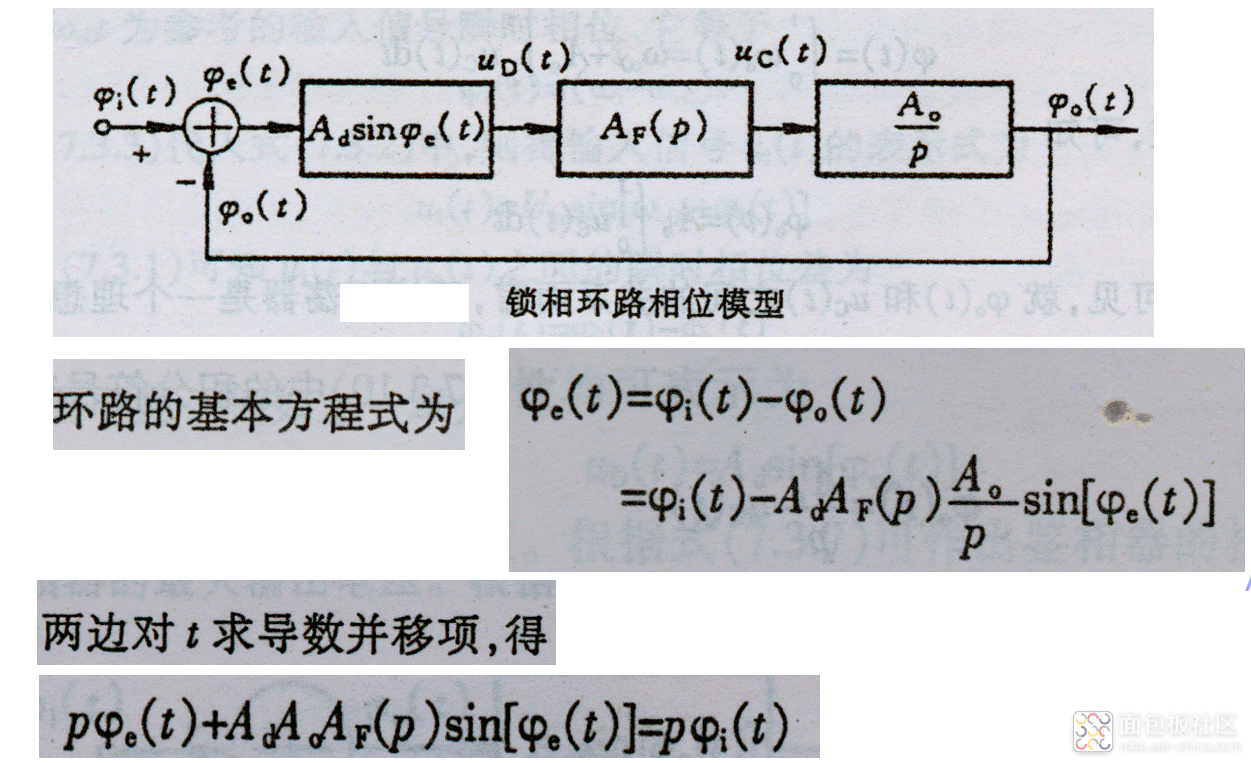

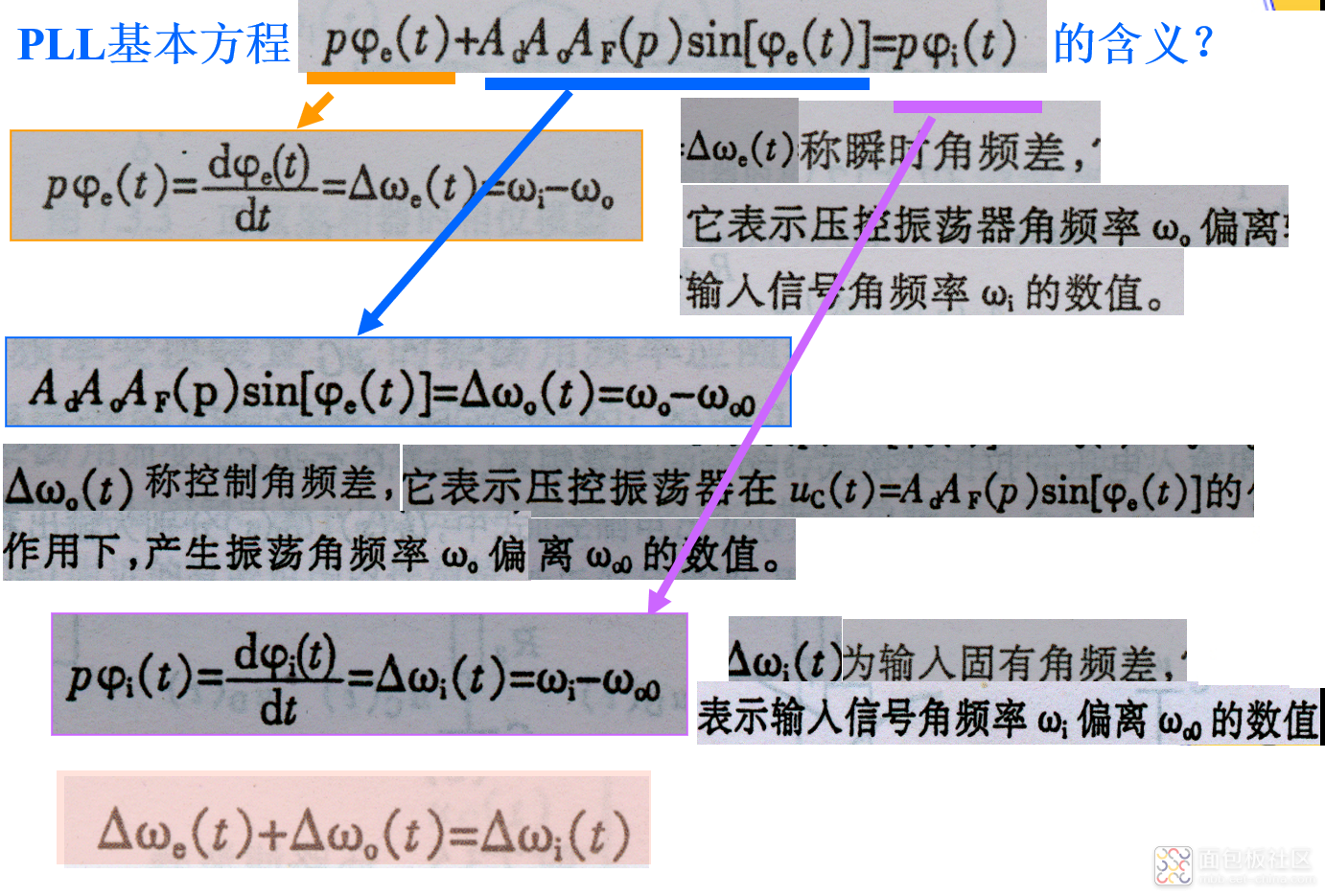

PLL的相位模型和基本方程:

上式是一个非线性微分方程,它完整地描述了环路的控制过程。

锁相环路(PLL)是一个传递相位的闭环系统,只要研究它的相位数学模型或它的微分方程,即可获得该系统的完整性能。

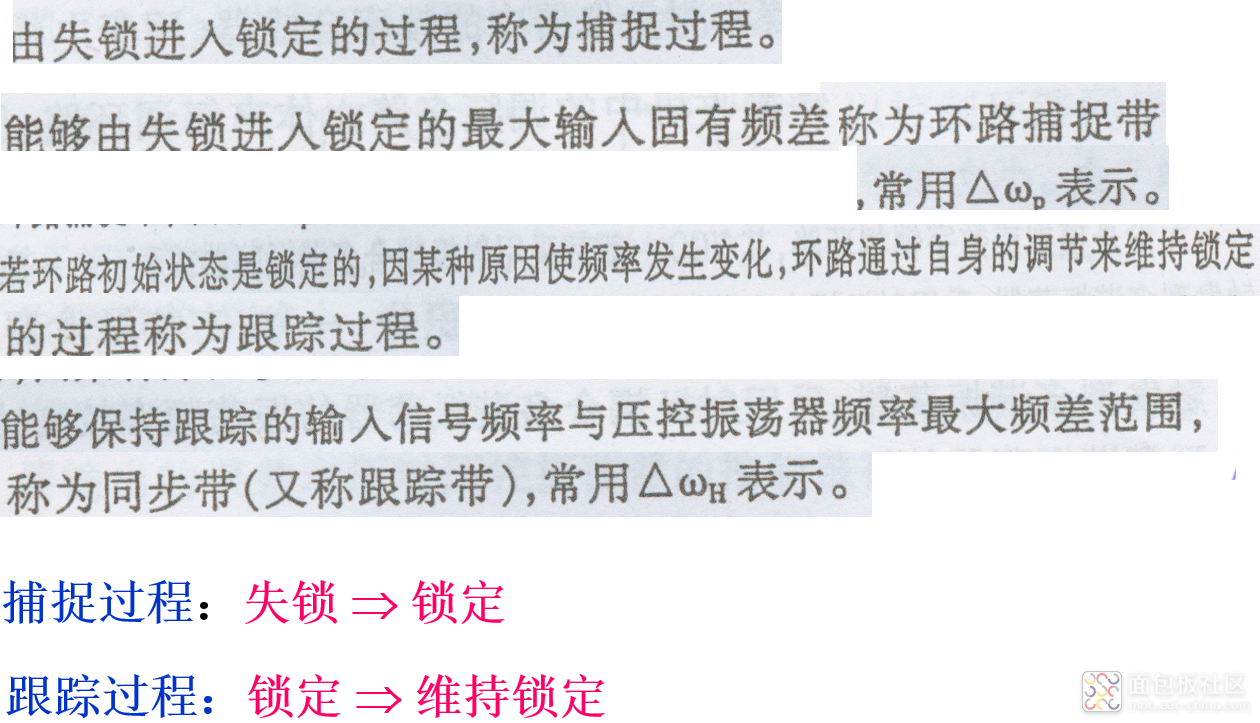

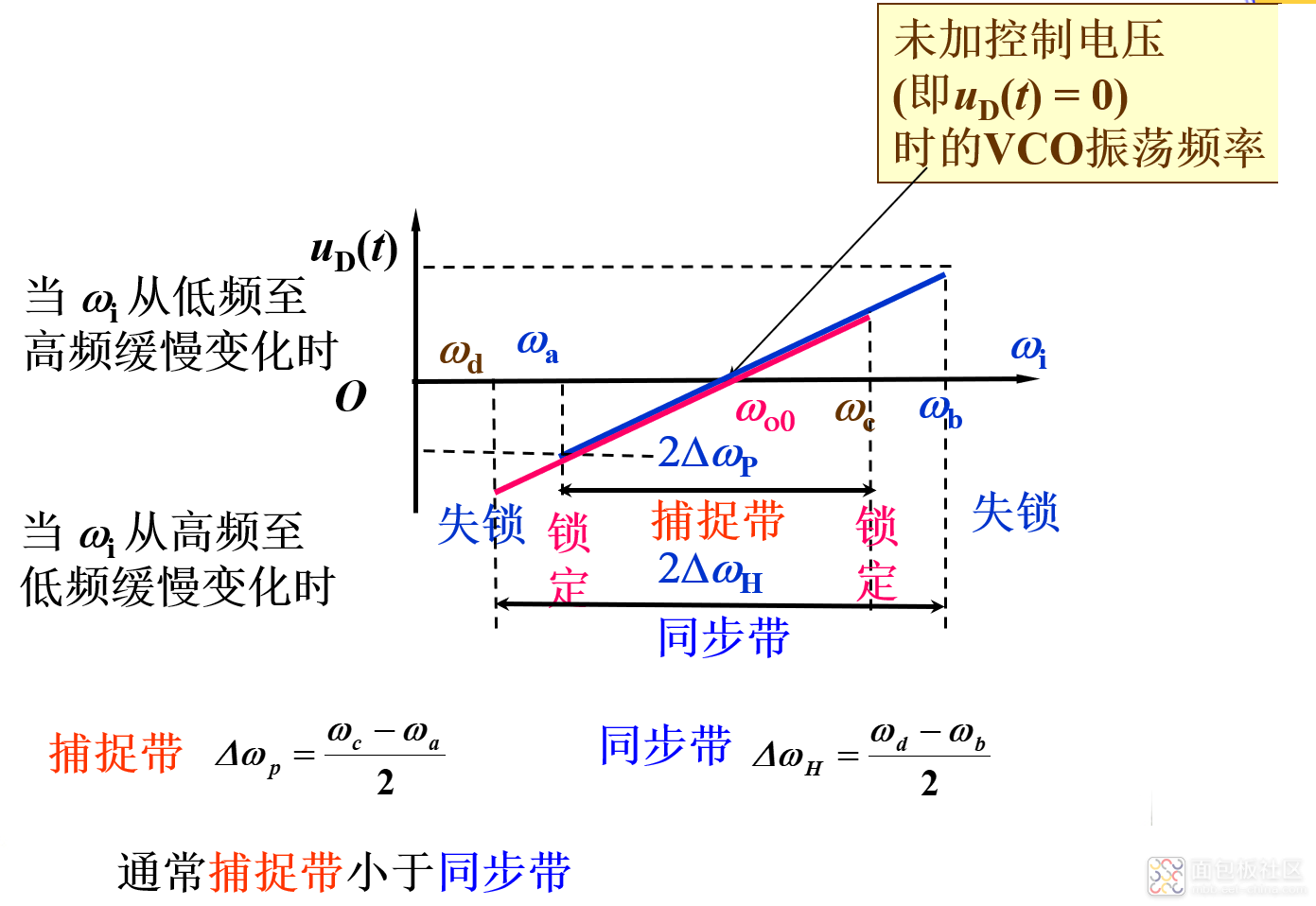

3、锁相环路的捕捉与跟踪

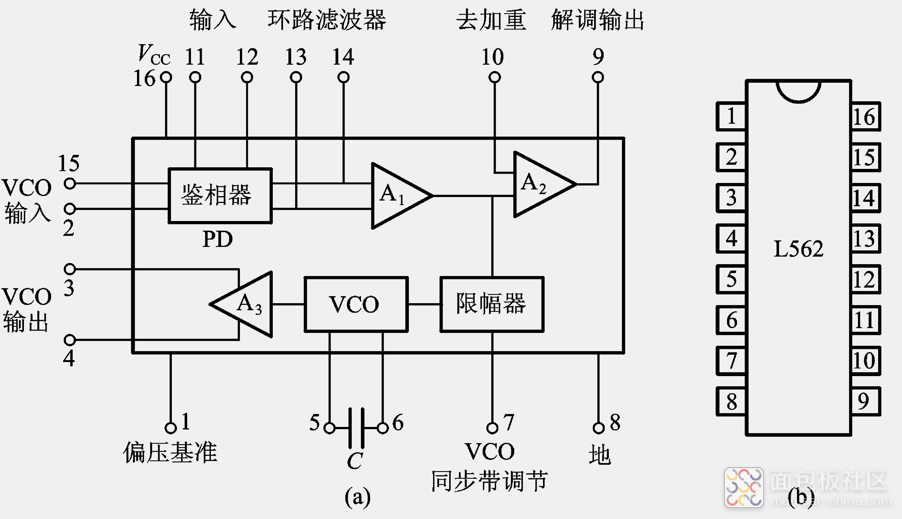

4、 集成锁相环路

通用型单片集成锁相环路L562简介:

为多功能单片集成PLL。内部除有PD、VCO外,还有三个放大器和一个限幅器。工作频率可达30MHz。

鉴相器(PD)采用双差分对模拟相乘器电路,压控振荡器(VCO)采用射极耦合多谐振荡器电路。

限幅器用于限制锁相环路的直流增益,以控制环路同步带的大小。

只需单电源供电,一般采用18V电源,最大电流14mA。输入信号电压最大值为3V。

L562内部结构与外引脚排列:

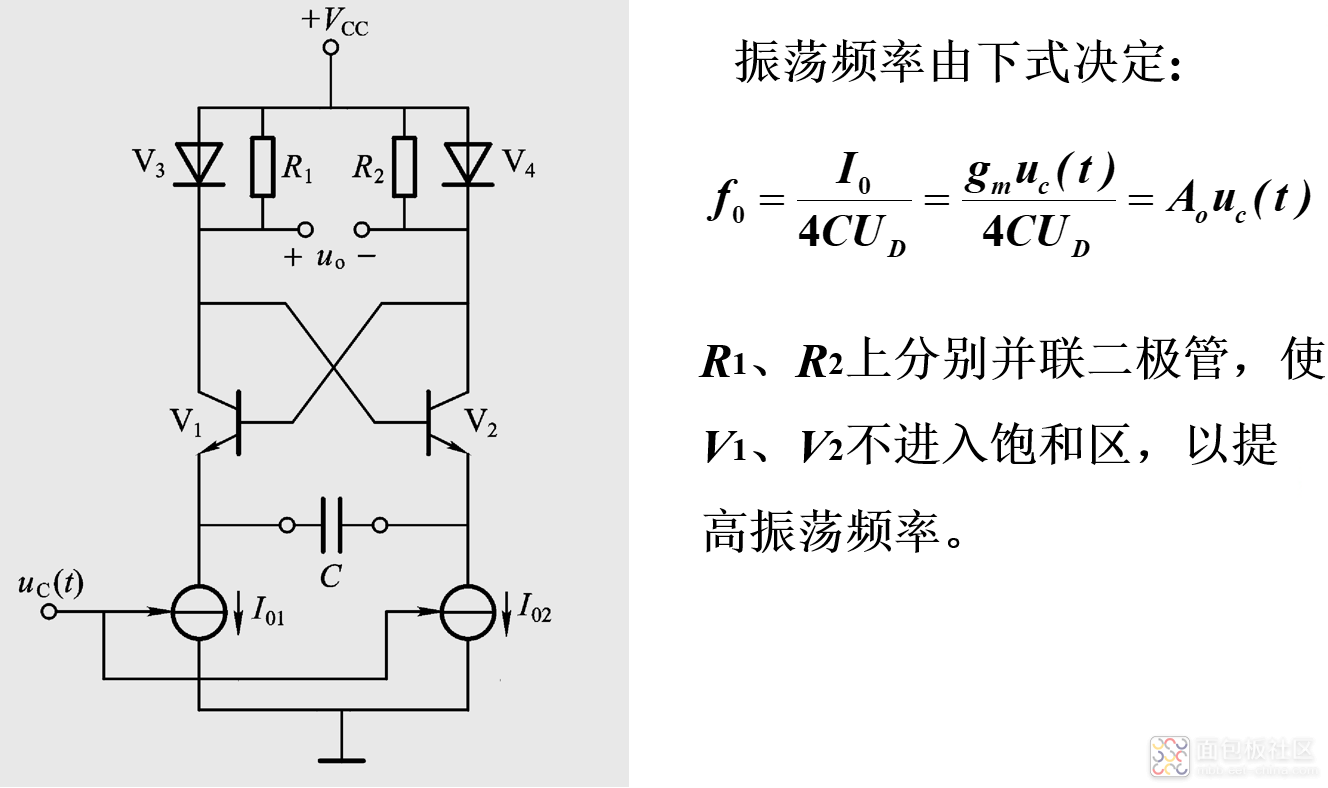

L562内部的射极耦合多谐VCO:

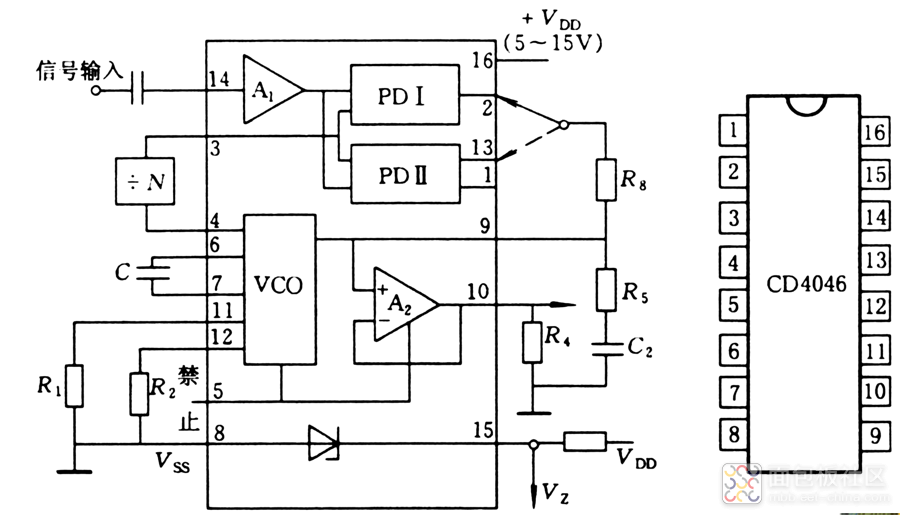

CMOS锁相环路CD4046简介:

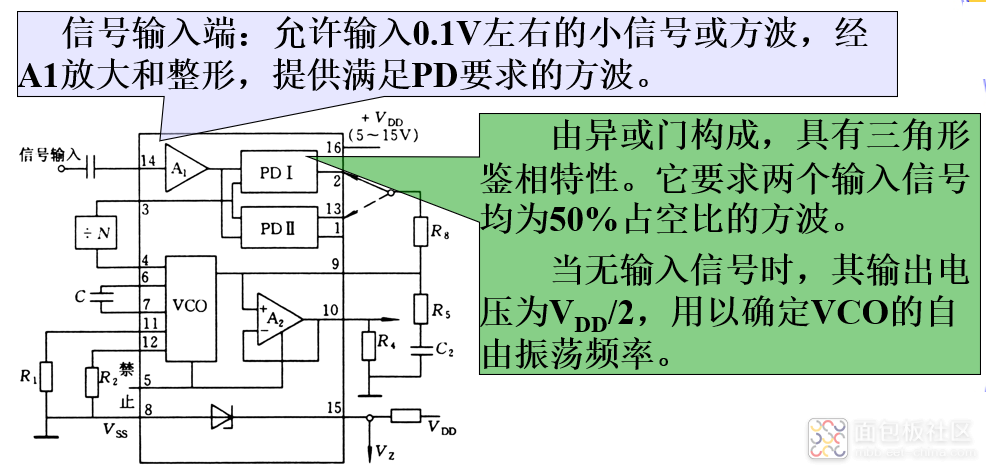

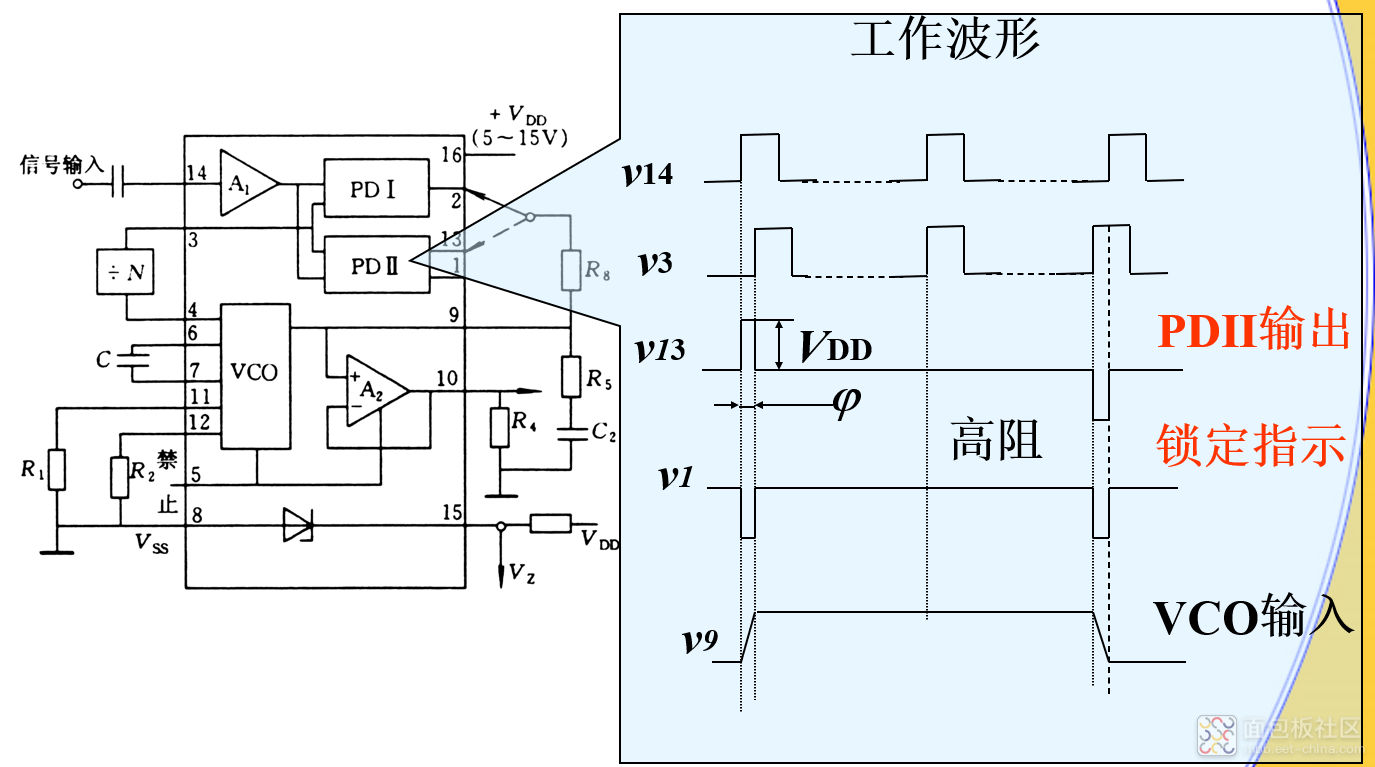

为数字PLL。内有两个PD、VCO、缓冲放大器、输入信号放大与整形电路、内部稳压器等。具有电源电压范围宽(5~15V)、功耗低、输入阻抗高 等优点。工作频率0~1MHz。内部VCO产生50%占空比的方波。输出电平可与TTL电平或CMOS电平兼容。

/5

/5