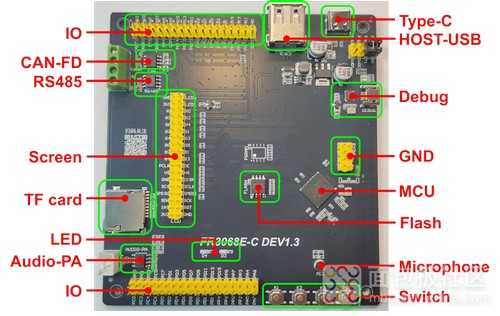

一、硬件基础

富芮坤 FR3068x-C 是一款功能较为强大的芯片,具备一定的处理能力和丰富的接口资源。其内置的高性能处理器为音频解码和播放提供了基础支持,丰富的 GPIO 接口方便连接各类外部设备,如音频放大器、存储设备等,为音乐播放功能的实现搭建了良好的硬件平台。收到的主要部件面、

主控 MCU:

- FR3068E-C 芯片架构属于双核架构,包括一颗独立的蓝牙核做蓝牙通讯,以及另外一颗主核MCU,双核之间通过串口做 HCI 通讯,蓝牙核一般不对外开放

- 内置 128KB CRAM+512KB SRAM,2MB flash (根据芯片型号有不同大小配置)

- 需外挂 24 MHz 晶体时钟,系统主频最高可倍频至 156 MHz

- 工作温度:工业级 -40~105 ℃

- 有 57 个可编程 IO(不同型号/封装会有所不同)

- 支持 2 路 CAN 总线,支持 CAN FD

- 支持丰富的外设总线如 SPI / UART / USB等

- 支持双模蓝牙 BLE + BT / EDR

蓝牙

FR306x-C 符合蓝牙 V5.3 标准,支持 BR 1Mbps GFSK, EDR 2Mbps π/4-DQPSK, 3Mbps 8DPSK; BLE1M/2Mbps GFSK, 125K/500K 多种模式,支持单独打开和关闭不同的模式,支持蓝牙多主多从多连接。

硬件资源

- 2x PDM 数字音频接口

- 2x 32位宽的I2S 接口

- 3x I2C

- 6x UART 带流控

- 2x SPI 主接口,支持 QSPI,OSPI

- 2x SPI 从接口,一路是单线的,一路支持四线

- USB 2.0 OTG

- 最多支持 2 x 16 channel PWM,支持输入捕获,可以做PWM DAC输出

- 最多支持 9 通道12bit SAR-ADC,支持普通模式、队列模式;

- 最多支持 57 个可配置 GPIO

- CAN FD 控制器

- 符合 CAN 总线协议 V 2.0 part A, B ,符合 ISO 11898-1

- Display显示接口 8080/6080/RGB/SPI

- 6x 32bit timer

- 2x DMA

- SDIO3.0

- 硬件加密单元 AES-128, AES-192, AES-256

- 支持 Floating point unit (FPU)

- 真随机数发生器 TRNG

- 像素编码转换器 YUV2RGB

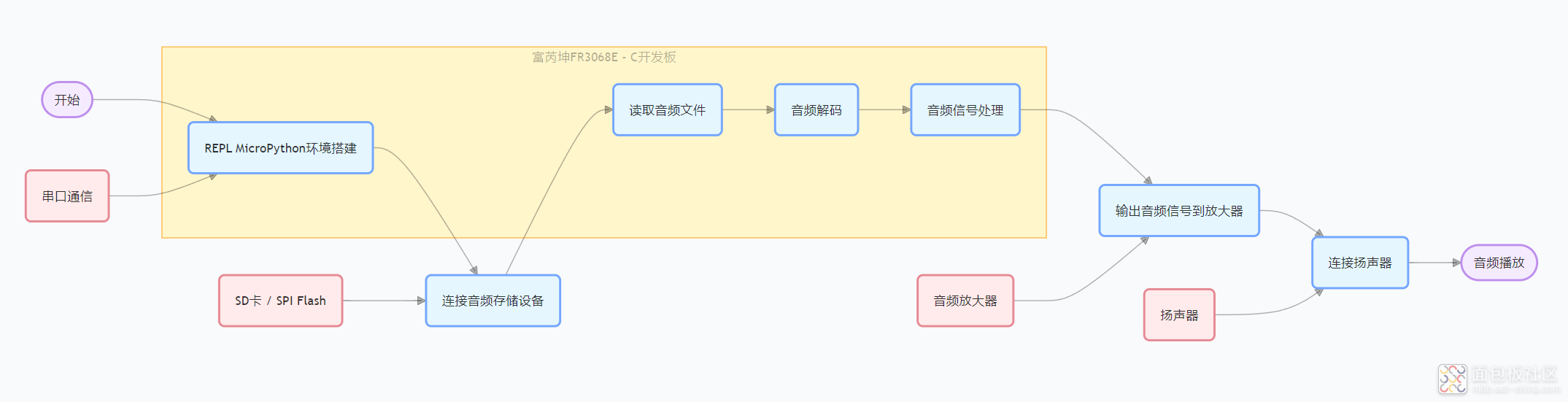

二、软件实现

大概的流程实现框图:

通过 B站的REPL MicroPython视频介绍与官方的SDK 来实现本地音乐播放,大大降低了开发门槛。

注意烧录的问题:

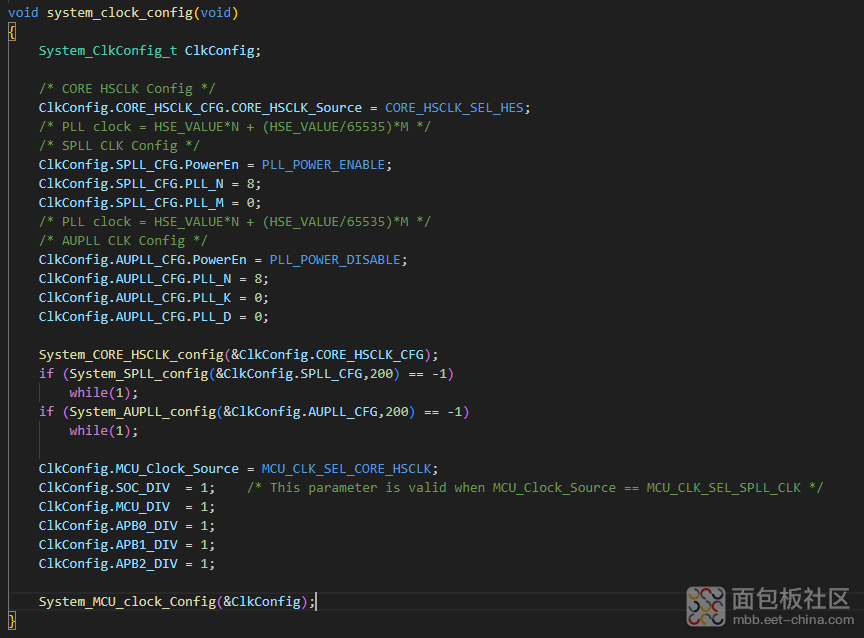

MicroPython 简洁的语法让开发者能够快速上手,利用其丰富的库函数开发前可以提前调整下时钟;

通过设置CORE_HSCLK(内核高速时钟)的时钟源为HSE(高速外部时钟源),以及对SPLL(系统锁相环)和AUPLL(音频锁相环)的配置,确定了系统的基本时钟频率。时钟就像是系统的 “心脏”,稳定且合适的时钟频率为整个芯片的稳定运行提供了基础,使得芯片内部的处理器、寄存器等组件能够按照预期的节奏进行工作。

时钟的调整可实现播放速度变化

1.变量定义

System_ClkConfig_t ClkConfig;定义了一个System_ClkConfig_t类型的结构体变量ClkConfig,该结构体用于存储系统时钟的各种配置参数。

2. 配置 CORE_HSCLK(高速时钟)

ClkConfig.CORE_HSCLK_CFG.CORE_HSCLK_Source = CORE_HSCLK_SEL_HSE;将CORE_HSCLK(内核高速时钟)的时钟源设置为HSE(高速外部时钟源)。

3. 配置 SPLL(系统锁相环)时钟

ClkConfig.SPLL_CFG.PowerEn = PLL_POWER_ENABLE;

ClkConfig.SPLL_CFG.PLL_N =8;

ClkConfig.SPLL_CFG.PLL_K =0;

- ClkConfig.SPLL_CFG.PowerEn = PLL_POWER_ENABLE;:使能系统锁相环(SPLL)的电源。

- ClkConfig.SPLL_CFG.PLL_N = 8;:设置 SPLL 的倍频因子N为 8。

- ClkConfig.SPLL_CFG.PLL_K = 0;:设置 SPLL 的分频因子K为 0 。通过公式PLL clock = HSE_VALUE*N + (HSE_VALUE/65535)*M(代码注释中有提及,不过代码中未设置M相关内容)来计算 SPLL 输出时钟频率。

4. 配置 AUPLL(音频锁相环)时钟(可以适当调整)

ClkConfig.AUPLL_CFG.PowerEn = PLL_POWER_DISABLE;

ClkConfig.AUPLL_CFG.PLL_N =8;

ClkConfig.AUPLL_CFG.PLL_K =0;

ClkConfig.AUPLL_CFG.FGEn =0;

- ClkConfig.AUPLL_CFG.PowerEn = PLL_POWER_DISABLE;:禁用音频锁相环(AUPLL)的电源。

- ClkConfig.AUPLL_CFG.PLL_N = 8;:设置 AUPLL 的倍频因子N为 8。

- ClkConfig.AUPLL_CFG.PLL_K = 0;:设置 AUPLL 的分频因子K为 0。

- ClkConfig.AUPLL_CFG.FGEn = 0;:禁用 AUPLL 的某个功能(根据代码上下文推测FGEn可能是功能使能相关的配置位 )。

5. 执行系统时钟配置函数

System_CORE_HSCLK_config(&ClkConfig.CORE_HSCLK_CFG);if(System_SPLL_config(&ClkConfig.SPLL_CFG,200)==-1)while(1);if(System_AUPLL_config(&ClkConfig.AUPLL_CFG,200)==-1)while(1);System_CORE_HSCLK_config(&ClkConfig.CORE_HSCLK_CFG);:根据前面设置的CORE_HSCLK配置参数来配置内核高速时钟。

- if (System_SPLL_config(&ClkConfig.SPLL_CFG,200) == -1):尝试配置系统锁相环 SPLL,如果配置函数返回 -1(表示配置失败),则进入死循环,阻止程序继续执行。

- if (System_AUPLL_config(&ClkConfig.AUPLL_CFG,200) == -1):尝试配置音频锁相环 AUPLL,如果配置函数返回 -1(表示配置失败),则进入死循环,阻止程序继续执行。

6. 配置 MCU 时钟源及相关分频参数

ClkConfig.MCU_Clock_Source = MCU_CLK_SEL_CORE_HSCLK;

ClkConfig.SOC_DIV =1;

ClkConfig.MCU_DIV =1;

ClkConfig.APB0_DIV =1;

ClkConfig.APB1_DIV =1;

ClkConfig.APB2_DIV =1;

- ClkConfig.MCU_Clock_Source = MCU_CLK_SEL_CORE_HSCLK;:将 MCU(微控制单元)的时钟源设置为CORE_HSCLK。

- 后面几条语句分别设置了不同总线上的分频因子(如SOC_DIV、MCU_DIV、APB0_DIV、APB1_DIV、APB2_DIV),这些分频因子用于调整不同总线的时钟频率,以满足不同外设的需求。

7. 最终配置 MCU 时钟(建议默认就好)

System_MCU_clock_Config(&ClkConfig);根据前面设置的 MCU 时钟源和分频参数,调用System_MCU_clock_Config函数来完成 MCU 时钟的最终配置。

总体而言,这段代码的作用是对芯片的系统时钟进行全面配置,包括选择时钟源、配置锁相环、设置 MCU 时钟源及相关分频参数,以确保芯片内部各模块能够在合适的时钟频率下稳定运行。

可以轻松实现文件读取、音频解码等功能。在实现过程中,首先要确保芯片与存储音乐文件的设备与PC正确连接,然后通过 MicroPython 编写代码来读取音乐文件,并进行相应的解码和音频输出设置。例如,使用相关的音频驱动库函数来初始化音频输出引脚,设置音频采样率、声道数等参数,以确保音频能够正常播放。

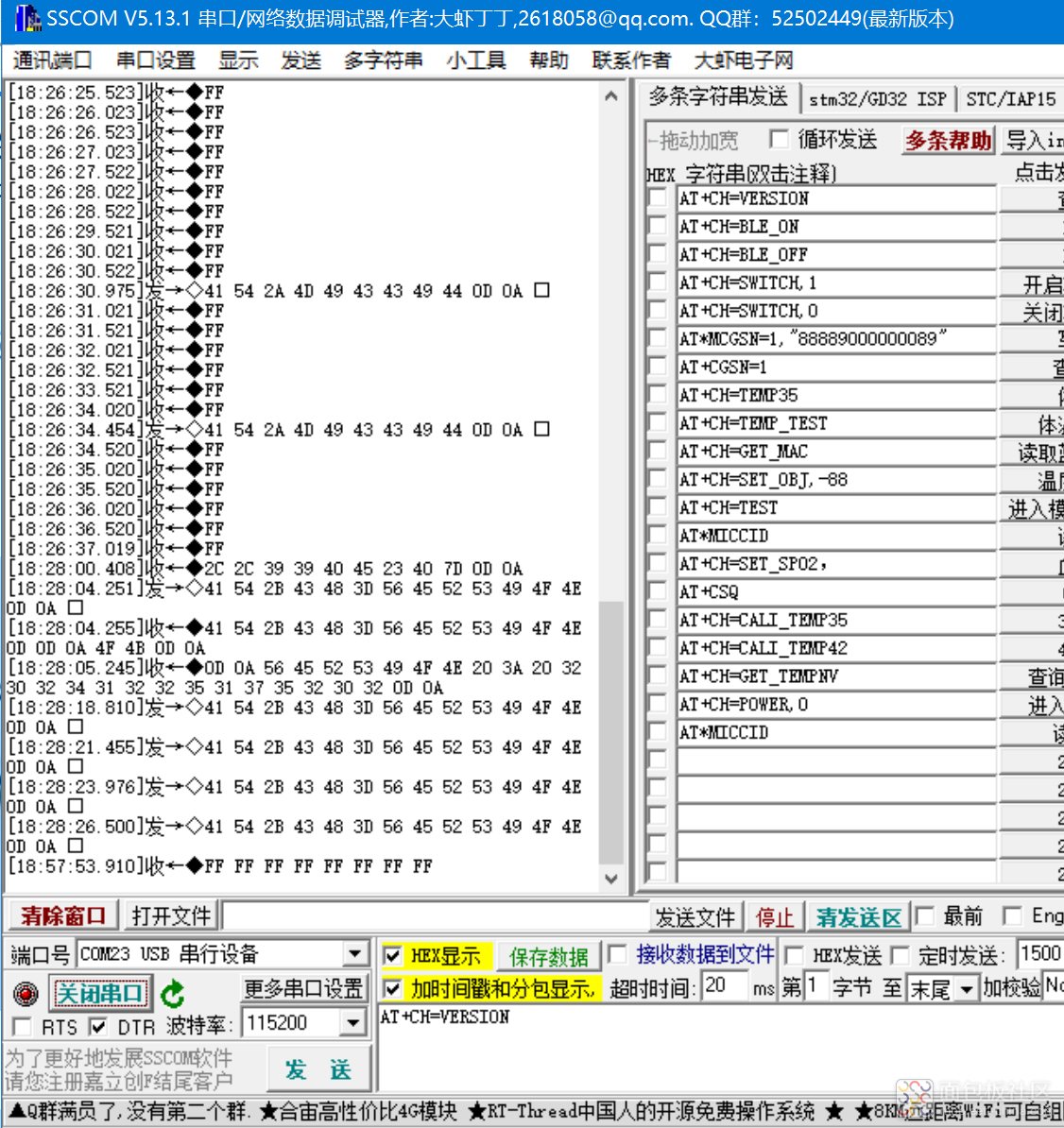

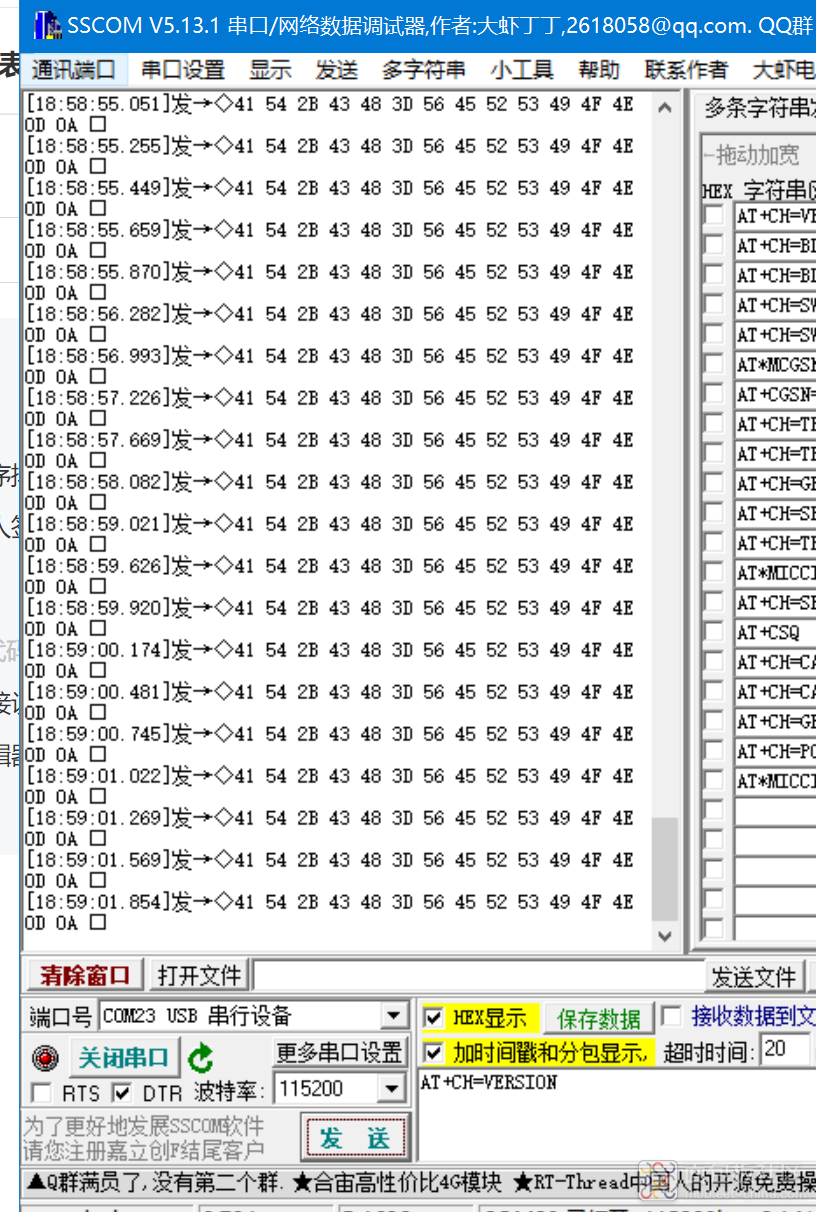

最开始出现的问题:REPL MicroPython 环境搭建

1. 出现的问题及解决方法

- 固件烧录失败:在将 MicroPython 固件烧录到富芮坤 FR3068x - C 芯片时,可能会遇到烧录失败的情况。这可能是由于烧录工具与芯片之间的连接不稳定,或者固件版本与芯片不兼容导致的。解决方法是检查烧录工具的连接线路,确保连接牢固,同时仔细核对所使用的固件版本是否适用于 FR3068x - C 芯片。

- 串口通信问题:REPL 环境依赖串口通信来实现与开发板的交互。在搭建过程中,可能会出现串口无法识别或者通信异常的问题。这可能是由于串口驱动未正确安装,或者串口波特率设置不正确。此时,需要安装对应的串口驱动程序,并根据开发板的要求设置正确的波特率。

- 内存、时钟问题:MicroPython 运行需要一定的内存空间,不合理的参数变量导致溢出内存不足,会MCU死机重启导致环境搭建失败或者运行不稳定:

-

- 在这种情况下,

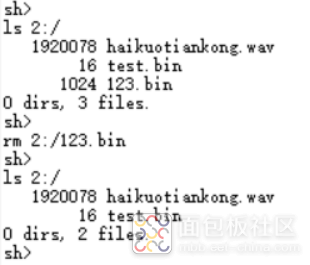

2. 搭建效果

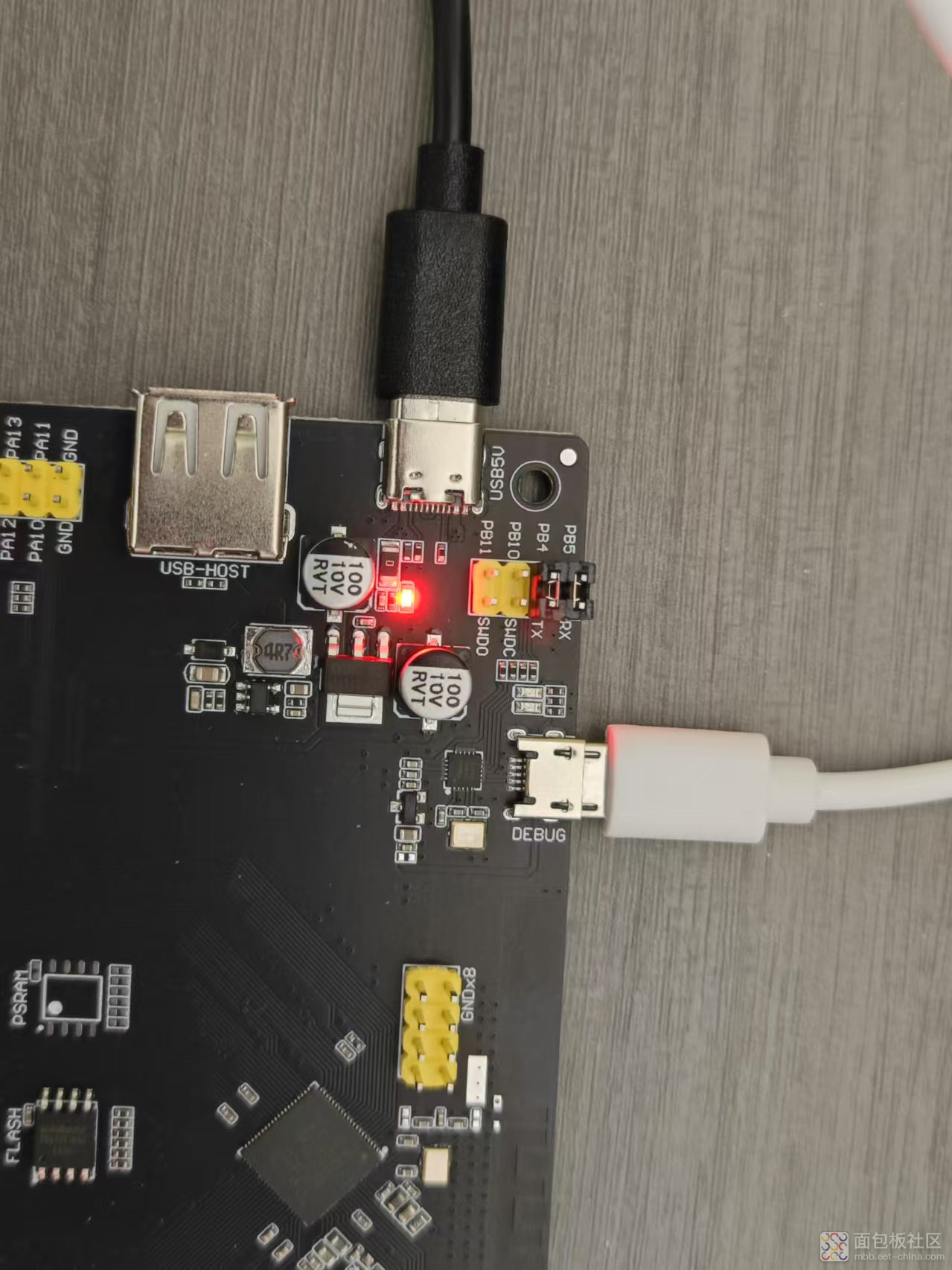

先连接好PC与开发板

经过一系列的调试和优化,成功搭建起 REPL MicroPython 环境后,开发者可以通过串口终端方便地与 FR3068x - C 芯片进行交互。在这个环境中,可以实时输入和执行 MicroPython 代码,快速验证代码的功能,大大提高了开发效率。而且,REPL 环境提供了丰富的调试信息,有助于开发者及时发现和解决代码中的问题。

三、实际效果评测

- 音质表现:在实际播放测试中,FR3068x-C 的音质表现较为出色。对于常见的 MP3 格式音乐文件,能够清晰还原音频细节,声音饱满,没有明显的杂音和失真。无论是流行音乐中的复杂乐器演奏,还是人声的细腻表达,都能较好地呈现。

- 播放稳定性:在长时间的播放测试中,基于 REPL MicroPython 实现的音乐播放功能表现稳定。没有出现卡顿、中断等异常情况,即使在频繁切换歌曲、调整音量等操作下,也能保持稳定运行,这得益于芯片良好的处理能力和 MicroPython 程序的优化。

- 资源占用:从资源占用情况来看,FR3068x-C 在播放音乐时对系统资源的占用处于合理范围。不会因为音乐播放而导致系统运行缓慢或其他功能无法正常使用,这使得它在实现音乐播放功能的同时,还能兼顾其他任务的执行。

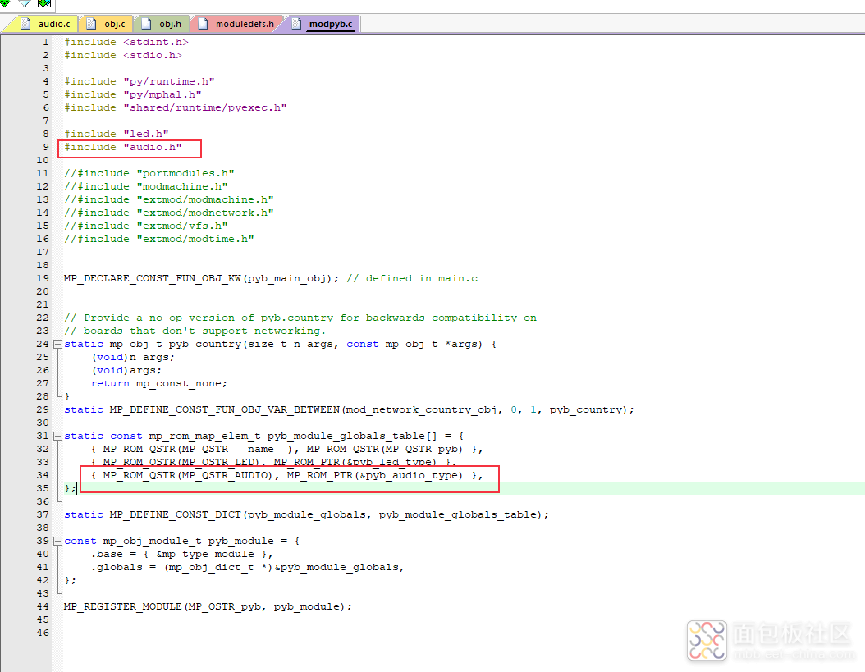

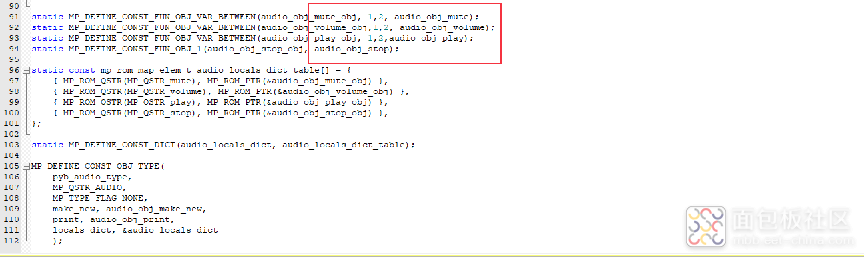

py\genhdr\moduledefs.h中之前LED示例中已经注册模块pyb_module,我们在

Src\py_port\modpyb.c中

pyb_module_globals_table下添加

{ MP_ROM_QSTR(MP_QSTR_AUDIO), MP_ROM_PTR(&pyb_audio_type) },

即注册pyb下的audio。

实现代码见audio.c和audio.h

audio.c中实现

主要绑定实现以下接口,mute,volume,play,stop

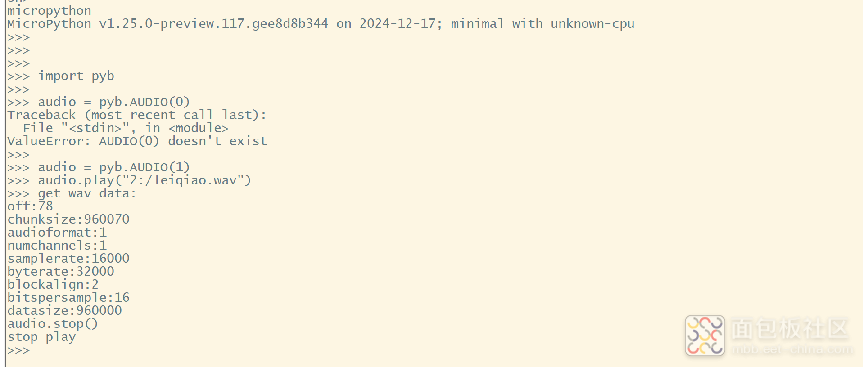

六.Micropython下音频播放测试

详细效果见视频演示

Shell环境中输入micropython进入python环境,

import pyb

audio = pyb.AUDIO(1) 这里注意ID从1开始只有一个实例

开始播放audio.play("2:/leiqiao.wav")

提前结束播放audio.stop()

mute测试

audio.mute(1) 静音

audio.mute(0) 不静音

设置音量测试

audio.volume(1)可以听到声音变小

退出python环境 按组合按键ctrl+d

四、总结

富芮坤 FR3068x-C 基于 REPL MicroPython 实现本地音乐播放,在硬件和软件的协同下,展现出了良好的性能。无论是音质表现、播放稳定性还是资源占用方面,都有着不错的成绩。本开发板的测试环节结束,测试过程中遇到一些问题和困难,感谢富芮坤官方技术人员的大力支持。如 FLASH 空间分配的控制等,后续将进行深入探讨,敬请期待。这一功能的实现,不仅丰富了 FR3068x-C 的应用场景,也为相关开发者在音频处理和播放领域提供了新的选择。未来,随着技术的不断发展和优化,相信 FR3068x-C 在音乐播放及更多领域会有更出色的表现的细节、内容侧重点等方面有调整想法,比如想增加和其他芯片的对比,欢迎随时告诉我。

/4

/4