一个小概念:关于上升时间的理解

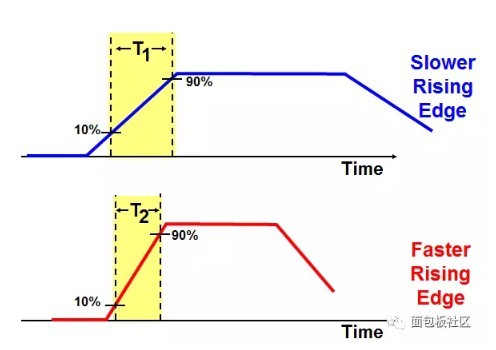

一个小概念:关于上升时间的理解任何一个真实的数字信号在由一个逻辑电平状态跳转到另一个逻辑电平状态时(比如信号从低电平跳转到高电平),其中间的过渡时间都不会是无限短。 如果信号电平跳变的过渡时间越短,说明信号边沿越陡。 我们通常使用上升时间(Rising...

@面包板社区微信用户hk提问:

上升时间不满足芯片要求,如过快或者过慢等不同情况,会分别有哪些方面的问题?

面包板用户A回答:

我觉得这得和源,路径,负载的状态相关起来考虑。高速信号必然要求陡峭的信号边沿(实际上我认为数字信号都希望有陡峭的信号上升沿,这样可以快速度过开关的线性区),但是由于负载总有一个开门和关门时间,这个时间基本上由开关器件的输入电容决定,为了快速开关,必须要充放电迅速,而这就和充电路径和源端有关系了,差的电路设计和不正确的阻抗匹配,都会导致开关速度的下降,因此高速数字电路设计是采用分布式电路理论设计的。而长的上升时间和下降时间,会导致器件在线性区逗留的时间变长,在数字信号里面,这段时间对应不确定状态,是希望避免的。

面包板用户B回答:

建议查一下建立保持时间的影响。

面包板用户C回答:

上升沿过快,辐射会高;

来源:面包板

/5

/5