ZYNQ7000器件将FPGA和ARM集成在一个芯片内部,除了获得集成度高,节省PCB面积的优点外,FPGA和ARM在片内通信互联相比在片外器件间通过通信总线互联还具有降低功耗、提高通信带宽和增加灵活性的优点。本文拟就ZYNQ7000器件内ARM(PS)和FPGA(PL)的通信方式和高速传输要用到的DMA进行了解,然后就开发中经常用到的在PS和PL间进行高速通信进行实验测试,对应的应用场景有: PL测采集到数据,然后用DMA从PL搬移数据到PS侧的DDR3内存,或者PL连接DAC, 用DMA从PS侧的DDR3内存把DAC数据连续地搬移到PL侧等等。

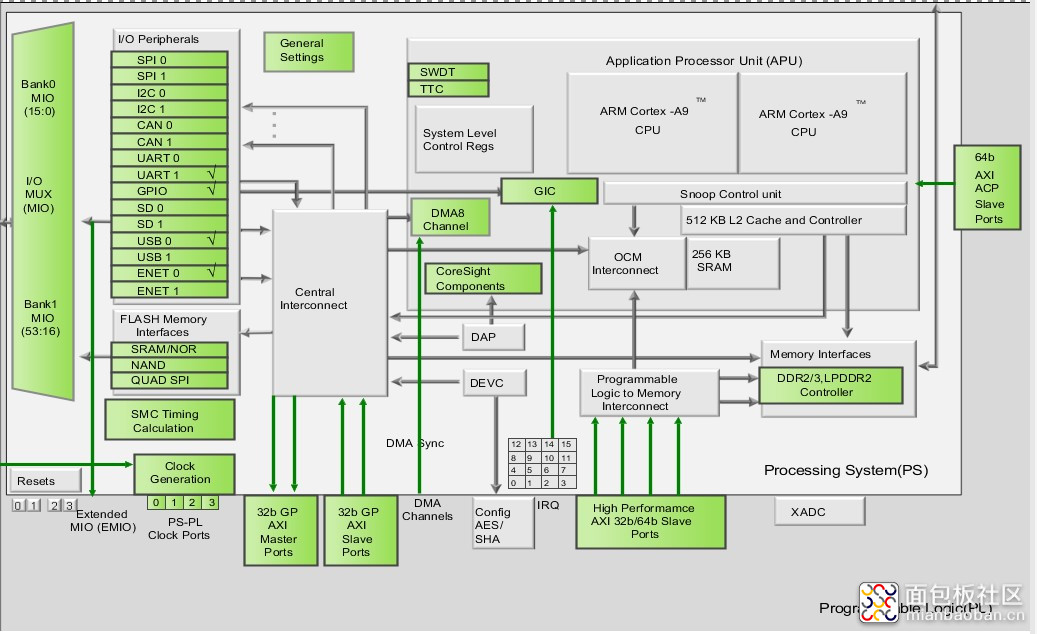

一、PS与PL的通信方式参考下面的ZYNQ的系统框图:

下面和右侧灰色部分为PL,从左往右可以看到和PS部分的互连通信接口有:

1、Extended MIO (EMIO),相当于把PS外设的引脚内部连接到FPGA上,这里注意QSPI、SMC(控制SRAM/NOR/NAND)、USB外设是不能布线到EMIO上的。总共有192个EMIO可以作为GPIO连接到PL部分,其中128个为PS输出到PL部分,64个为PL输出到PS部分。

2、AXI_GP接口, 包括两个32位的AXI_GP主设备接口和两个32位的AXI_GP从设备接口,主要用在速率比较低的情况下互连通信。

3、DMA Channels, 用在不需要CPU干预情况下在PS和PL间进行大量数据的搬移,第二节我们将进一步介绍。

4、AXI_HP接口,包括四个高性能/带宽的AXI3.0标准的接口,PL模块是作为主设备连接,主要用于PL访问PS上的存储器(DDR和On-Chip RAM),可以配置为32位或者64位的AXI_HP总线。

5、AXI_ACP接口,是ARM多核架构下定义的一种接口,全称acceleratorcoherency port(ACP),中文翻译为加速器一致性端口,这个接口为64位的总线,并且只能是PL端为主设备,PS端是从设备,通过该接口,PL可以直接访问PS的cache,同时也可以第一时间将逻辑加速运算结果送至cache中,特点是有很低的延迟。

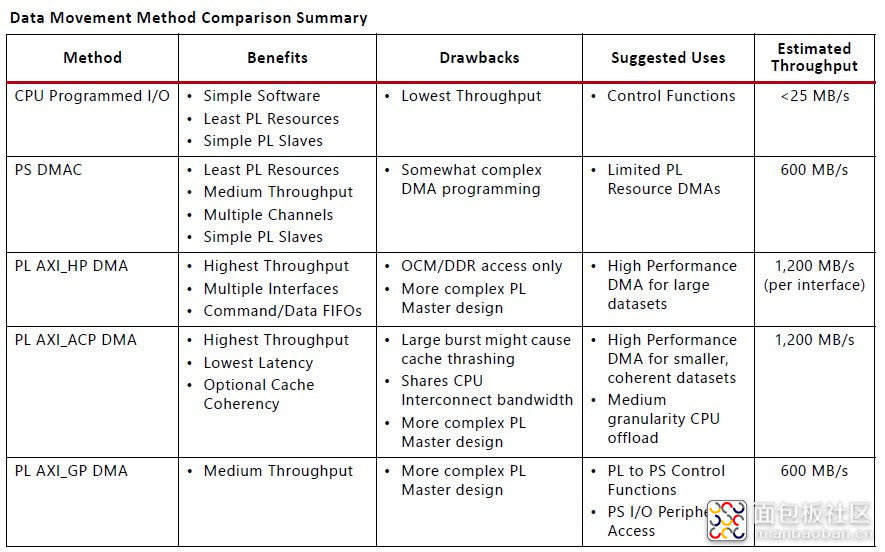

总的来说,第一种用EMIO的方式速率比较慢,但实现方式比较灵活,后面四种方式都是总线互连的方式,能达到的速率和总线频率及总线宽度有关,下表是XILINX提供的一个通信方式的比较,有参考速率和适用选择建议:

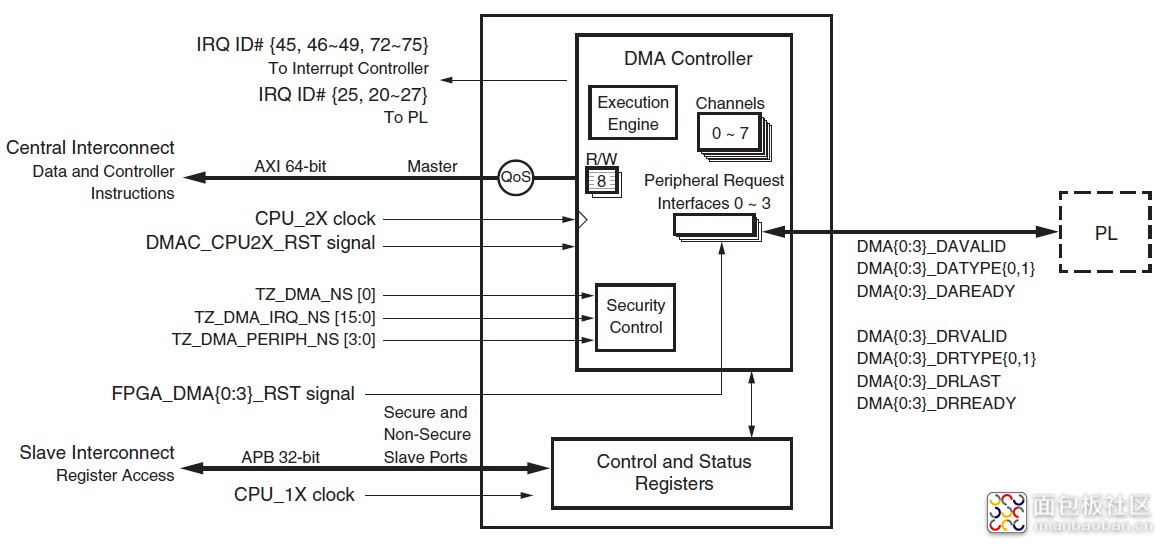

二、DMA控制器介绍

如果想进行高速数据传输,使用DMA是免不了的,ZYNQ-7000器件的DMA使用要区分下是分为PS侧的DMAC和PL侧的AXI DMA IP核的使用。

ZYNQ-7000器件PS侧的DMAC(Direct Memory Access Controller)使用一个工作在CPU_2x时钟频率的64位AXI接口,实现系统存储器和外设(包括PL)之间的高速传输,DMAC的特点有:

(1)DMA引擎拥有一个灵活的指令设置DMA的传输,包括灵活的分散-聚集存储器传输,对于源和目的寻址的完全控制,定义AXI交易属性,管理字节流等;(2)拥有8个cache线,每一个cache线宽度是4个字;

(3)拥有8个可以并发的DMA通道线程,允许并行执行多个线程,最多支持到8个读和8个写AXI交易;

(4)拥有8个中断给中断控制器,可以给到PS和PL;

(5)拥有8个DMA触发事件并且可以编码控制;

(6)一个传输过程中,128个64bit位宽的MFIFO用于缓冲控制器读/写的数据;

(7)安全特性,有专用的APB从接口用于访问安全寄存器,另外可以将整个控制器的配置分为安全模式和非安全模式。

(8)支持任意内存到内存的DMA传输;

(9)四个PL外设请求接口,用于管理控制进出到PL侧的流,每个接口支持最多4个活动的请求;

ZYNQ-7000器件PS侧的DMAC的系统结构如下图示:

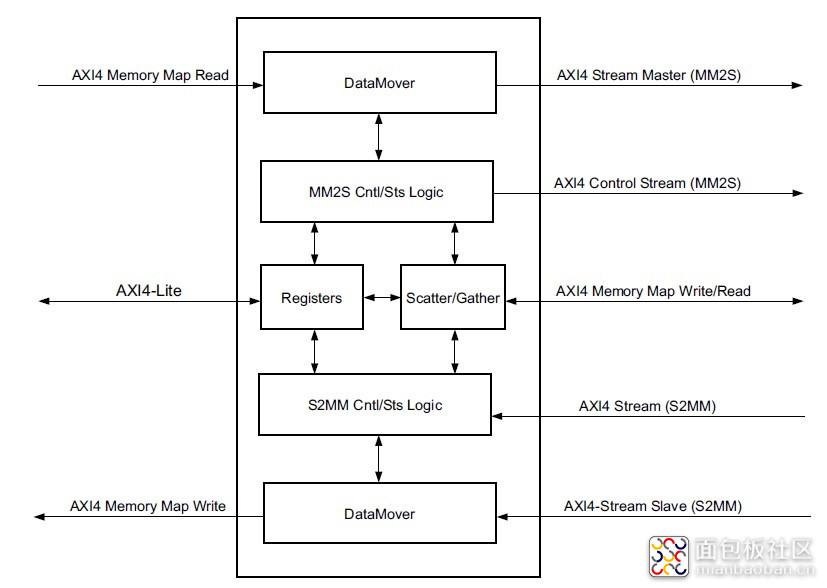

ZYNQ-7000器件PL侧的AXI DMA IP核在AXI内存映射和AXI4-Stream目标外设之间提供高带宽直接内存访问。其可选的分散/收集功能还可以从中央处理单元(CPU)卸载数据移动任务,通过AXI4-Lite从设备接口访问初始化,状态和管理寄存器。其主要特点有:

(1)符合AXI4标准 (Compliant合规);(2)可选独立的分散/收集直接内存访问(DMA)支持,提供从CPU卸载DMA管理工作,提供独立于主数据总线的提取和更新传输描述符的总线,允许描述符放置在与数据缓冲区分开的任何存储器映射位置。例如,描述符可以放在块RAM中。提供可以选择的循环操作(cyclicoperation);

(3)可选的直接寄存器模式,无分散/收集支持。通过排除分散/收集引擎,可以启用较低性能但较少的FPGA资源密集型模式。 在此模式下,通过设置源地址(MM2S)或目标地址(对于S2MM),然后在长度寄存器中指定字节计数来控制传输;

(4)主AXI4数据位宽支持32、64、128、256、512和1024比特;

(5)主AXI4-Stream数据宽度支持8、16、32、64、128、256、512和1024比特;

(6)可选数据重新对齐引擎,流数据宽度最大为512比特,允许数据重新对齐主存储器映射和流数据路径上的字节(8比特)级别;

(7)可选的AXI控制和状态流,可与AXI以太网IP连接,为MM2S通道提供可选的控制流和为S2MM通道可选的状态流,以从高带宽数据通路卸载低带宽的控制和状态。

(8)可选的微型模式(Micro Mode),AXI DMA可配置为提供低占用空间,低性能的IP,可处理小数据包的传输。

ZYNQ-7000器件PL侧的AXIDMA IP核的系统结构如下图示:

三、实验操作

为了获得最大的PS和PL间的通信带宽,根据第一节的介绍我们应该使用AXI HP或者AXI ACP接口进行通信,并且要使用64比特的位宽,米尔科技提供的MYD-C7Z010/20开发板的配套光盘的MYD-C7Z01020_V08_20181220\05-Programmable_Source\7Z010目录下有个DMA.rar文件是一个参考DEMO, 具体操作可以参考该目录下doc文件夹下的MYiR Zynq FPGA 使用手册.pdf的第124页~135页,这里我们实验功能和这个DEMO类似,但会使用DMA中断功能,使用AXI HP接口在PS侧DDR3内存和PL的AXI FIFO(实际开发中可以替换为有相同接口的用户自定义IP)间用DMA进行高速传输,DMA传输完成后会中断通知到PS进行后继处理,并在Vivado2018.3工具下详细描述实验步骤,具体如下:

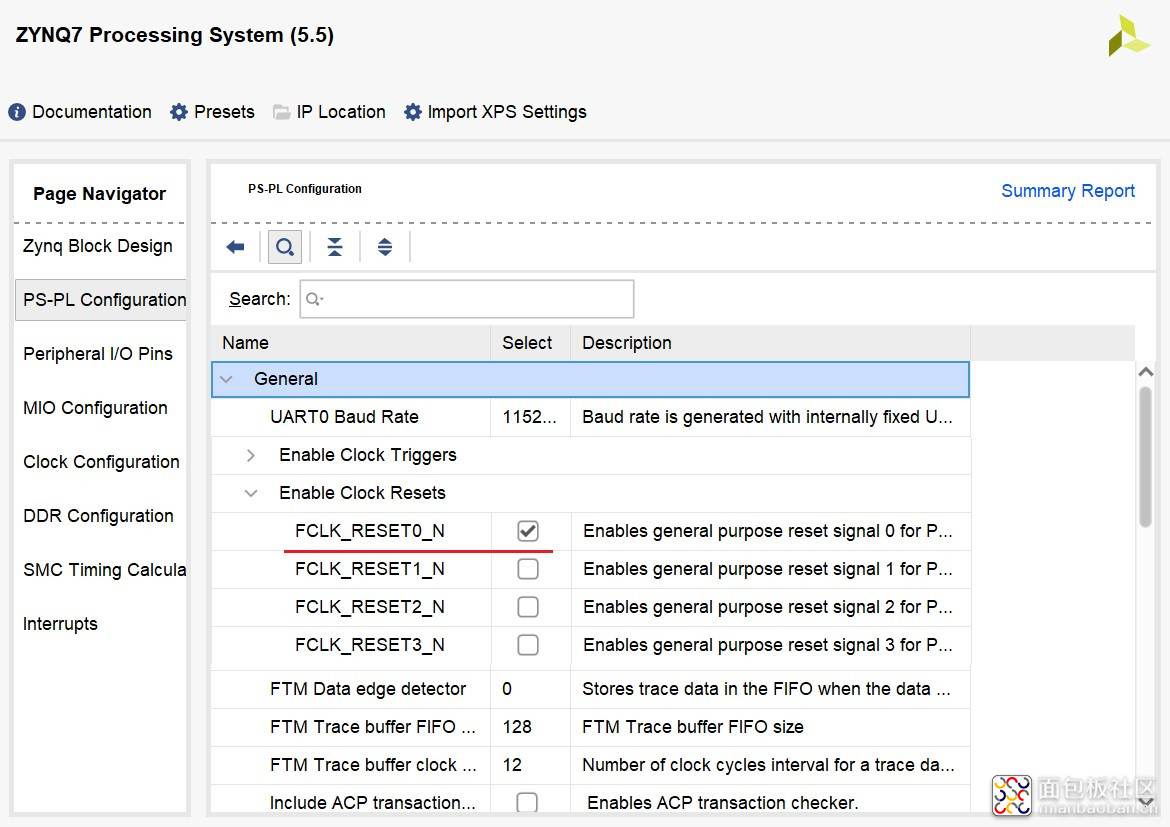

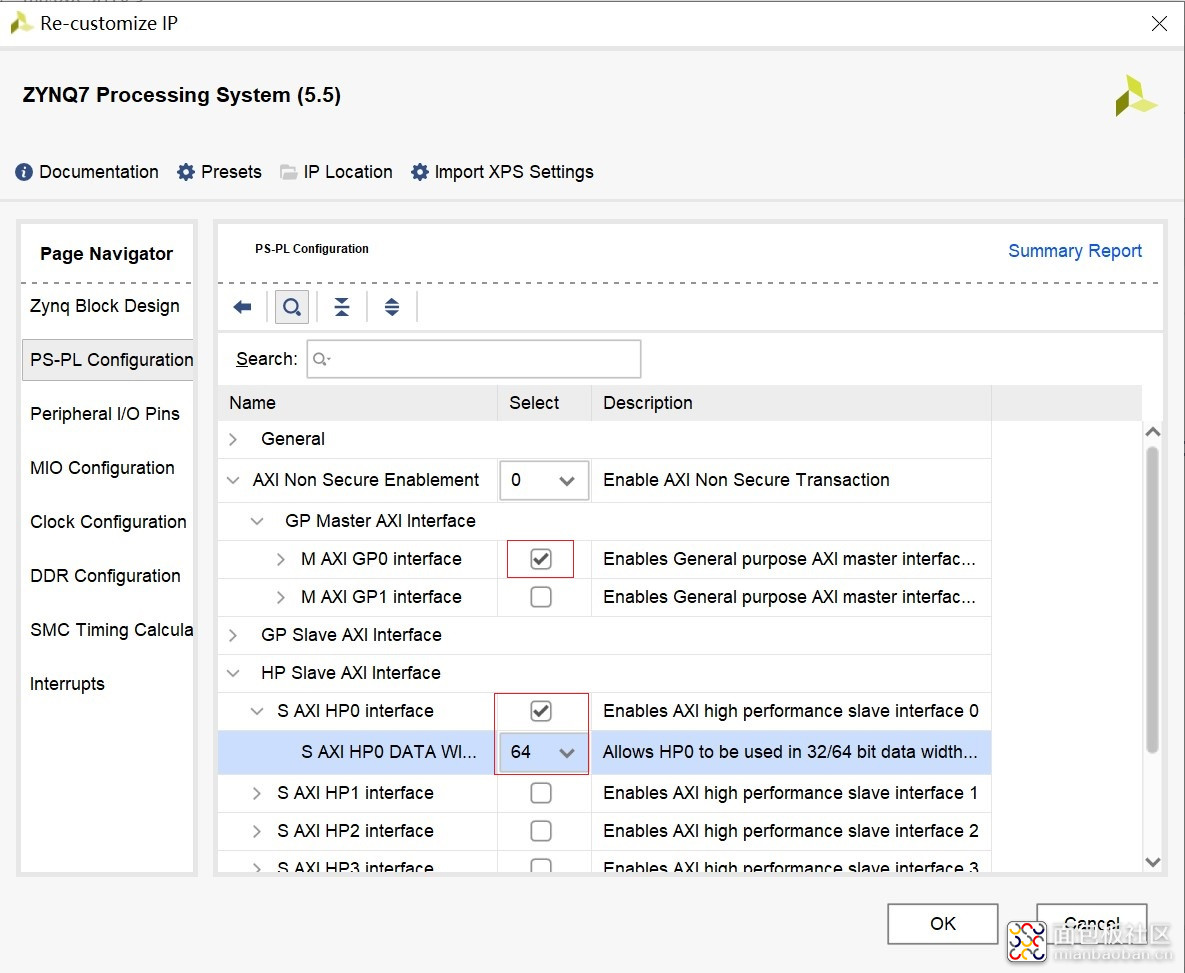

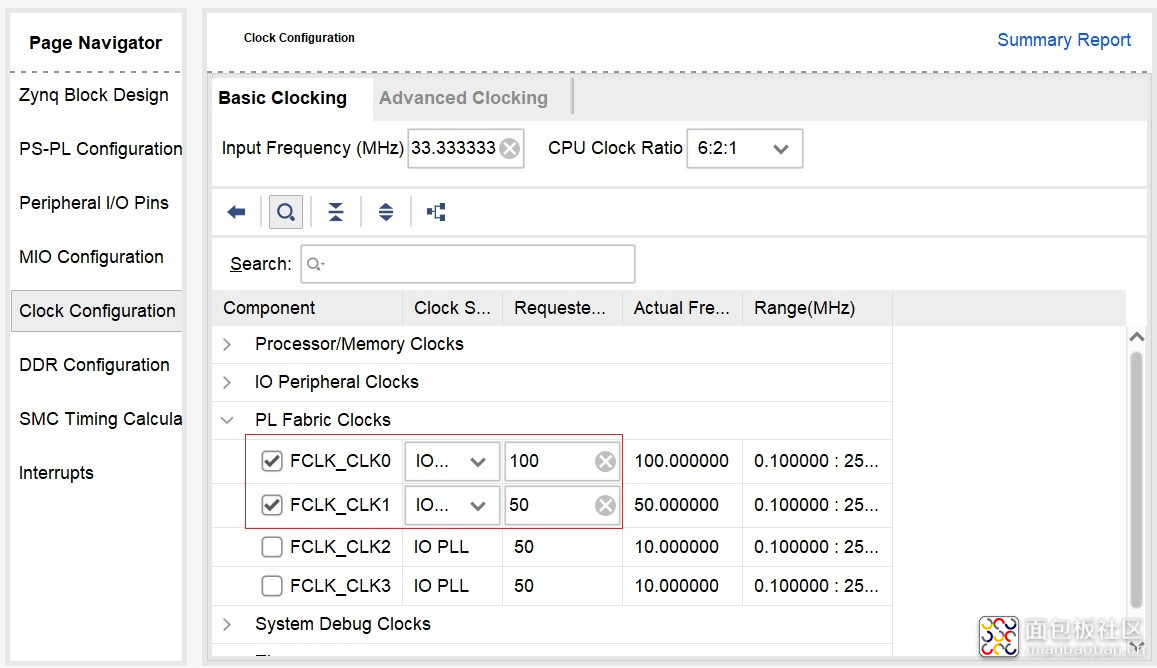

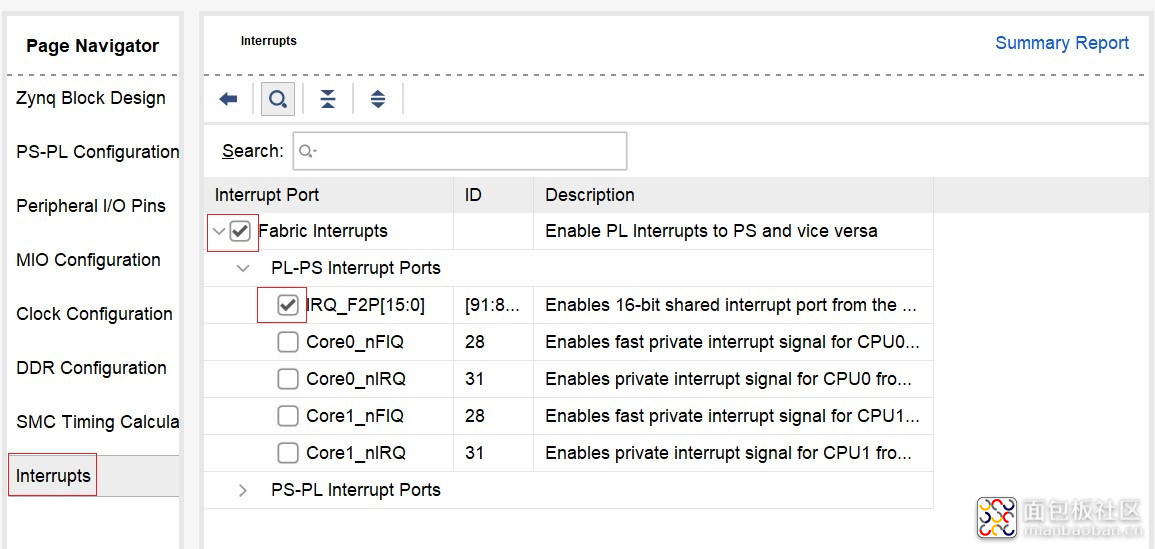

1、参考之前的试用报告新建一个工程名为axi_hp_dma的工程,增加ZYNQ7 Processing System处理器IP,这里我们直接用米尔科技提供的DMA.rar压缩包下的MYIR.tcl预设脚本进行参数设置,然后我们可以查看检查下比较重要的配置项,在界面左侧选择PS-PL Configuration,General—Enable ClockResets下勾选上FCLK_RESET0_N, AXI Non Secure Enablement—GP MasterAXI Interface下勾选上M AXI GP0 interface, HP Slave AXIInterface下勾选上S AXI HP0 interface,数据宽度选择64比特,用于DMA和DDR控制器间通信; 在界面左侧选择Clock Configuration, 然后在PL Fabric Clocks里勾选上FCLK_CLK0和FCLK_CLK1, 为PL提供100MHz和50MHz的时钟;在界面左侧选择Interrupts—Fabric Interrupts前打勾使能PL和PS间的中断,点开PL-PS InterruptPots, 勾选上IRQ_F2P[15:0]。具体如下图表示:

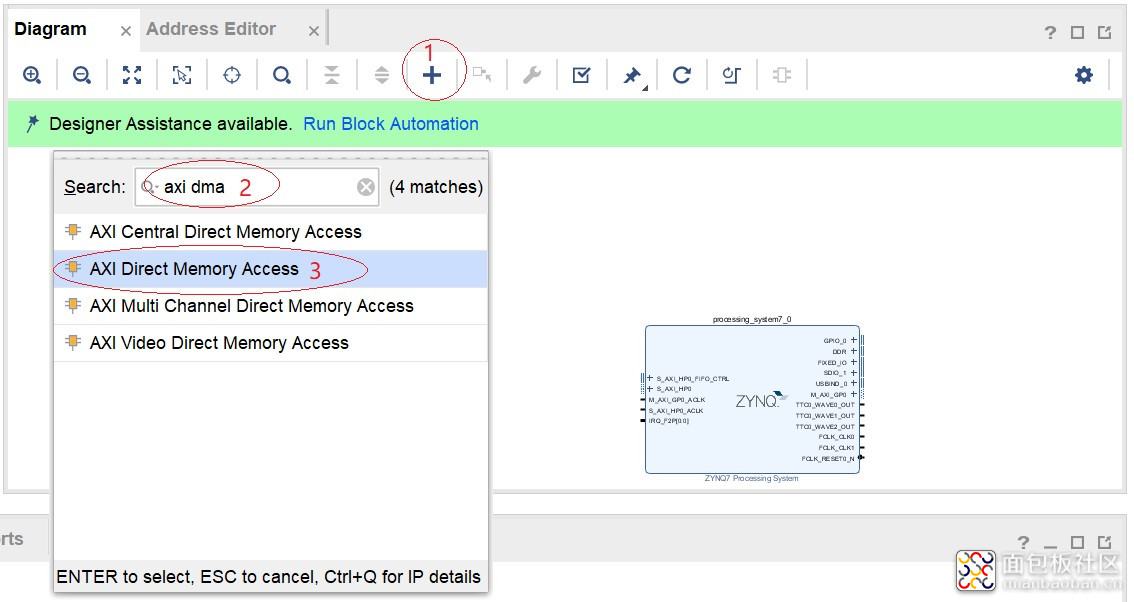

2、点击块图上面的+号增加新的IP,在搜索栏输入axidma找到AXI Direct Memory Access项,回车添加IP到块图,如下图表示:

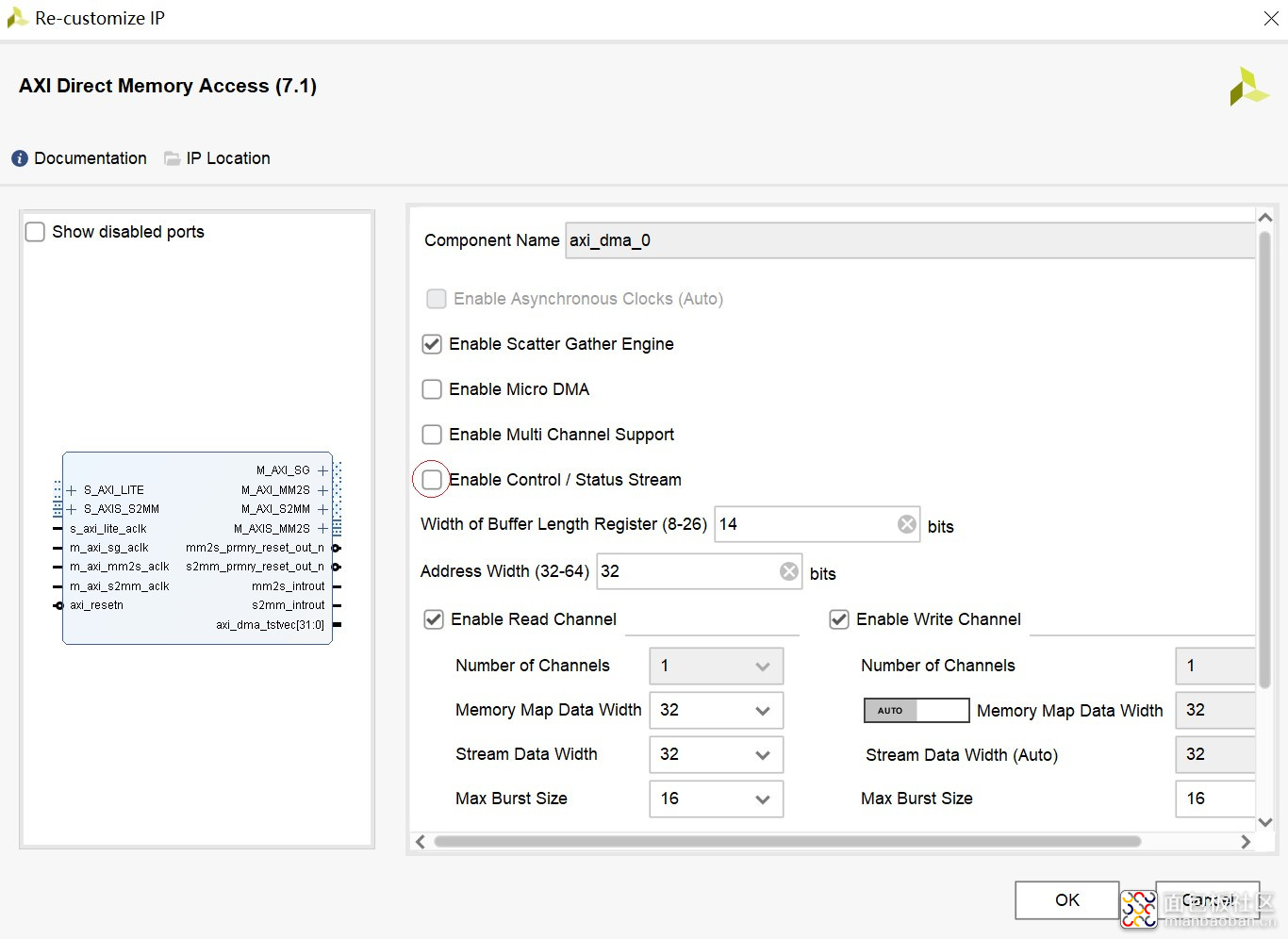

双击DMA IP核按下图设置参数(主要是去勾选EnableControl/Status Stream):

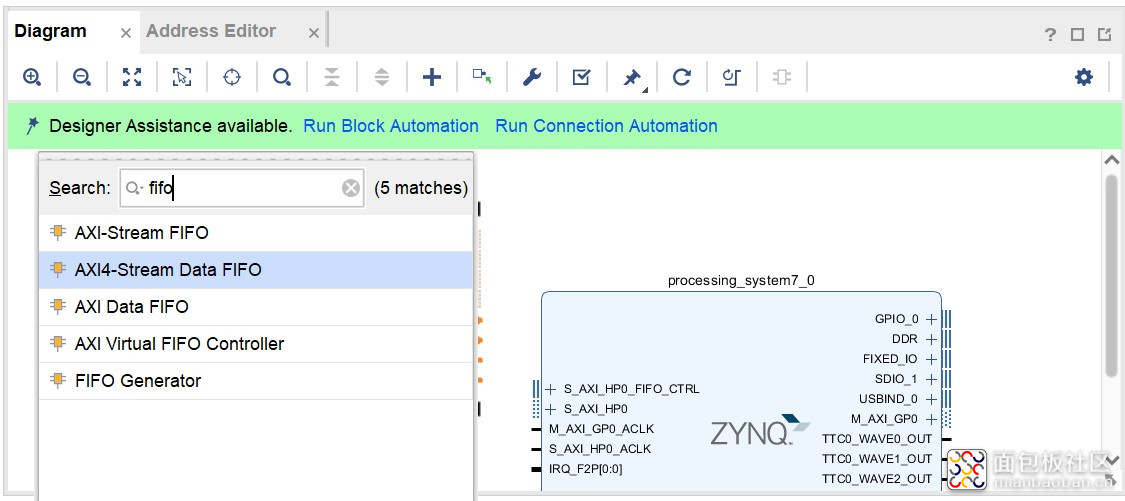

3、点击块图上面的+号增加新的IP,在搜索栏输入fifo找到AXI4– Stream Data FIFO项,回车添加IP到块图,如下图表示:

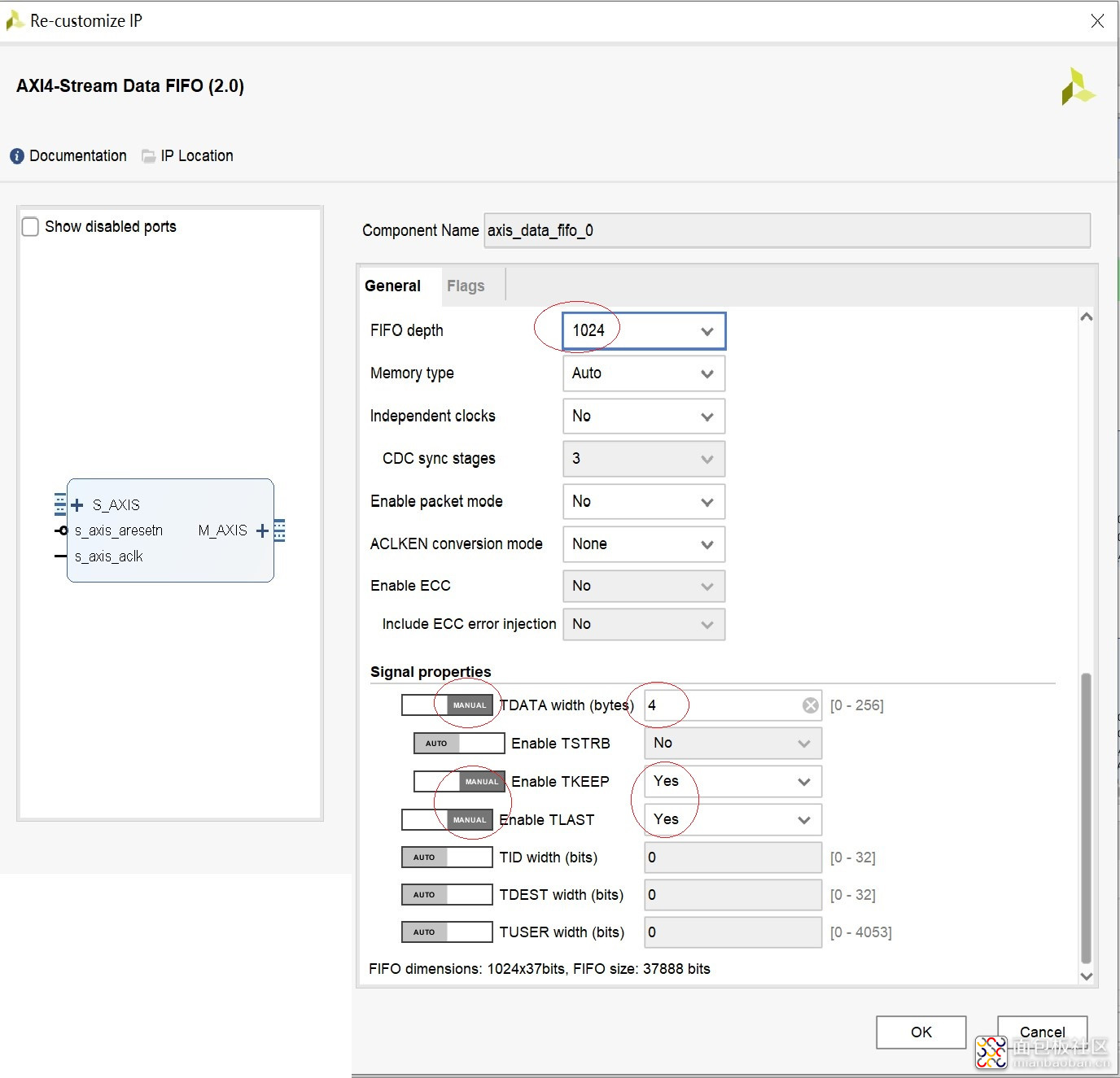

双击AXI4– Stream Data FIFO IP核按下图设置参数:

4、点击块图上面的+号增加新的IP,在搜索栏输入Concat找到Concat项,回车添加IP到块图,用样方法输入reset找到Processor System Reset项,回车添加IP到块图。这两个IP参数用默认值不用设置。

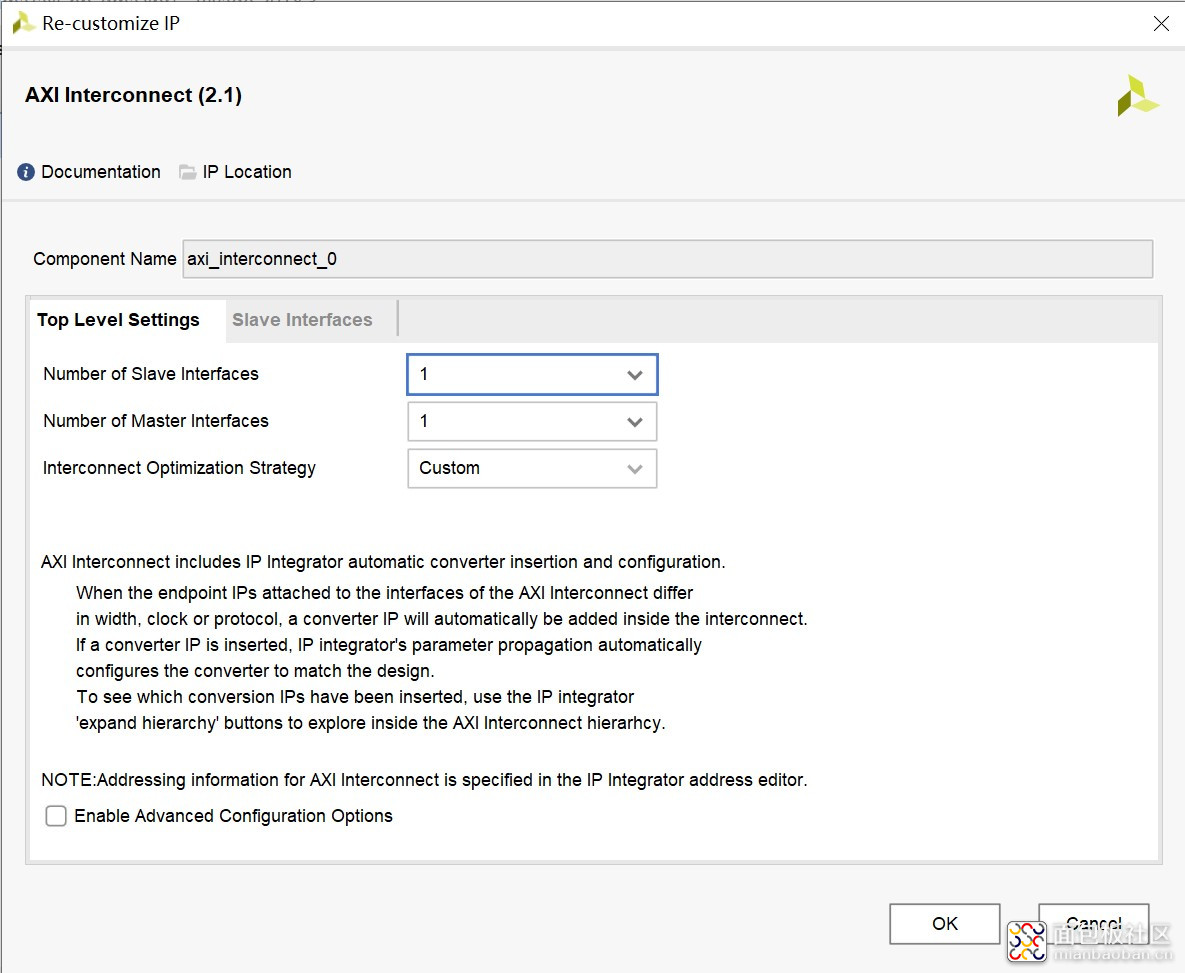

5、点击块图上面的+号增加新的IP,在搜索栏输入Interconnect找到AXI Interconnect项,回车添加IP到块图,用样方法再增加一个AXI Interconnect IP核,axi_interconnect_0按下图进行IP核参数设置:

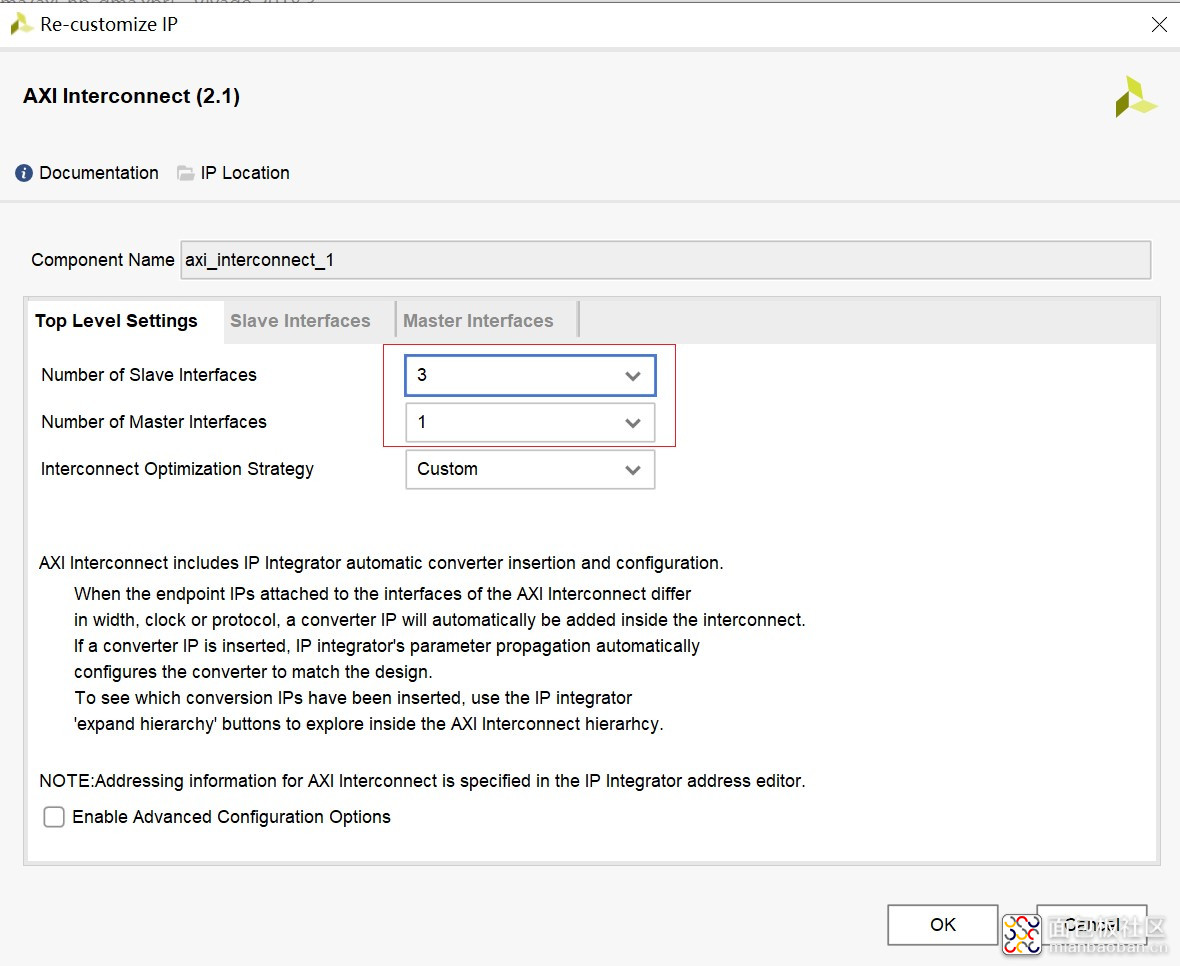

axi_interconnect_1按下图进行IP核参数设置:

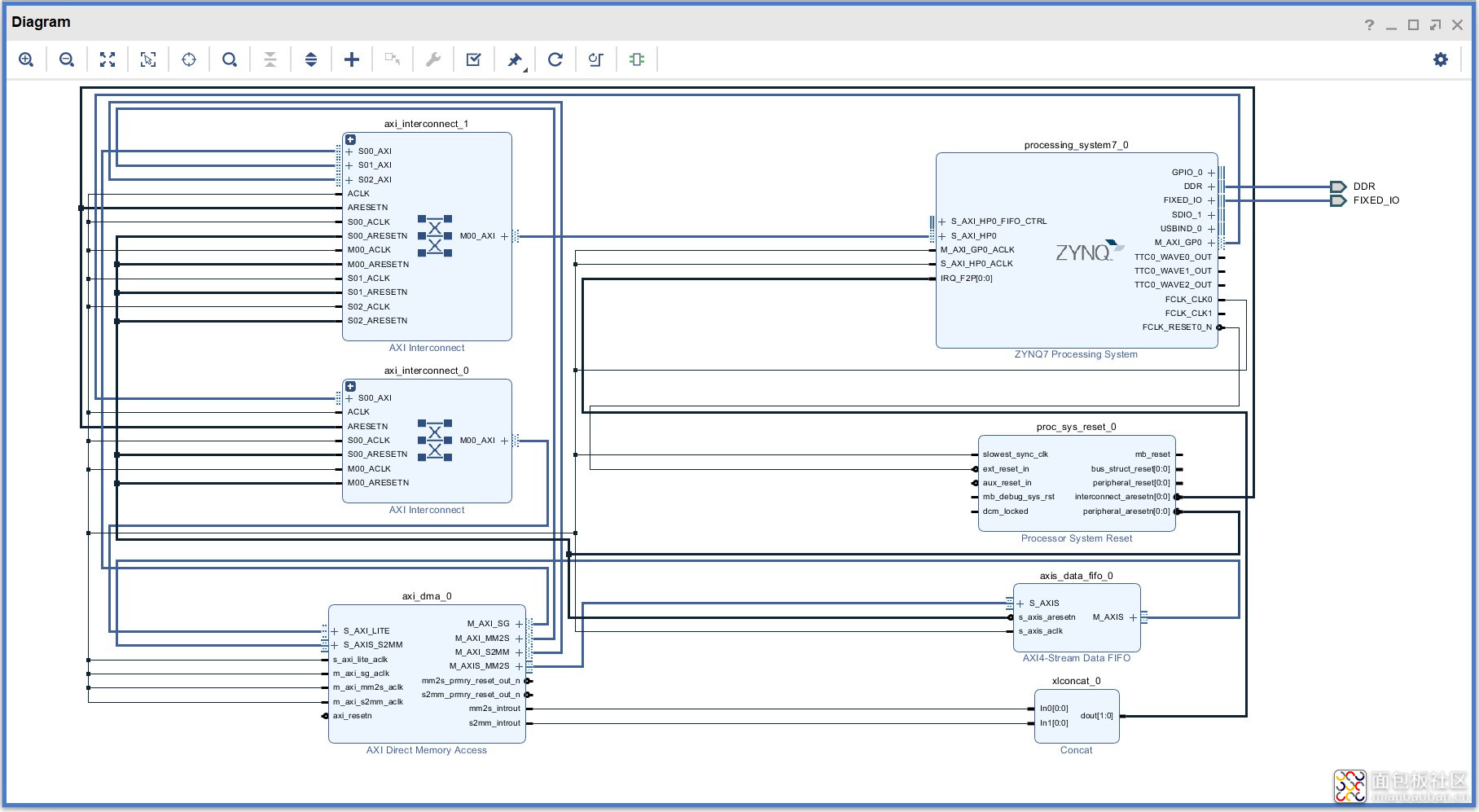

6、系统信号互连,选择IP模块上的一个信号名字,然后按着鼠表左键可以一直拖拽到要连接的另外一头IP模块的信号端口上,先点块图上方的Run Block Automation,再手动连接,具体连接如下图示:

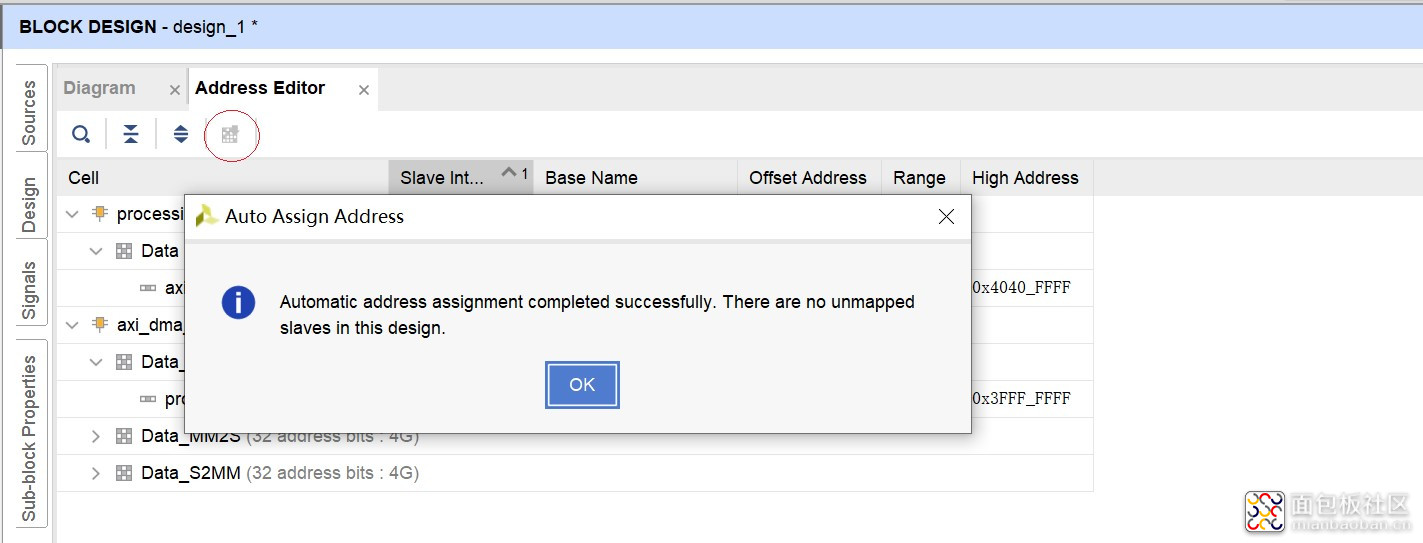

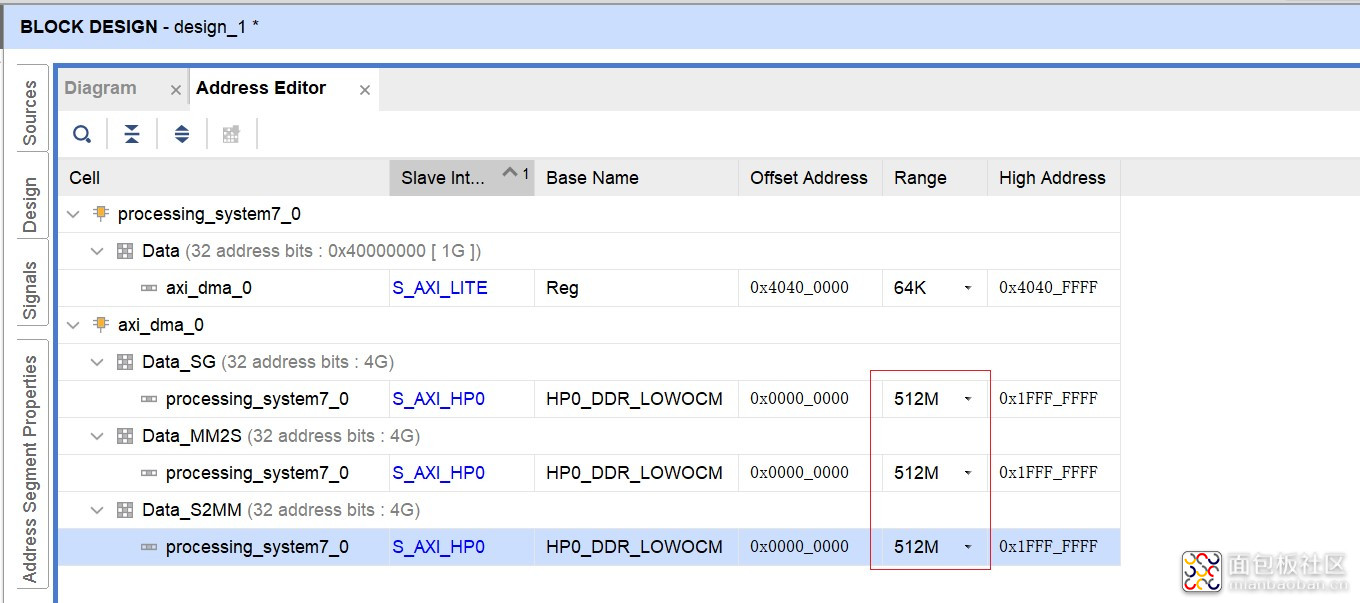

7、分配地址空间,先进行自动地址分配,然后DMA的地址范围调整为512M, 具体如下图表示:

8、生成综合文件、生成FPGA顶层文件、生成比特流文件、导出硬件配置文件(这里要勾选上Includebitstream),大家可以参考MYiR Zynq FPGA 使用手册.pdf的第127页~129页的1.2~1.5节,这里不再贴图描述。

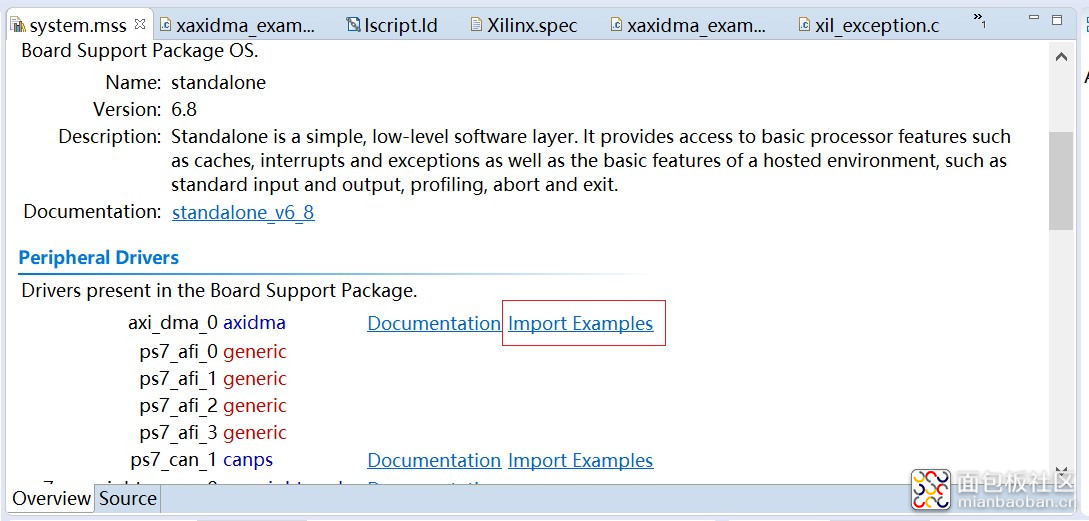

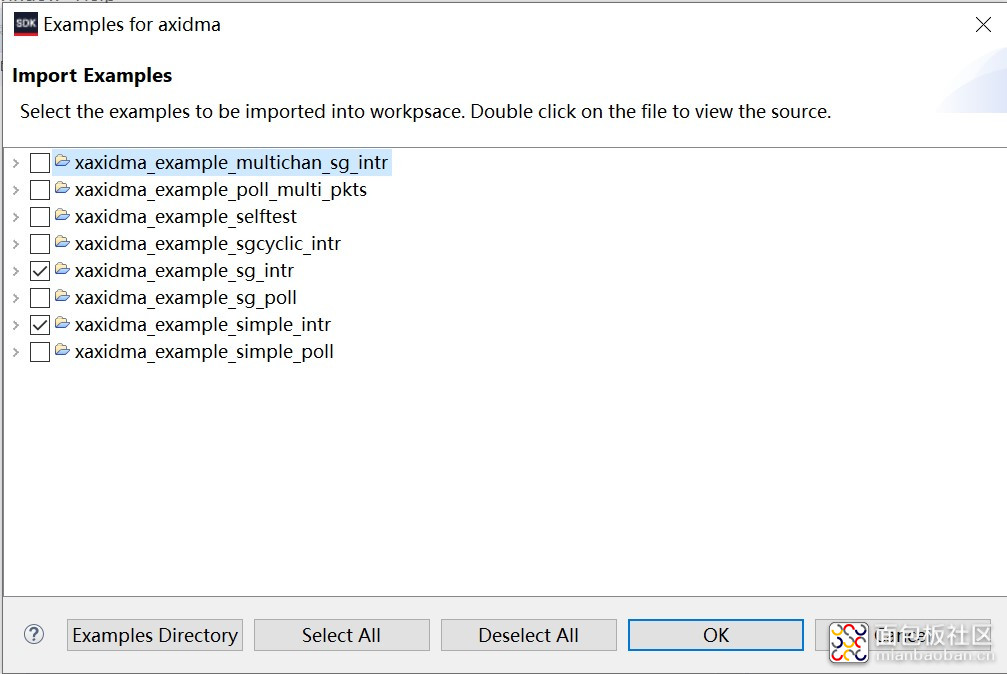

9、运行SDK软件生成FSBL工程,大家可以参考MYiR Zynq FPGA 使用手册.pdf的第130页~131页的1.6节,生成工程后我们可以在BSP包找到DMA中断的Example工程,如下图示:

这里有axi dma驱动的文档,对照Example工程用JTAG Debug功能可以快速研究DMA的使用,由于时间所限,目前只是简单跑了下Example工程,详细的使用方法有待深入研究后整理分享。

四、主要参考文献

1、XILINX: UG585(V1.12.2)- Zynq-7000 SoC Technical Reference Manual

2、XILINX: PG021 AXI DMAv7.1 LogiCORE IP Product Guide

3、米尔科技: MYiR Zynq FPGA 使用手册.pdf

/5

/5