Verilog HDL (Hardware Description Language) 是一种硬件描述语言,可以在算法级、门级到开关级的多种抽象设计层次上对数字系统建模。它可以描述设计的行为特性、数据流特性、结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。此外,verilog提供了编程语言接口,通过该接口用户可以在模拟、验证期间从外部访问设计,包括模拟的具体控制和运行。Verilog 不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。因此,用这种语言编写的模型能够使用 Verilog 仿真器进行验证。 Verilog 从C语言中继承了多种操作符和结构,所以从结构上看两者有很多相似之处。

Verilog HDL在开发 FPGA 、ASIC 时使用的语言,跟开发软件使用 C语言一个道理。

Verilog 大小写敏感,且所有关键字都是小写。

1 寄存器

register = storage,是数据存储单元的抽象,可视为能够存储数值的变量 (variable that can hold value)

关键字 reg; 缺省值 x;

2 网络连接 net = connection, 表示寄存器之间的连接,只能采用连续赋值 (must be driven continuously)

关键字 wire; 缺省值 z;

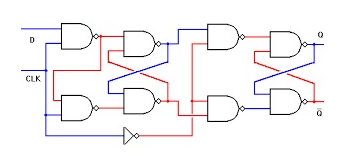

2.1 D 触发器 (同步复位)module dff(clk, rst, d, q); //dff with syn reset input clk, rst, d; output q; reg q; always @(posedge clk) begin if (rst) q <= 1'b0; else q <= d; end endmodule

复制代码module dff(clk, rst, d, q); // dff with asyn reset input clk, rst, d; output q; reg q; always @(posedge clk or posedge rst) begin if (rst) q <= 1'b0; else q <= d; end endmodule

复制代码

3 连续赋值 continuous assignment

assign data_left = data_right; // right drive left(net)

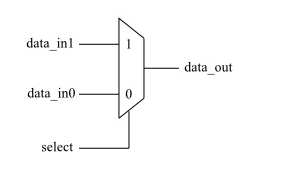

例:选择器 mux

assign data_out = select ? data_in1 : data_in0;

4 procedural assignment

1) 阻塞赋值 ("=")

execute sequential

2) 非阻塞赋值 ("<=")

read (right) -> schedule (left) -> execute (<=)

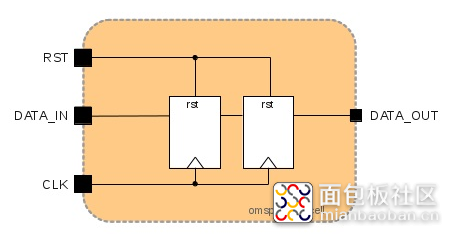

例: synchronizer

reg [1:0] data_sync;

always @ (posedge clk or posedge rst)

begin

if (rst)

data_sync <= 2'b00;

else

data_sync <= {data_sync[0], data_in};

end

assign data_out = data_sync[1];

/5

/5