综合N篇paper的说法,LDO的设计大概要考虑3个方面:1,闭环稳定性(closed-loop stability);2,环路带宽(BW);3,SRG(输出调整管栅端的SR)。

1和2是小信号设计参数,取决于反馈系统的零-极点位置设计,那么有无数篇paper去讲环路的各种补偿方式,忒复杂,今天不再展开,以后遇到再说。

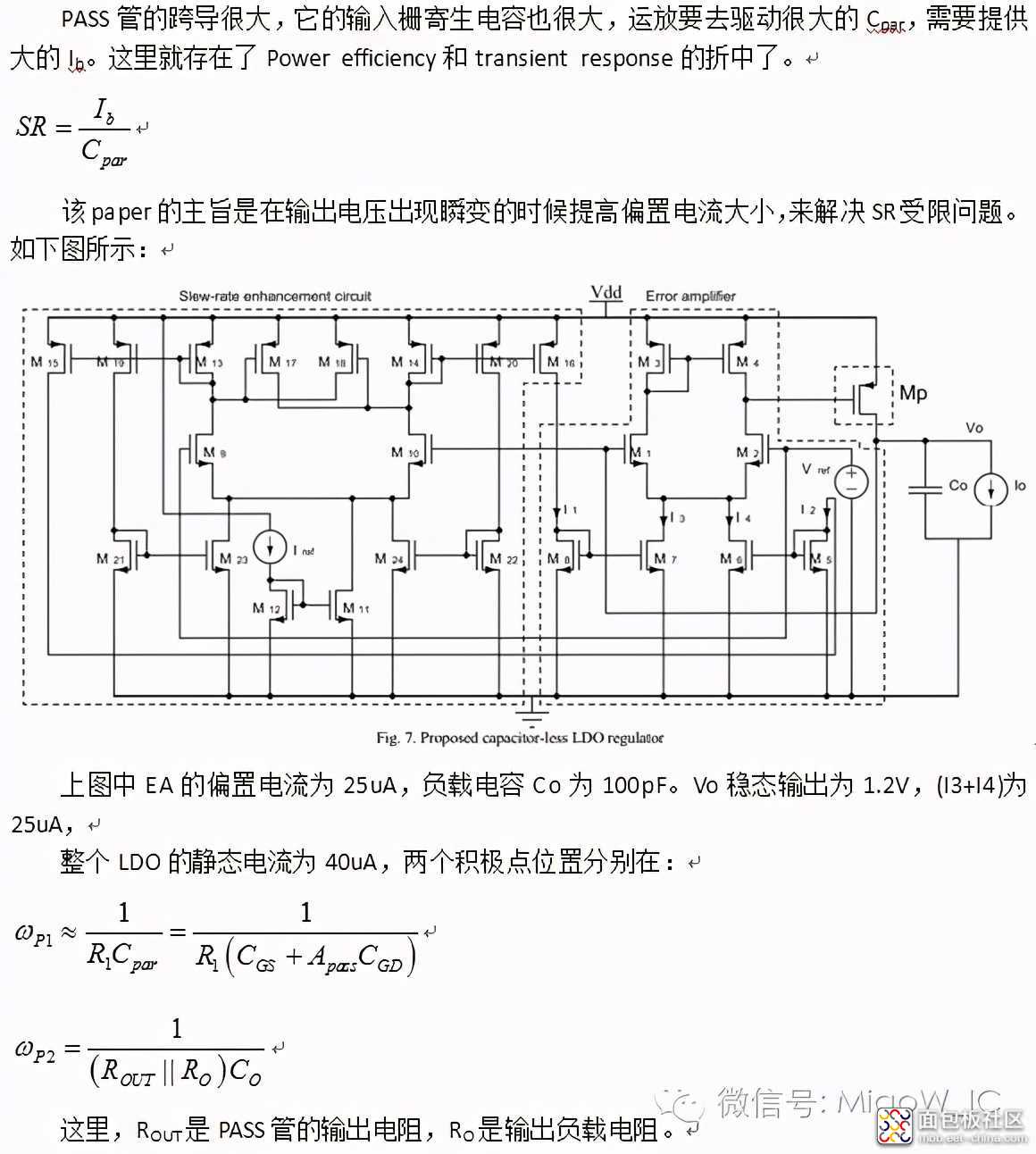

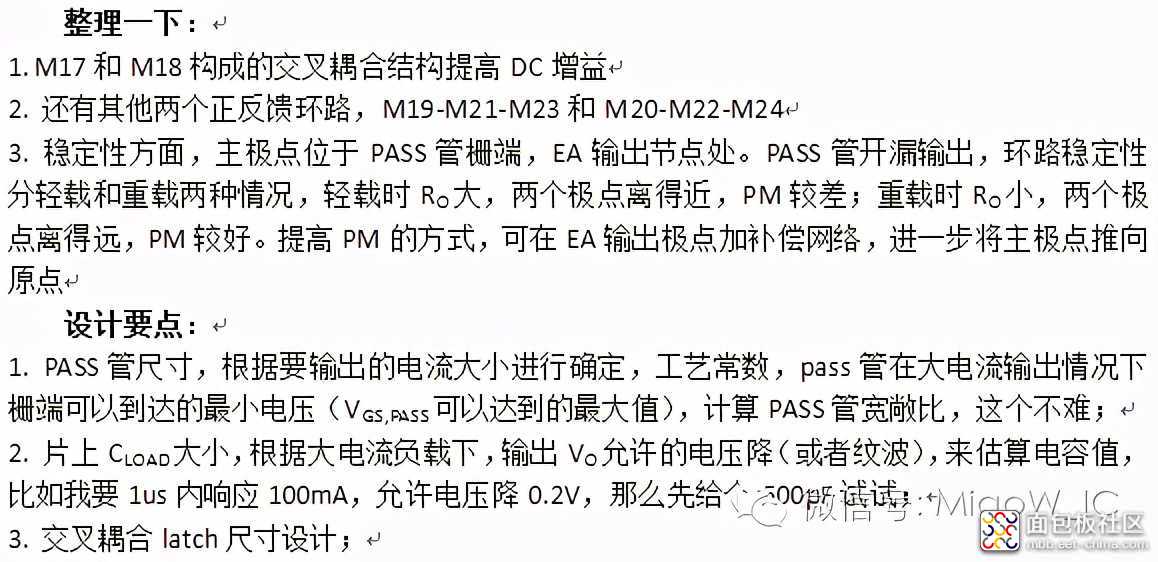

3是大信号设计参数,也有无数篇paper去讲如何提高SRG。取决于EA的偏置(尾)电流,今天要讲的就是一种提高SR的设计电路。

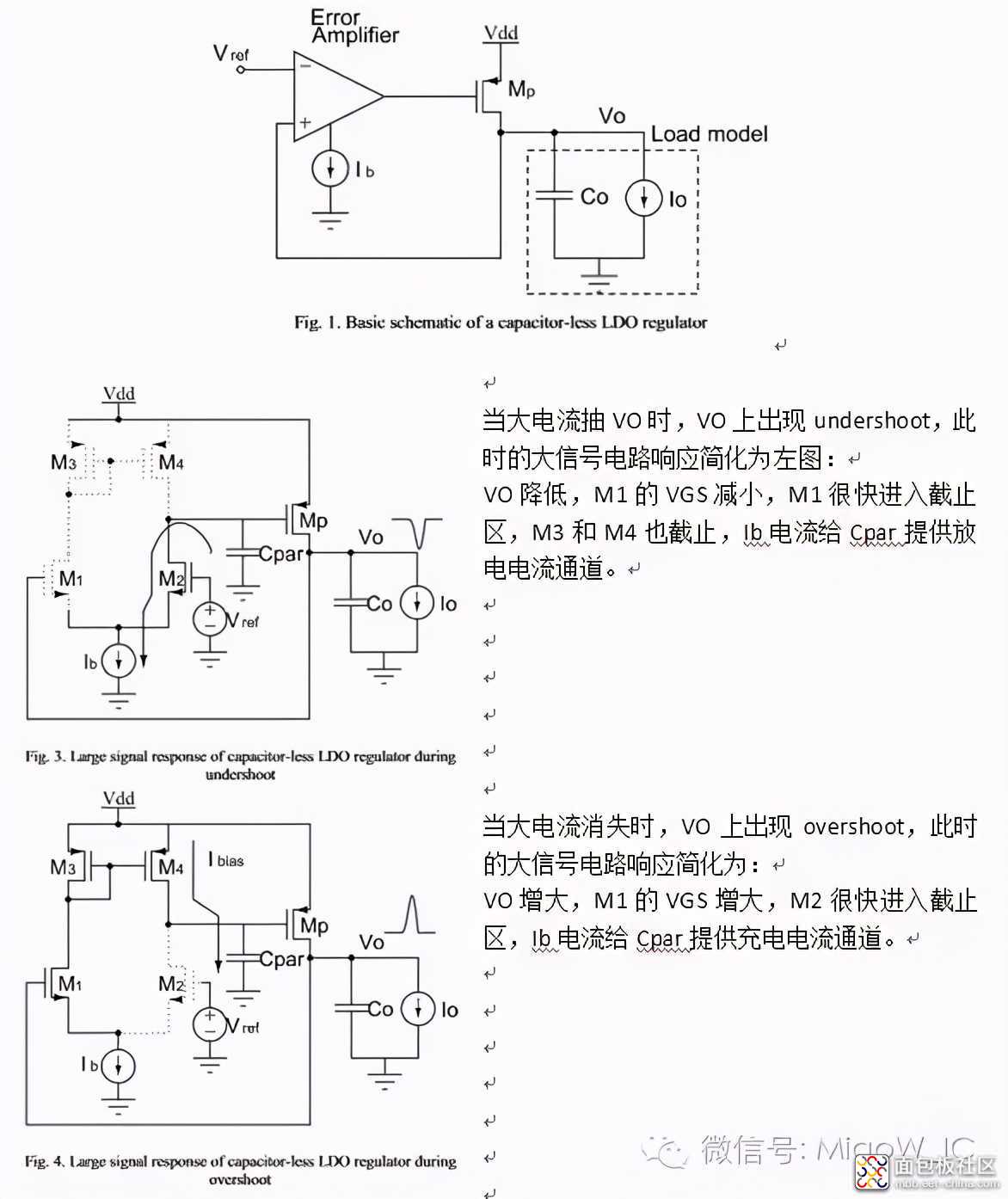

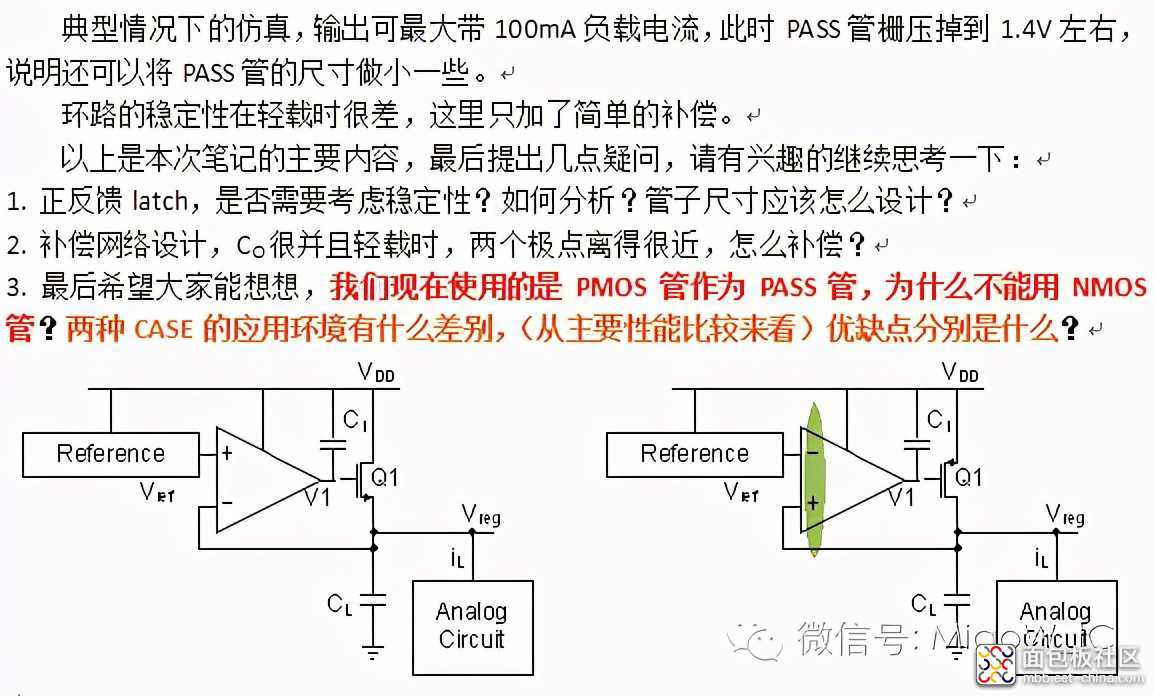

先给出cap-less LDO的基本结构:

该内容 转载自网络,仅供学习交流使用,如有侵权,请联系删除。

/2

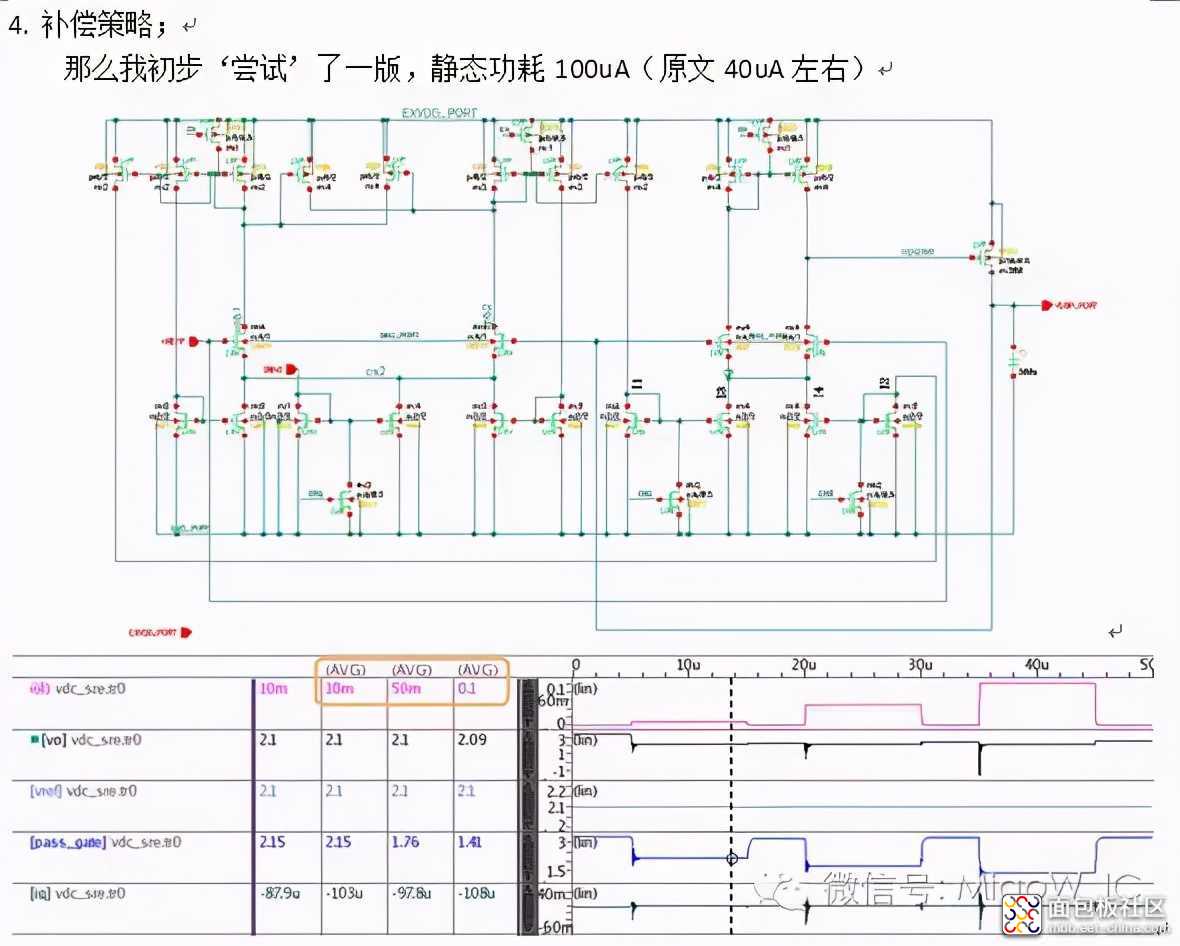

/2