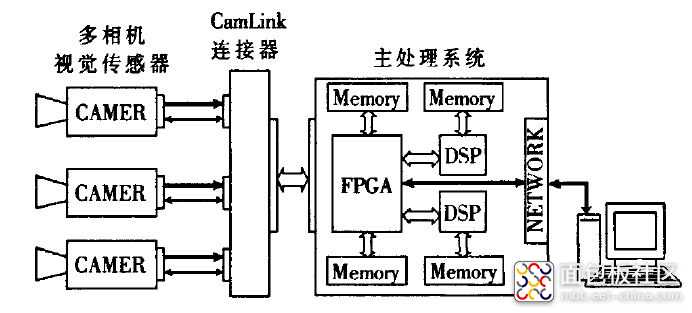

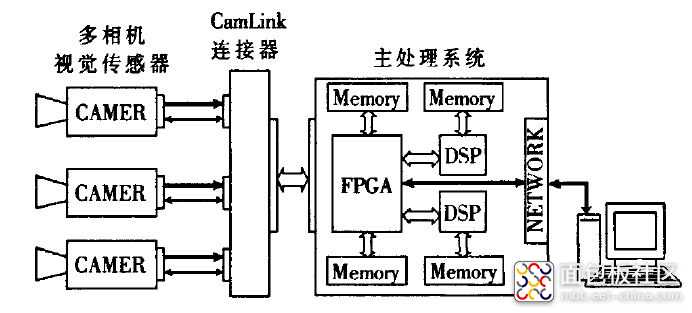

为适合高速图像采集,本系统选用CMOS传感器,CMOS的一个优点是数据读取速度快。系统由高速CMOS相机、基于CamLink技术的图像读取、FPGA+DSP的图像处理三部分构成,如下图所示。从图可以看出,该系统有两片FPGA,图像读取模块中的FPGA1负责从CMOS相机抓图和通讯控制,FPGA2则辅助两片DSP进行高速图像处理,实现同时对6个相机图像的实时处理。

逻辑控制芯片FPGA1选用XIUNX公司的XC3S1000LFG456作为视频数据采集控制芯片,该芯片是Spartan3低功耗系列的一种,具有1M个逻辑门,24个18×18乘法器及丰富的片上存储空间,足够进行视频采集的同步逻辑控制。并行计算FPGA选用XILINX公司Virtex-4系列中的XC4VFX60一FFll52,内部有4Mbit RAM,56880个逻辑门和128个XtremeDSP模块,足够进行大量高速数据处理,特别是片上18K RAM模块工作在500MHz,支持真正的双端口读写同步操作,为该芯片作为芯片间高速数据交互提供了资源。2个协处理DSP芯片为TI公司高性能C6416,拥有8个并行处理单元,工作频率为600Hz,最高处理速度可达4800兆指令/秒(MFLOPS)。

系统设计采集图像大小为1280x1024像素,最高速度可达每相机60f/s的实时采集。6路摄像头输出的数字视频信号经过FPGAl进行同步分离后,进入输入端高速数据缓冲区。系统采用两片ZBT SRAM进行轮流数据采集,当一帧图像采集完,FPGAl通知FPGA2进行数据转移,FPGA2将数据预处理后由DSP经EDMA保存到SRAM后等待进一步处理。

暂无评论,快来抢沙发吧

暂无评论,快来抢沙发吧

/1

/1