去耦电容如何理解

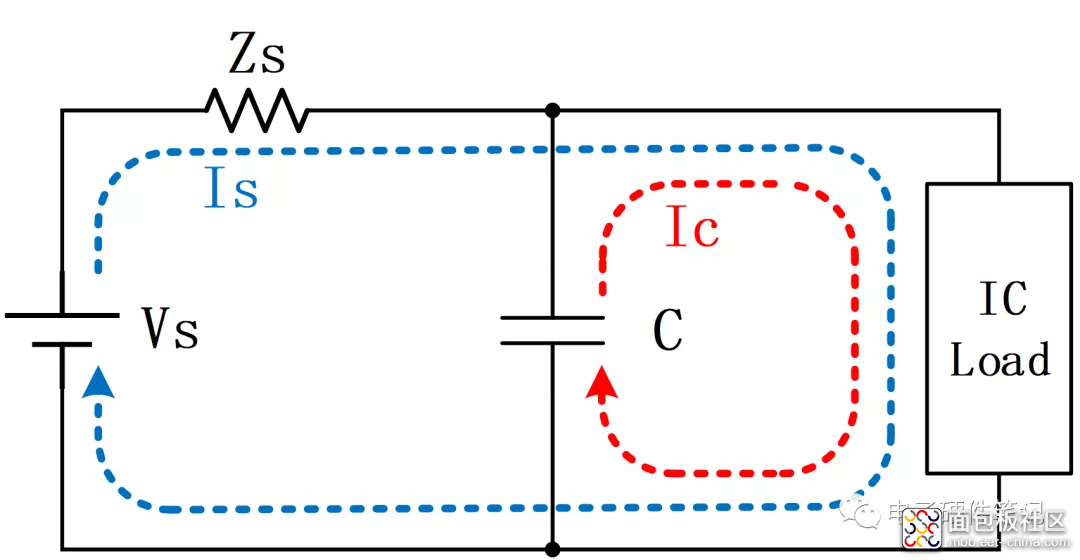

图-1:去耦电容工作原理示意图

◆ 理解1:如图-1,在芯片稳态工作下负载电流由Is提供,电容C满电荷。当负载在极短的时间内发生瞬间变化时,电源Vs无法很快地响应这个电流,芯片电压跌落,而电容能马上感应到这个变化为芯片提供电流Ic,防止电压继续跌落,从而使电压稳定。简言之,去耦电容好比一个水库,雨季储水,旱季放水。

◆ 理解2:我们说设计一个电源的本质就是设计它的内阻Zs。比如一个电源的输出电压电流为12V\1A,那么它的内阻就是12V/1A=12Ω。而电源内阻与负载成分压关系,如果内阻足够小则可以认为Vs理想电压源就全部加在了负载,电流能力强。

现将去耦电容并到电源上。由于电容具有通交特性,对于瞬态电流呈现低阻抗,因此电源并上电容后在瞬态时则阻抗更低,能提供的电流更大。简言之,去耦电容降低了电源内阻,提升了电流能力。

从这个角度理解去耦电容是比较科(有)学(用)的。如果说水库大小对应电容值,而把电容理解成一个水库,后面我们会发现电容值并不能说明一些现象。

电容特性

◆ 若将电容理解成一个水库,可以计算出这个电容值。比如负载在瞬间1ns需要让电容提供10A电流,电压为3.3V,允许的电压波动为±5%。则电容值

C=I·dt/dv=10A·1ns/(3.3V·5%)=60nF

惊喜不?1ns/10A只要60nF,很显明这并不符合实际。想想我们单片机系统随随便便都要几百nF,而且电流远远小于10A。所以说只看电容量是不够的。

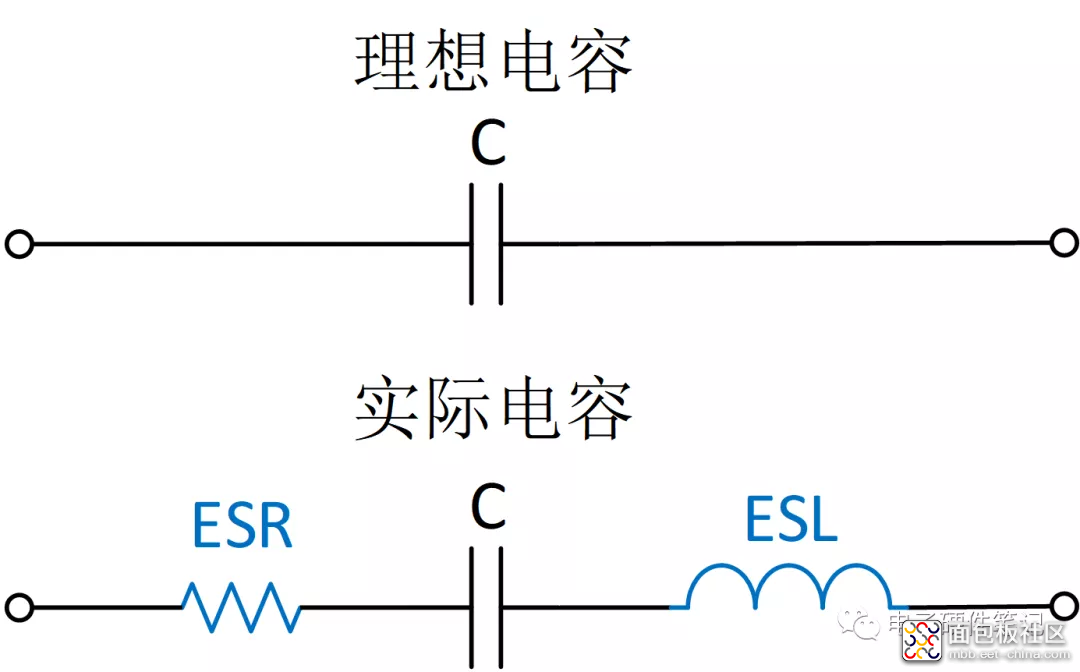

◆ 实际上这就是电容理想与现实的差距,实际的电容会包含一些寄生参数,如下图-2。

▼图-2▼

图-2:电容模型

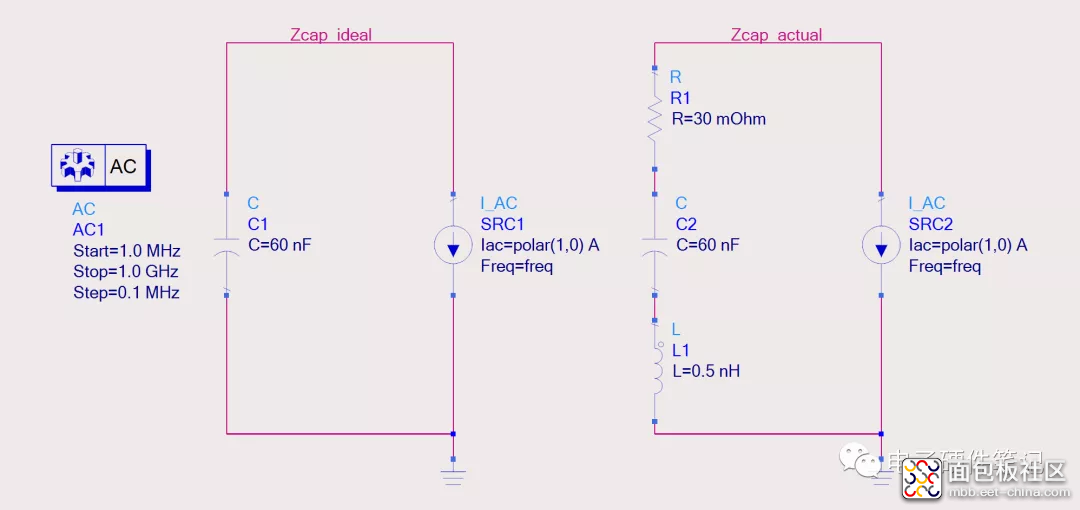

◆ 下面我们用ADS对60nF电容的两个模型进行AC扫描仿真查看它们的阻抗特性,如下图-3。采用的是直接对电流源进行频率扫描,由于所用电流源为1A,所以实际上电容上的电压值就是阻抗值。

▼图-3▼

图-3:电容模型阻抗仿真原理图

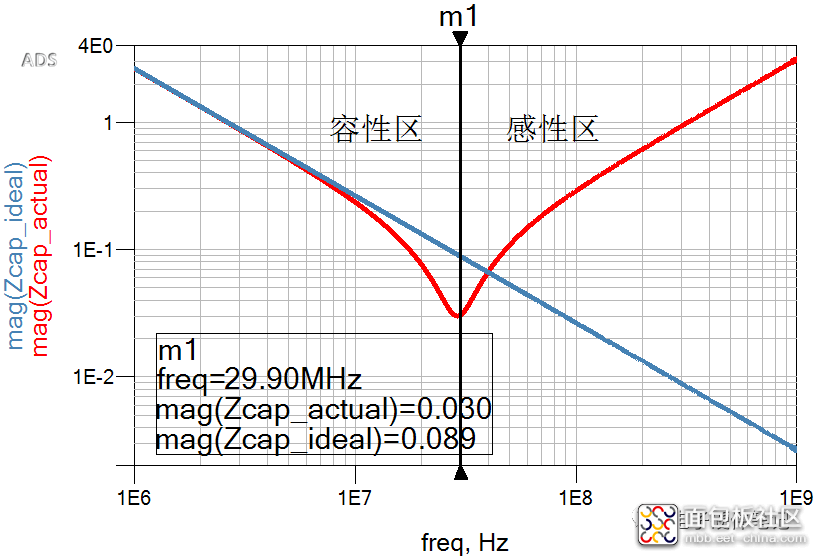

图-4:电容模型阻抗仿真曲线

◆ 如上图-4,可以看到理想电容的阻抗随着频率升高而降低,电容始终是电容。而实际电容在超过某个频率时阻抗不降反增,呈感性,电容不再是电容。

所以,以上1ns/10A选择60nF可能是不够的,因为在大于29.9M的电流频带内它的阻抗变大,电流能力会下降。为此,为了让电源系统的阻抗始终在一个合理的区间内,下面引入目标阻抗设计法,它也是当前最有效的方法。

目标阻抗设计法

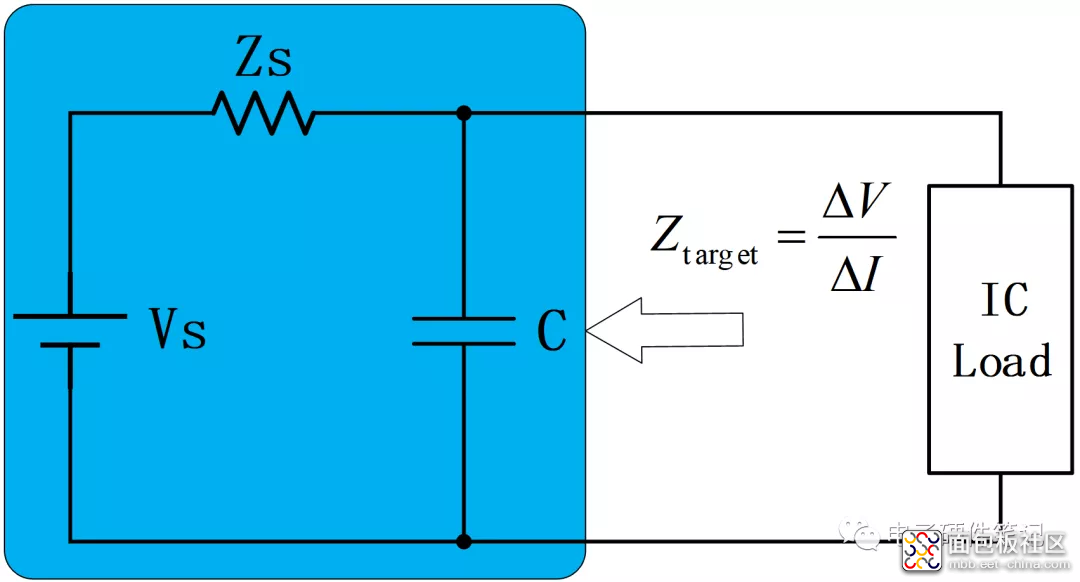

图-5:目标阻抗示意图

◆ 如上图-5,我们将从芯片向电源端看去的阻抗等效为电源系统的阻抗,如果这个阻抗越小则负载能力越强。那么这个阻抗应该多大才能满足我们的负载要求呢?先将满足我们要求的阻抗称之目标阻抗。

假设电压波动为ΔV,负载最大瞬态电流变化量为ΔI,则目标阻抗等于

Ztarget=ΔV/ΔI

◆ 总而言之,我们只要将电源系统的阻抗控制在目标阻抗以内就能够满足负载要求。

内容转载自电子硬件笔记,仅供学习交流使用,如有侵权,请联系删除。

/5

/5